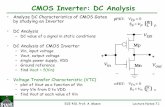

HDL Example 10-1 //-------------------- //CMOS inverter Fig. 10-22 (a) module inverter (Y,A);

description

Transcript of HDL Example 10-1 //-------------------- //CMOS inverter Fig. 10-22 (a) module inverter (Y,A);

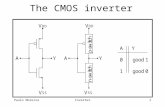

• //HDL Example 10-1• //-------------------- • //CMOS inverter Fig. 10-22 (a)• module inverter (Y,A);• input A; • output Y;• supply1 PWR;• supply0 GRD;• pmos (Y,PWR,A); //(Drain,source,gate)• nmos (Y,GRD,A); //(Drain,source,gate)• endmodule

• //HDL Example 10-2• //----------------------------- • //CMOS 2-input NAND Fig. 10-22(b)• module NAND2 (Y,A,B);• input A,B;• output Y;• supply1 PWR;• supply0 GRD;• wire W1; //terminal between two nmos• pmos (Y,PWR,A); //source connected to Vdd• pmos (Y,PWR,B); // parallel connection• nmos (Y,W1,A); // serial connction• nmos (W1,GRD,B); // source connected to ground• endmodule

• //HDL Example 10-3• //------------------- • //XOR with CMOS switchs Fig. 10-25• module SXOR (A,B,Y);• input A,B;• output Y;• wire Anot, Bnot;• //instantiate inverter • inverter v1 (Anot,A);• inverter v2 (Bnot,B);• //instantiate cmos switch• cmos (Y,B,Anot,A);

//(output,input,ncontrol,pcontrol)• cmos (Y,Bnot,A,Anot);• endmodule

• //CMOS inverter Fig. 10-22(a)• module inverter (Y,A);• input A; • output Y;• supply1 PWR;• supply0 GRD;• pmos (Y,PWR,A); //(Drain,source,gate)• nmos (Y,GRD,A); //(Drain,source,gate)• endmodule

• //Stimulus to test SXOR• module test_SXOR;• reg A,B;• wire Y;• //Instantiate SXOR• SXOR X1 (A,B,Y);• //Apply truth table• initial• begin• A=1'b0; B=1'b0;• #5 A=1'b0; B=1'b1;• #5 A=1'b1; B=1'b0;• #5 A=1'b1; B=1'b1;• end• //display results• initial• $monitor ("A =%b B= %b Y =%b",A,B,Y);• endmodule