Lecture 4 - CMOS Inverter

-

Upload

shabeeb-ali-oruvangara -

Category

Documents

-

view

45 -

download

2

description

Transcript of Lecture 4 - CMOS Inverter

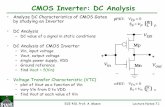

Introduction toCMOS VLSI

Design

Lecture 4: CMOS Inverter

Dr.Theerayod Wiagntong

Electronic Department, MUT

4: DC and Transient Response Slide 2CMOS VLSI Design

OutlineCMOS InverterDC ResponseLogic Levels and Noise MarginsTransient ResponseDelay Estimation

4: DC and Transient Response Slide 3CMOS VLSI Design

Activity1) If the width of a transistor increases, the current willincrease decrease not change

2) If the length of a transistor increases, the current willincrease decrease not change

3) If the supply voltage of a chip increases, the maximum transistor current will

increase decrease not change4) If the width of a transistor increases, its gate capacitance willincrease decrease not change

5) If the length of a transistor increases, its gate capacitance willincrease decrease not change

6) If the supply voltage of a chip increases, the gate capacitance of each transistor will

increase decrease not change

4: DC and Transient Response Slide 4CMOS VLSI Design

Activity1) If the width of a transistor increases, the current willincrease decrease not change

2) If the length of a transistor increases, the current willincrease decrease not change

3) If the supply voltage of a chip increases, the maximum transistor current will

increase decrease not change4) If the width of a transistor increases, its gate capacitance willincrease decrease not change

5) If the length of a transistor increases, its gate capacitance willincrease decrease not change

6) If the supply voltage of a chip increases, the gate capacitance of each transistor will

increase decrease not change

4: DC and Transient Response Slide 5CMOS VLSI Design

Static Load MOS Inverter

4: DC and Transient Response Slide 6CMOS VLSI Design

CMOS Inverter

Polysilicon

In Out

VDD

GND

PMOS 2λ

Metal 1

NMOS

OutIn

VDD

PMOS

NMOS

Contacts

N Well

4: DC and Transient Response Slide 7CMOS VLSI Design

Two Inverters

Connect in Metal

Share power and ground

Abut cells

VDD

4: DC and Transient Response Slide 8CMOS VLSI Design

CMOS Inverter as Switch

tpHL = f(Ron.CL)= 0.69 RonCL

V outVout

R n

R p

V DDV DD

V in 5 V DDV in 5 0

(a) Low-to-high (b) High-to-low

CLCL

4: DC and Transient Response Slide 9CMOS VLSI Design

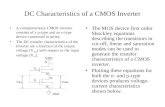

DC ResponseDC Response: Vout vs. Vin for a gateEx: Inverter– When Vin = 0 -> Vout = VDD

– When Vin = VDD -> Vout = 0– In between, Vout depends on

transistor size and current– By KCL, must settle such that

Idsn = |Idsp|– We could solve equations– But graphical solution gives more insight

Idsn

Idsp Vout

VDD

Vin

4: DC and Transient Response Slide 10CMOS VLSI Design

Transistor OperationCurrent depends on region of transistor behaviorFor what Vin and Vout are nMOS and pMOS in– Cutoff?– Linear?– Saturation?

4: DC and Transient Response Slide 11CMOS VLSI Design

nMOS Operation

Vgsn >

Vdsn >

Vgsn >

Vdsn <

Vgsn <SaturatedLinearCutoff

Idsn

Idsp Vout

VDD

Vin

4: DC and Transient Response Slide 12CMOS VLSI Design

nMOS Operation

Vgsn > Vtn

Vdsn > Vgsn – Vtn

Vgsn > Vtn

Vdsn < Vgsn – Vtn

Vgsn < Vtn

SaturatedLinearCutoff

Idsn

Idsp Vout

VDD

Vin

4: DC and Transient Response Slide 13CMOS VLSI Design

nMOS Operation

Vgsn > Vtn

Vdsn > Vgsn – Vtn

Vgsn > Vtn

Vdsn < Vgsn – Vtn

Vgsn < Vtn

SaturatedLinearCutoff

Idsn

Idsp Vout

VDD

Vin

Vgsn = Vin

Vdsn = Vout

4: DC and Transient Response Slide 14CMOS VLSI Design

nMOS Operation

Vgsn > Vtn

Vin > Vtn

Vdsn > Vgsn – Vtn

Vout > Vin - Vtn

Vgsn > Vtn

Vin > Vtn

Vdsn < Vgsn – Vtn

Vout < Vin - Vtn

Vgsn < Vtn

Vin < Vtn

SaturatedLinearCutoff

Idsn

Idsp Vout

VDD

Vin

Vgsn = Vin

Vdsn = Vout

4: DC and Transient Response Slide 15CMOS VLSI Design

pMOS Operation

Vgsp <

Vdsp <

Vgsp <

Vdsp >

Vgsp >SaturatedLinearCutoff

Idsn

Idsp Vout

VDD

Vin

4: DC and Transient Response Slide 16CMOS VLSI Design

pMOS Operation

Vgsp < Vtp

Vdsp < Vgsp – Vtp

Vgsp < Vtp

Vdsp > Vgsp – Vtp

Vgsp > Vtp

SaturatedLinearCutoff

Idsn

Idsp Vout

VDD

Vin

4: DC and Transient Response Slide 17CMOS VLSI Design

pMOS Operation

Vgsp < Vtp

Vdsp < Vgsp – Vtp

Vgsp < Vtp

Vdsp > Vgsp – Vtp

Vgsp > Vtp

SaturatedLinearCutoff

Idsn

Idsp Vout

VDD

Vin

Vgsp = Vin - VDD

Vdsp = Vout - VDD

Vtp < 0

4: DC and Transient Response Slide 18CMOS VLSI Design

pMOS Operation

Vgsp < Vtp

Vin < VDD + Vtp

Vdsp < Vgsp – Vtp

Vout < Vin - Vtp

Vgsp < Vtp

Vin < VDD + Vtp

Vdsp > Vgsp – Vtp

Vout > Vin - Vtp

Vgsp > Vtp

Vin > VDD + Vtp

SaturatedLinearCutoff

Idsn

Idsp Vout

VDD

Vin

Vgsp = Vin - VDD

Vdsp = Vout - VDD

Vtp < 0

4: DC and Transient Response Slide 19CMOS VLSI Design

I-V CharacteristicsMake pMOS is wider than nMOS such that βn = βp

Vgsn5

Vgsn4

Vgsn3

Vgsn2Vgsn1

Vgsp5

Vgsp4

Vgsp3

Vgsp2

Vgsp1VDD

-VDD

Vdsn

-Vdsp

-Idsp

Idsn

0

4: DC and Transient Response Slide 20CMOS VLSI Design

Current vs. Vout, Vin

Vin5

Vin4

Vin3

Vin2Vin1

Vin0

Vin1

Vin2

Vin3Vin4

Idsn, |Idsp|

VoutVDD

4: DC and Transient Response Slide 21CMOS VLSI Design

Load Line Analysis

Vin5

Vin4

Vin3

Vin2Vin1

Vin0

Vin1

Vin2

Vin3Vin4

Idsn, |Idsp|

VoutVDD

For a given Vin:– Plot Idsn, Idsp vs. Vout

– Vout must be where |currents| are equal in

Idsn

Idsp Vout

VDD

Vin

4: DC and Transient Response Slide 22CMOS VLSI Design

Load Line Analysis

Vin0

Vin0

Idsn, |Idsp|

VoutVDD

Vin = 0

4: DC and Transient Response Slide 23CMOS VLSI Design

Load Line Analysis

Vin1

Vin1Idsn, |Idsp|

VoutVDD

Vin = 0.2VDD

4: DC and Transient Response Slide 24CMOS VLSI Design

Load Line Analysis

Vin2

Vin2

Idsn, |Idsp|

VoutVDD

Vin = 0.4VDD

4: DC and Transient Response Slide 25CMOS VLSI Design

Load Line Analysis

Vin3

Vin3

Idsn, |Idsp|

VoutVDD

Vin = 0.6VDD

4: DC and Transient Response Slide 26CMOS VLSI Design

Load Line Analysis

Vin4

Vin4

Idsn, |Idsp|

VoutVDD

Vin = 0.8VDD

4: DC and Transient Response Slide 27CMOS VLSI Design

Load Line Analysis

Vin5Vin0

Vin1

Vin2

Vin3Vin4

Idsn, |Idsp|

VoutVDD

Vin = VDD

4: DC and Transient Response Slide 28CMOS VLSI Design

Load Line Summary

Vin5

Vin4

Vin3

Vin2Vin1

Vin0

Vin1

Vin2

Vin3Vin4

Idsn, |Idsp|

VoutVDD

4: DC and Transient Response Slide 29CMOS VLSI Design

DC Transfer CurveTranscribe points onto Vin vs. Vout plot

Vin5

Vin4

Vin3

Vin2Vin1

Vin0

Vin1

Vin2

Vin3Vin4

VoutVDD

CVout

0

Vin

VDD

VDD

A B

DE

Vtn VDD/2 VDD+Vtp

4: DC and Transient Response Slide 30CMOS VLSI Design

Operating RegionsRevisit transistor operating regions

CVout

0

Vin

VDD

VDD

A B

DE

Vtn VDD/2 VDD+VtpEDCBA

pMOSnMOSRegion

4: DC and Transient Response Slide 31CMOS VLSI Design

Operating RegionsRevisit transistor operating regions

CVout

0

Vin

VDD

VDD

A B

DE

Vtn VDD/2 VDD+VtpCutoffLinearESaturationLinearDSaturationSaturationCLinearSaturationBLinearCutoffApMOSnMOSRegion

4: DC and Transient Response Slide 32CMOS VLSI Design

Region Operation

4: DC and Transient Response Slide 33CMOS VLSI Design

Region A0 ≤ Vin ≤ VTnn-device อยูในชวง Cut-off สวน p-device อยูในชวง LinearIdsn = -Idsp = 0Vdsp = Vout – VDD, but Vdsp = 0Vout = VDD

4: DC and Transient Response Slide 34CMOS VLSI Design

Region Bกําหนดไดโดย VTn ≤ Vin ≤ VDD/2n-device อยูในชวง Saturation

p-device อยูในชวง Linear

เราสามารถแทน p-device ไดโดยมองเปนตัวความตานทาน และมอง n-device เปนแหลงจายกระแส

4: DC and Transient Response Slide 35CMOS VLSI Design

Region Cทั้ง n และ p-device อยูในสภาวะ Saturationสามารถแทนไดเปนแหลงจายกระแสสองตัวที่ตออนกุรมกนั

ถาเรากําหนดให βn = βp และ VTn = VTp จะได

4: DC and Transient Response Slide 36CMOS VLSI Design

Region Dกําหนดไดโดย VDD/2 < Vin ≤ VDD- VTpp-device อยูในชวง Saturation สวน n-device อยูในชวง Linear

4: DC and Transient Response Slide 37CMOS VLSI Design

Region Eกําหนดไดโดย Vin ≥ VDD- VTpp-device อยูในชวง Cut-off n-device อยูในชวง Linearในชวงนี้ Vgsp = Vin- VDD ซึ่งมีคามากกวาแรงดัน Threshold ของ p-device (VTp) และจะไดวา Vout = 0

4: DC and Transient Response Slide 38CMOS VLSI Design

Beta RatioIf βp / βn ≠ 1, switching point will move from VDD/2Called skewed gateOther gates: collapse into equivalent inverter

Vout

0

Vin

VDD

VDD

0.51

2

10p

n

ββ

=

0.1p

n

ββ

=

4: DC and Transient Response Slide 39CMOS VLSI Design

Transition (undefined) Region

Vm = Switching Threshold Voltage

Undefined (Indeterminate) regionVy = Vx

VOH

VOL

VIHVIL

VM

Vy

Vx

4: DC and Transient Response Slide 40CMOS VLSI Design

Noise MarginsHow much noise can a gate input see before it does not recognize the input?

IndeterminateRegion

NML

NMH

Input CharacteristicsOutput Characteristics

VOH

VDD

VOL

GND

VIH

VIL

Logical HighInput Range

Logical LowInput Range

Logical HighOutput Range

Logical LowOutput Range

4: DC and Transient Response Slide 41CMOS VLSI Design

Logic LevelsTo maximize noise margins, select logic levels at

VDD

Vin

Vout

VDD

βp/βn > 1

Vin Vout

0

4: DC and Transient Response Slide 42CMOS VLSI Design

Logic LevelsTo maximize noise margins, select logic levels at – unity gain point of DC transfer characteristic

VDD

Vin

Vout

VOH

VDD

VOL

VIL VIHVtn

Unity Gain PointsSlope = -1

VDD-|Vtp|

βp/βn > 1

Vin Vout

0

4: DC and Transient Response Slide 43CMOS VLSI Design

Delay Definitions

tpdr : rising propagation delay– From input to rising output

crossing VDD/2tpdf: falling propagation delay– From input to falling output

crossing VDD/2tpd: average propagation delay– tpd = (tpdr + tpdf)/2

(V)

0.0

0.5

1.0

1.5

2.0

t(s)0.0 200p 400p 600p 800p 1n

tpdf = 66ps tpdr = 83psVin Vout

4: DC and Transient Response Slide 44CMOS VLSI Design

Delay Definitionstr: rise time– From output crossing 0.1 VDD to 0.9 VDD

tf: fall time– From output crossing 0.9 VDD to 0.1 VDD

4: DC and Transient Response Slide 45CMOS VLSI Design

Delay EstimationWe would like to be able to easily estimate delay– Not as accurate as simulation– But easier to ask “What if?”

The step response usually looks like a 1st order RC response with a decaying exponential.Use RC delay models to estimate delay– C = total capacitance on output node– Use effective resistance R– So that tpd = RC

Characterize transistors by finding their effective R– Depends on average current as gate switches

4: DC and Transient Response Slide 46CMOS VLSI Design

RC Delay ModelsUse equivalent circuits for MOS transistors– Ideal switch + capacitance and ON resistance– Unit nMOS has resistance R, capacitance C– Unit pMOS has resistance 2R, capacitance C

Capacitance proportional to widthResistance inversely proportional to width

kgs

dg

s

d

kCkC

kCR/k

kgs

dg

s

d

kC

kC

kC

2R/k

4: DC and Transient Response Slide 47CMOS VLSI Design

Switching Characteristic

4: DC and Transient Response Slide 48CMOS VLSI Design

Fall Time

4: DC and Transient Response Slide 49CMOS VLSI Design

Rise Time

How to make rise time = fall time?

4: DC and Transient Response Slide 50CMOS VLSI Design

Effective ß

How to make rise time = fall time?

4: DC and Transient Response Slide 51CMOS VLSI Design

Switch Level RC ModelsSimple RC Model

4: DC and Transient Response Slide 52CMOS VLSI Design

Switch Level RC ModelsPenfield-Rubenstein Model (Distributed RC)

4: DC and Transient Response Slide 53CMOS VLSI Design

CMOS Gate Transistor Sizing

4: DC and Transient Response Slide 54CMOS VLSI Design

Fan-in/Fan-out

4: DC and Transient Response Slide 55CMOS VLSI Design

Inverter Chain

CL

If CL is given:- How many stages are needed to minimize the delay?- How to size the inverters?

May need some additional constraints.

In Out

4: DC and Transient Response Slide 56CMOS VLSI Design

Inverter Delay• Minimum length devices, L=0.25µm• Assume that for WP = 2WN =2W

• same pull-up and pull-down currents• approx. equal resistances RN = RP• approx. equal rise tpLH and fall tpHL delays

• Analyze as an RC network

WNunit

Nunit

unit

PunitP RR

WWR

WWRR ==⎟⎟

⎠

⎞⎜⎜⎝

⎛≈⎟⎟

⎠

⎞⎜⎜⎝

⎛=

−− 11

tpHL = (ln 2) RNCL tpLH = (ln 2) RPCLDelay (D):

2W

W

unitunit

gin CWWC 3=Load for the next stage:

4: DC and Transient Response Slide 57CMOS VLSI Design

Inverter with Load

Load (CL)

Delay

Assumptions: no load -> zero delay

CL

tp = k RWCL

RW

RW

Wunit = 1k is a constant, equal to 0.69

4: DC and Transient Response Slide 58CMOS VLSI Design

Inverter with Load

Load

Delay

Cint CL

Delay = kRW(Cint + CL) = kRWCint + kRWCL = kRW Cint(1+ CL /Cint)= Delay (Internal) + Delay (Load)

CN = Cunit

CP = 2Cunit

2W

W

4: DC and Transient Response Slide 59CMOS VLSI Design

Delay Formula

( )

( ) ( )γ/1/1

~

0int ftCCCkRt

CCRDelay

pintLWp

LintW

+=+=

+

Cint = γCgin with γ ≈ 1f = CL/Cgin - effective fanoutR = Runit/W ; Cint =WCunittp0 = 0.69RunitCunit

4: DC and Transient Response Slide 60CMOS VLSI Design

Apply to Inverter Chain

CL

In Out

1 2 N

tp = tp1 + tp2 + …+ tpN

⎟⎟⎠

⎞⎜⎜⎝

⎛+ +

jgin

jginunitunitpj C

CCRt

,

1,1~γ

LNgin

N

i jgin

jginp

N

jjpp CC

CC

ttt =⎟⎟⎠

⎞⎜⎜⎝

⎛+== +

=

+

=∑∑ 1,

1 ,

1,0

1, ,1

γ

4: DC and Transient Response Slide 61CMOS VLSI Design

Optimal Tapering for Given N

Delay equation has N - 1 unknowns, Cgin,2 – Cgin,N

Minimize the delay, find N - 1 partial derivatives

Result: Cgin,j+1/Cgin,j = Cgin,j/Cgin,j-1

Size of each stage is the geometric mean of two neighbors

- each stage has the same effective fanout (Cout/Cin)- each stage has the same delay

1,1,, +−= jginjginjgin CCC

4: DC and Transient Response Slide 62CMOS VLSI Design

Optimum Delay and Number of Stages

1,/ ginLN CCFf ==

When each stage is sized by f and has same eff. fanout f:

N Ff =

( )γ/10N

pp FNtt +=

Minimum path delay

Effective fanout of each stage:

4: DC and Transient Response Slide 63CMOS VLSI Design

Example

CL= 8 C1

In Out

C11 f f2

283 ==f

CL/C1 has to be evenly distributed across N = 3 stages:

4: DC and Transient Response Slide 64CMOS VLSI Design

Optimum Number of Stages

For a given load, CL and given input capacitance CinFind optimal sizing f

( ) ⎟⎟⎠

⎞⎜⎜⎝

⎛+=+=

fffFt

FNtt pNpp lnln

ln1/ 0/1

0γ

γγ

0ln

1lnln2

0 =−−

⋅=∂

∂

fffFt

ft pp γ

γ

For γ = 0, f = e, N = lnF

fFNCfCFC in

NinL ln

ln with ==⋅=

( )ff γ+= 1exp

4: DC and Transient Response Slide 65CMOS VLSI Design

Optimum Effective Fanout fOptimum f for given process defined by γ

( )ff γ+= 1exp

fopt = 3.6for γ=1

4: DC and Transient Response Slide 66CMOS VLSI Design

Buffer Design

1

1

1

1

8

64

64

64

64

4

2.8 8

16

22.6

N f tp

1 64 65

2 8 18

3 4 15

4 2.8 15.3

4: DC and Transient Response Slide 67CMOS VLSI Design

Power DissipationStatic – reverse bias ระหวางบริเวณ Diffusion และ Substrate

4: DC and Transient Response Slide 68CMOS VLSI Design

Power DissipationDynamic– Switching transient current

(short-circuit current)– Charging and discharging

of load capacitances (major)

4: DC and Transient Response Slide 69CMOS VLSI Design

Short Circuit Current

4: DC and Transient Response Slide 70CMOS VLSI Design

Charge-Discharge Current

*สําหรับ step input ที่ in(t) = CL(dVout/dt)

สมการที่ไดมาขางบน จะสมมุติมีการสวิทชทุก ๆ รอบไซเคิล อยางไรก็ตามโนดแตละโนดอาจจะไมเกิดการสวิทชทุกครั้ง ดังนั้นเราควรจะใสแฟกเตอร (E) เพื่อที่จะแสดงความถี่ในการสวิทชของโนดนั้นดวย ดังนั้น E(switching) เปนคาที่แสดงจํานวนครัง้ในการสวิทชตอหนึ่งไซเคิลที่เกต และเราจะไดวา

Pd = CLVDD2fpE(switching)

4: DC and Transient Response Slide 71CMOS VLSI Design

CMOS Latch-up Problem