L5 CMOS Inverter Static

Transcript of L5 CMOS Inverter Static

-

8/9/2019 L5 CMOS Inverter Static

1/20

Lecture-5-MOS-Inverter

Introduction

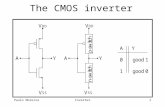

Inverter is fundamental logic gate uses single input.

Basic principles employing in design and analysis of

inverter can be directly applied on complex gates.

Therefore inverter design forms basis for digital circuits.

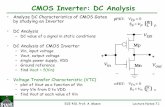

First we start with DC Characteristics.

What do you understand by DC response of the

circuit?

-

8/9/2019 L5 CMOS Inverter Static

2/20

Lecture-5-MOS-Inverter

Introduction (contd.)

The DC response is Ultra Low Frequency response of theCircuit.

When you are at a logic low or high before switching it

is a DC condition.

-

8/9/2019 L5 CMOS Inverter Static

3/20

Lecture-5-MOS-Inverter

Actual Inverter CharacteristicsGeneral Model of inverter

-

8/9/2019 L5 CMOS Inverter Static

4/20

Lecture-5-MOS-Inverter

Noise Immunity and Noise Margins

Output signal is transmitted through interconnect to next inverter.

Interconnects are prone to noise. Suppose output of 1st inverter is

perturbed, and its level is higher than VIL than it can not be correctly

predicted at output of 2nd

inverter. Thus VIL is max allowable input voltage which is low enough to ensure

1 output.

Similarly VIH is minimum allowable input voltage which is high enough

to ensure 0 output.

-

8/9/2019 L5 CMOS Inverter Static

5/20

Lecture-5-MOS-Inverter

Noise Immunity and Noise Margins Noise tolerance also called Noise Margins and denoted by NM. Two

noise margins will be defined : for low signal level as NML and highsignal level as NMH as

Justification for VIL and VIH

noise

in

outinout

noiseinoutinout

VdV

dVvfV

VVfVVfV

(!

(!!

)(

)();(

'

'

-

8/9/2019 L5 CMOS Inverter Static

6/20

-

8/9/2019 L5 CMOS Inverter Static

7/20

Lecture-5-MOS-Inverter

CMOS INVERTER

-

8/9/2019 L5 CMOS Inverter Static

8/20

Lecture-5-MOS-Inverter

Region of operation:

TOPINTOPIN

TOPGSPTOPGSPDDTOPIN

DDTOPINDDTOPIN

TOPGSPTOPGSPTOPGSP

-VVV-VVV

-VVV-VVVVVV

VVVVVV

VVVVVV

"

""

"

TOUTOU

DSPDSP

PMOS

SATURATEDLINEARCUTOFF

TOnINTOnINOUT

TOnGSnTOnGSnTOnIN

TOnINTOnIN

TOnGSnTOnGSnTOnGSn

-VVV-VVV

-VVV-VVVVV

VVVV

VVVVVV

"

"

""

""

TOU

DSnDSn

NMOS

SATURATEDLINEARCUTOFF

-

8/9/2019 L5 CMOS Inverter Static

9/20

-

8/9/2019 L5 CMOS Inverter Static

10/20

Lecture-5-MOS-Inverter

-

8/9/2019 L5 CMOS Inverter Static

11/20

Lecture-5-MOS-Inverter

-

8/9/2019 L5 CMOS Inverter Static

12/20

Lecture-5-MOS-Inverter

-

8/9/2019 L5 CMOS Inverter Static

13/20

Lecture-5-MOS-Inverter

-

8/9/2019 L5 CMOS Inverter Static

14/20

Lecture-5-MOS-Inverter

-

8/9/2019 L5 CMOS Inverter Static

15/20

Lecture-5-MOS-Inverter

-

8/9/2019 L5 CMOS Inverter Static

16/20

Lecture-5-MOS-Inverter

-

8/9/2019 L5 CMOS Inverter Static

17/20

Lecture-5-MOS-Inverter

-

8/9/2019 L5 CMOS Inverter Static

18/20

Lecture-5-MOS-Inverter

If KR = 1 Then

Ideal Logic threshold

value.

-

8/9/2019 L5 CMOS Inverter Static

19/20

Lecture-5-MOS-Inverter

-

8/9/2019 L5 CMOS Inverter Static

20/20

Lecture-5-MOS-Inverter

Next Topic

MOS Inverter : Dynamic Characteristics