CMOS inverter _dynamic characteristics

-

Upload

senthilkumar-subramani -

Category

Documents

-

view

510 -

download

1

Transcript of CMOS inverter _dynamic characteristics

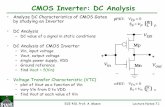

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design PerspectiveThe Digital CMOS Inverter

Dynamic Characteristics

Anurup Mitra

BITS Pilani

April 2007

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Charging and Discharging

The delay of the CMOS inverter is a performance metric forhow fast the circuit is. This delay is dependent upon the RCcharging or discharging of the load capacitor by the pMOSor nMOS devices respectively and provides a quantitativefeel for the time that is taken by the output of the inverterto completely respond to a change at its input.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Output Waveforms

The output waveform shows a distinct RC charging anddischarging phase.

The green waveform indicates the short circuit current thatflows between supply and ground each time the inverterswitches. This is to be expected as the inverter passesthrough the analog region during those times.

It can be intuitively inferred from these waveforms why thedynamic power dissipation of digital circuits is usuallyconsidered. Also, it can be noticed why this power is directlyproportional to the frequency of operation.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Output Waveforms

The output waveform shows a distinct RC charging anddischarging phase.

The green waveform indicates the short circuit current thatflows between supply and ground each time the inverterswitches. This is to be expected as the inverter passesthrough the analog region during those times.

It can be intuitively inferred from these waveforms why thedynamic power dissipation of digital circuits is usuallyconsidered. Also, it can be noticed why this power is directlyproportional to the frequency of operation.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Output Waveforms

The output waveform shows a distinct RC charging anddischarging phase.

The green waveform indicates the short circuit current thatflows between supply and ground each time the inverterswitches. This is to be expected as the inverter passesthrough the analog region during those times.

It can be intuitively inferred from these waveforms why thedynamic power dissipation of digital circuits is usuallyconsidered. Also, it can be noticed why this power is directlyproportional to the frequency of operation.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Simulation Results

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Capacitance Estimation

Several (even non-linear) capacitances contribute to the loadcapacitance of the inverter. To simplify the calculation ofthe delay incurred, the capacitances need to be linearisedand lumped together at the output.

The most fundamental delay in digital circuits is the unitdelay where an inverter is loaded by a identical inverter andthe propagation delay calculated. This delay is constant forany given technology.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Capacitance Estimation

Several (even non-linear) capacitances contribute to the loadcapacitance of the inverter. To simplify the calculation ofthe delay incurred, the capacitances need to be linearisedand lumped together at the output.

The most fundamental delay in digital circuits is the unitdelay where an inverter is loaded by a identical inverter andthe propagation delay calculated. This delay is constant forany given technology.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Resistance Estimation

As the output of an inverter swings from HIGH to LOW orvice versa, the nMOS and the pMOS devices (respectively)might travel through various regions of operation, namelylinear, saturation and velocity saturation.

Each of these regions exhibit a different ON resistance forthe MOS device. A decent approximation to the associatedReq can be got by averaging the resistances that the devicepasses through during the output swing.

Req =1

V 1− V 2

∫ V 1

V 2

V

ID(1 + λV )dV

where ID is chosen according to the region of operation.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Resistance Estimation

As the output of an inverter swings from HIGH to LOW orvice versa, the nMOS and the pMOS devices (respectively)might travel through various regions of operation, namelylinear, saturation and velocity saturation.

Each of these regions exhibit a different ON resistance forthe MOS device. A decent approximation to the associatedReq can be got by averaging the resistances that the devicepasses through during the output swing.

Req =1

V 1− V 2

∫ V 1

V 2

V

ID(1 + λV )dV

where ID is chosen according to the region of operation.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Resistance Estimation

As the output of an inverter swings from HIGH to LOW orvice versa, the nMOS and the pMOS devices (respectively)might travel through various regions of operation, namelylinear, saturation and velocity saturation.

Each of these regions exhibit a different ON resistance forthe MOS device. A decent approximation to the associatedReq can be got by averaging the resistances that the devicepasses through during the output swing.

Req =1

V 1− V 2

∫ V 1

V 2

V

ID(1 + λV )dV

where ID is chosen according to the region of operation.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Formal Definitions

The following are some formal definitions of temporalparameters of digital circuits. All percentages are of thesteady state values.

tr Rise Time : Time taken to rise from 10% to90%

tf Fall Time : Time taken to fall from 90% to10%

trf Edge Rate : (tr + tf )/2

tpHL H-to-L propagation delay : Time taken to fallfrom VOH to 50%

tpLH L-to-H propagation delay : Time taken to risefrom 50% to VOL

tp Propagation Delay : (tpHL + tpLH)/2

tcd Contamination Delay : Minimum time from theinput crossing 50% to the output crossing 50%

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Formal Definitions

The following are some formal definitions of temporalparameters of digital circuits. All percentages are of thesteady state values.

tr Rise Time : Time taken to rise from 10% to90%

tf Fall Time : Time taken to fall from 90% to10%

trf Edge Rate : (tr + tf )/2

tpHL H-to-L propagation delay : Time taken to fallfrom VOH to 50%

tpLH L-to-H propagation delay : Time taken to risefrom 50% to VOL

tp Propagation Delay : (tpHL + tpLH)/2

tcd Contamination Delay : Minimum time from theinput crossing 50% to the output crossing 50%

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Formal Definitions

The following are some formal definitions of temporalparameters of digital circuits. All percentages are of thesteady state values.

tr Rise Time : Time taken to rise from 10% to90%

tf Fall Time : Time taken to fall from 90% to10%

trf Edge Rate : (tr + tf )/2

tpHL H-to-L propagation delay : Time taken to fallfrom VOH to 50%

tpLH L-to-H propagation delay : Time taken to risefrom 50% to VOL

tp Propagation Delay : (tpHL + tpLH)/2

tcd Contamination Delay : Minimum time from theinput crossing 50% to the output crossing 50%

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Formal Definitions

The following are some formal definitions of temporalparameters of digital circuits. All percentages are of thesteady state values.

tr Rise Time : Time taken to rise from 10% to90%

tf Fall Time : Time taken to fall from 90% to10%

trf Edge Rate : (tr + tf )/2

tpHL H-to-L propagation delay : Time taken to fallfrom VOH to 50%

tpLH L-to-H propagation delay : Time taken to risefrom 50% to VOL

tp Propagation Delay : (tpHL + tpLH)/2

tcd Contamination Delay : Minimum time from theinput crossing 50% to the output crossing 50%

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Formal Definitions

The following are some formal definitions of temporalparameters of digital circuits. All percentages are of thesteady state values.

tr Rise Time : Time taken to rise from 10% to90%

tf Fall Time : Time taken to fall from 90% to10%

trf Edge Rate : (tr + tf )/2

tpHL H-to-L propagation delay : Time taken to fallfrom VOH to 50%

tpLH L-to-H propagation delay : Time taken to risefrom 50% to VOL

tp Propagation Delay : (tpHL + tpLH)/2

tcd Contamination Delay : Minimum time from theinput crossing 50% to the output crossing 50%

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Formal Definitions

The following are some formal definitions of temporalparameters of digital circuits. All percentages are of thesteady state values.

tr Rise Time : Time taken to rise from 10% to90%

tf Fall Time : Time taken to fall from 90% to10%

trf Edge Rate : (tr + tf )/2

tpHL H-to-L propagation delay : Time taken to fallfrom VOH to 50%

tpLH L-to-H propagation delay : Time taken to risefrom 50% to VOL

tp Propagation Delay : (tpHL + tpLH)/2

tcd Contamination Delay : Minimum time from theinput crossing 50% to the output crossing 50%

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Formal Definitions

The following are some formal definitions of temporalparameters of digital circuits. All percentages are of thesteady state values.

tr Rise Time : Time taken to rise from 10% to90%

tf Fall Time : Time taken to fall from 90% to10%

trf Edge Rate : (tr + tf )/2

tpHL H-to-L propagation delay : Time taken to fallfrom VOH to 50%

tpLH L-to-H propagation delay : Time taken to risefrom 50% to VOL

tp Propagation Delay : (tpHL + tpLH)/2

tcd Contamination Delay : Minimum time from theinput crossing 50% to the output crossing 50%

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Graphical Depiction

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Delay Estimation...

Now that we can estimate the capacitance and resistanceassociated with the charging/discharing of the output of aninverter, we can also estimate any of the defined delays byviewing the output as a first-order RC network.

Hence, the rise and fall times are estimated as follows:

tpHL = 0.69ReqnCeq

tpLH = 0.69ReqpCeq

giving us

tp = 0.69

(Reqn + Reqp

2

)Ceq

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Delay Estimation...

Now that we can estimate the capacitance and resistanceassociated with the charging/discharing of the output of aninverter, we can also estimate any of the defined delays byviewing the output as a first-order RC network.

Hence, the rise and fall times are estimated as follows:

tpHL = 0.69ReqnCeq

tpLH = 0.69ReqpCeq

giving us

tp = 0.69

(Reqn + Reqp

2

)Ceq

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

...Contd.

Assuming velocity saturation, the Req of an MOS device isgiven as

Req =1

0.5VDD

∫ VDD

0.5VDD

VdV

ID(1 + λV )≈ 3

4

VDD

IDSAT

(1− 7

9λVDD

)where

IDSAT = µCoxW

L

(VDD − Vt)VDSAT −

V 2DSAT

2

Usually, a normalised Req is provided as a technologyparameter.

A similar technology parameter can be calculated for tr andtf as well.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

...Contd.

Assuming velocity saturation, the Req of an MOS device isgiven as

Req =1

0.5VDD

∫ VDD

0.5VDD

VdV

ID(1 + λV )≈ 3

4

VDD

IDSAT

(1− 7

9λVDD

)where

IDSAT = µCoxW

L

(VDD − Vt)VDSAT −

V 2DSAT

2

Usually, a normalised Req is provided as a technologyparameter.

A similar technology parameter can be calculated for tr andtf as well.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

...Contd.

Assuming velocity saturation, the Req of an MOS device isgiven as

Req =1

0.5VDD

∫ VDD

0.5VDD

VdV

ID(1 + λV )≈ 3

4

VDD

IDSAT

(1− 7

9λVDD

)where

IDSAT = µCoxW

L

(VDD − Vt)VDSAT −

V 2DSAT

2

Usually, a normalised Req is provided as a technologyparameter.

A similar technology parameter can be calculated for tr andtf as well.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Example

Calculate the propagation delay of a CMOS inverter in0.18µm technology. The Req’s of the nMOS and the pMOSare 7 kΩ and 20 kΩ respectively. Their aspect ratios are 1and 3 respectively and the load cap is 5fF.

The charge down is determined by the nMOS device. Thus

tpHL = 0.69×(

7kΩ

1

)× 5fF = 24.2ps

The charge up is determined by the pMOS device. Hence

tpLH = 0.69×(

20kΩ

3

)× 5fF = 23ps

Therefore the total propagation delay is given by 23.6 ps.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Example

Calculate the propagation delay of a CMOS inverter in0.18µm technology. The Req’s of the nMOS and the pMOSare 7 kΩ and 20 kΩ respectively. Their aspect ratios are 1and 3 respectively and the load cap is 5fF.

The charge down is determined by the nMOS device. Thus

tpHL = 0.69×(

7kΩ

1

)× 5fF = 24.2ps

The charge up is determined by the pMOS device. Hence

tpLH = 0.69×(

20kΩ

3

)× 5fF = 23ps

Therefore the total propagation delay is given by 23.6 ps.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Example

Calculate the propagation delay of a CMOS inverter in0.18µm technology. The Req’s of the nMOS and the pMOSare 7 kΩ and 20 kΩ respectively. Their aspect ratios are 1and 3 respectively and the load cap is 5fF.

The charge down is determined by the nMOS device. Thus

tpHL = 0.69×(

7kΩ

1

)× 5fF = 24.2ps

The charge up is determined by the pMOS device. Hence

tpLH = 0.69×(

20kΩ

3

)× 5fF = 23ps

Therefore the total propagation delay is given by 23.6 ps.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Example

Calculate the propagation delay of a CMOS inverter in0.18µm technology. The Req’s of the nMOS and the pMOSare 7 kΩ and 20 kΩ respectively. Their aspect ratios are 1and 3 respectively and the load cap is 5fF.

The charge down is determined by the nMOS device. Thus

tpHL = 0.69×(

7kΩ

1

)× 5fF = 24.2ps

The charge up is determined by the pMOS device. Hence

tpLH = 0.69×(

20kΩ

3

)× 5fF = 23ps

Therefore the total propagation delay is given by 23.6 ps.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

An Important Observation

It might be tempting to think that the easiest way todecrease the propagation delay of any stage of a digitalsystem (and thus increase its speed) is to scale up the(W/L)’s of that particular stage.

However, this is not straightforward. It should be noted thata digital system consists of a cascade of inverters orequivalent inverters. If the j-th stage out of N cascadedstages is chosen, increasing the (W/L) of that stage willincrease the charging and discharging time of the (j + 1)-thstage, but it will also increase the load presented to the(j − 1)-th stage. This might result in an overall increase inthe system delay.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

An Important Observation

It might be tempting to think that the easiest way todecrease the propagation delay of any stage of a digitalsystem (and thus increase its speed) is to scale up the(W/L)’s of that particular stage.

However, this is not straightforward. It should be noted thata digital system consists of a cascade of inverters orequivalent inverters. If the j-th stage out of N cascadedstages is chosen, increasing the (W/L) of that stage willincrease the charging and discharging time of the (j + 1)-thstage, but it will also increase the load presented to the(j − 1)-th stage. This might result in an overall increase inthe system delay.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

A Word on Capacitive Loading...

All the components of the inverter load cap discussed so farcan be split into two broad categories - the intrinsic loadCint (diffusion and overlap caps), and the extrinsic load Cext

(wire and connecting gate caps).

The propagation delay canbe expressed as

tp = 0.69Req(Cint + Cext) = tp0

(1 +

Cext

Cint

)Here tp0 represents the delay of the inverter loaded only byits intrinsic capacitance and is hence called the the intrinsicor unloaded delay.

It can be empirically established thatCint = γCg (= CoxWnLn + CoxWpLp) and γ is a correctionfactor very close to unity.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

A Word on Capacitive Loading...

All the components of the inverter load cap discussed so farcan be split into two broad categories - the intrinsic loadCint (diffusion and overlap caps), and the extrinsic load Cext

(wire and connecting gate caps). The propagation delay canbe expressed as

tp = 0.69Req(Cint + Cext) = tp0

(1 +

Cext

Cint

)

Here tp0 represents the delay of the inverter loaded only byits intrinsic capacitance and is hence called the the intrinsicor unloaded delay.

It can be empirically established thatCint = γCg (= CoxWnLn + CoxWpLp) and γ is a correctionfactor very close to unity.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

A Word on Capacitive Loading...

All the components of the inverter load cap discussed so farcan be split into two broad categories - the intrinsic loadCint (diffusion and overlap caps), and the extrinsic load Cext

(wire and connecting gate caps). The propagation delay canbe expressed as

tp = 0.69Req(Cint + Cext) = tp0

(1 +

Cext

Cint

)Here tp0 represents the delay of the inverter loaded only byits intrinsic capacitance and is hence called the the intrinsicor unloaded delay.

It can be empirically established thatCint = γCg (= CoxWnLn + CoxWpLp) and γ is a correctionfactor very close to unity.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

A Word on Capacitive Loading...

All the components of the inverter load cap discussed so farcan be split into two broad categories - the intrinsic loadCint (diffusion and overlap caps), and the extrinsic load Cext

(wire and connecting gate caps). The propagation delay canbe expressed as

tp = 0.69Req(Cint + Cext) = tp0

(1 +

Cext

Cint

)Here tp0 represents the delay of the inverter loaded only byits intrinsic capacitance and is hence called the the intrinsicor unloaded delay.

It can be empirically established thatCint = γCg (= CoxWnLn + CoxWpLp) and γ is a correctionfactor very close to unity.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

...Contd.With the approximation we can now write

tp = tp0

(1 +

Cext

γCg

)= tp0

(1 +

f

γ

)

This establishes that the delay of an inverter is purely afunction of the ratio between its external load cap andits input cap. This ratio f , is termed the effective fan-out.

The fan-out of a digital inverter or equivalent inverterdenotes the number of load gates that are connected to theoutput of the driving gate. A large fan-out can deterioratethe dynamic performance of the gate because of the addedcapacitance at the output which needs to be charged ordischarged.

It should also be mentioned here that the fan-in of a gate isdefined as the number of inputs to the gate. A large fan-intends to make the construction of the gate more complexand degrades both the static and dynamic performance.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

...Contd.With the approximation we can now write

tp = tp0

(1 +

Cext

γCg

)= tp0

(1 +

f

γ

)This establishes that the delay of an inverter is purely afunction of the ratio between its external load cap andits input cap. This ratio f , is termed the effective fan-out.

The fan-out of a digital inverter or equivalent inverterdenotes the number of load gates that are connected to theoutput of the driving gate. A large fan-out can deterioratethe dynamic performance of the gate because of the addedcapacitance at the output which needs to be charged ordischarged.

It should also be mentioned here that the fan-in of a gate isdefined as the number of inputs to the gate. A large fan-intends to make the construction of the gate more complexand degrades both the static and dynamic performance.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

...Contd.With the approximation we can now write

tp = tp0

(1 +

Cext

γCg

)= tp0

(1 +

f

γ

)This establishes that the delay of an inverter is purely afunction of the ratio between its external load cap andits input cap. This ratio f , is termed the effective fan-out.

The fan-out of a digital inverter or equivalent inverterdenotes the number of load gates that are connected to theoutput of the driving gate. A large fan-out can deterioratethe dynamic performance of the gate because of the addedcapacitance at the output which needs to be charged ordischarged.

It should also be mentioned here that the fan-in of a gate isdefined as the number of inputs to the gate. A large fan-intends to make the construction of the gate more complexand degrades both the static and dynamic performance.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

...Contd.With the approximation we can now write

tp = tp0

(1 +

Cext

γCg

)= tp0

(1 +

f

γ

)This establishes that the delay of an inverter is purely afunction of the ratio between its external load cap andits input cap. This ratio f , is termed the effective fan-out.

The fan-out of a digital inverter or equivalent inverterdenotes the number of load gates that are connected to theoutput of the driving gate. A large fan-out can deterioratethe dynamic performance of the gate because of the addedcapacitance at the output which needs to be charged ordischarged.

It should also be mentioned here that the fan-in of a gate isdefined as the number of inputs to the gate. A large fan-intends to make the construction of the gate more complexand degrades both the static and dynamic performance.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Inverter Sizing...

The goal is to minimise the delay of an inverter chain whichis representative of a typical digital system. The input cap isdenoted by Cg1 and the final load cap is CL.

The delay of the j-th inverter stage is given by

tp,j = tp0

(1 +

Cg ,j+1

γCg ,j

)= tp0

(1 +

fjγ

)Hence, the total delay through the system is

tp =N∑

j=1

tp,j = tp0

N∑j=1

(1 +

Cg ,j+1

γCg ,j

)

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Inverter Sizing...

The goal is to minimise the delay of an inverter chain whichis representative of a typical digital system. The input cap isdenoted by Cg1 and the final load cap is CL.

The delay of the j-th inverter stage is given by

tp,j = tp0

(1 +

Cg ,j+1

γCg ,j

)= tp0

(1 +

fjγ

)Hence, the total delay through the system is

tp =N∑

j=1

tp,j = tp0

N∑j=1

(1 +

Cg ,j+1

γCg ,j

)

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

...Contd.

The minimum delay is found by equating N-1 partialderivatives to 0 and obtaining a set of constraints

Cg ,j+1

Cg ,j=

Cg ,j

Cg ,j−1; j = 2...N

Cg ,j =√

Cg ,j−1Cg ,j+1

The optimum size of each inverter is the geometric meanof its neighbour’s sizes.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Stage Ratio

This means that each inverter has a scale-up factor of f withrespect to the preceding stage, the same effective fan-outand hence the same delay.

Denoting the CL/Cg1 ratio by F , we have

f =N√

F

The minimum delay is achieved as

tp = Ntp0

(1 +

N√

F

γ

)F is called the effective fan-out and f , the stage ratio.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Stage Ratio

This means that each inverter has a scale-up factor of f withrespect to the preceding stage, the same effective fan-outand hence the same delay.

Denoting the CL/Cg1 ratio by F , we have

f =N√

F

The minimum delay is achieved as

tp = Ntp0

(1 +

N√

F

γ

)F is called the effective fan-out and f , the stage ratio.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Stage Ratio

This means that each inverter has a scale-up factor of f withrespect to the preceding stage, the same effective fan-outand hence the same delay.

Denoting the CL/Cg1 ratio by F , we have

f =N√

F

The minimum delay is achieved as

tp = Ntp0

(1 +

N√

F

γ

)

F is called the effective fan-out and f , the stage ratio.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Stage Ratio

This means that each inverter has a scale-up factor of f withrespect to the preceding stage, the same effective fan-outand hence the same delay.

Denoting the CL/Cg1 ratio by F , we have

f =N√

F

The minimum delay is achieved as

tp = Ntp0

(1 +

N√

F

γ

)F is called the effective fan-out and f , the stage ratio.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Optimised Number of Stages

tp = Ntp0

(1 +

N√

F

γ

)An optimum value has to be chosen for the number ofstages N.

If N is too large, Ntp0 becomes dominant and theintrinsic delay of the stages dominates. If N is too small, theeffective fan-out becomes excessively large.

Differentiating the delay expression with respect to thenumber of stages and equating to 0, we attain

γ +N√

F −N√

F lnF

N= 0

or , f = exp(1 +

γ

f

)This equation has to be solved numerically and gives anoptimum value of 4 for f .

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Optimised Number of Stages

tp = Ntp0

(1 +

N√

F

γ

)An optimum value has to be chosen for the number ofstages N. If N is too large, Ntp0 becomes dominant and theintrinsic delay of the stages dominates.

If N is too small, theeffective fan-out becomes excessively large.

Differentiating the delay expression with respect to thenumber of stages and equating to 0, we attain

γ +N√

F −N√

F lnF

N= 0

or , f = exp(1 +

γ

f

)This equation has to be solved numerically and gives anoptimum value of 4 for f .

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Optimised Number of Stages

tp = Ntp0

(1 +

N√

F

γ

)An optimum value has to be chosen for the number ofstages N. If N is too large, Ntp0 becomes dominant and theintrinsic delay of the stages dominates. If N is too small, theeffective fan-out becomes excessively large.

Differentiating the delay expression with respect to thenumber of stages and equating to 0, we attain

γ +N√

F −N√

F lnF

N= 0

or , f = exp(1 +

γ

f

)This equation has to be solved numerically and gives anoptimum value of 4 for f .

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Optimised Number of Stages

tp = Ntp0

(1 +

N√

F

γ

)An optimum value has to be chosen for the number ofstages N. If N is too large, Ntp0 becomes dominant and theintrinsic delay of the stages dominates. If N is too small, theeffective fan-out becomes excessively large.

Differentiating the delay expression with respect to thenumber of stages and equating to 0, we attain

γ +N√

F −N√

F lnF

N= 0

or , f = exp(1 +

γ

f

)

This equation has to be solved numerically and gives anoptimum value of 4 for f .

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Optimised Number of Stages

tp = Ntp0

(1 +

N√

F

γ

)An optimum value has to be chosen for the number ofstages N. If N is too large, Ntp0 becomes dominant and theintrinsic delay of the stages dominates. If N is too small, theeffective fan-out becomes excessively large.

Differentiating the delay expression with respect to thenumber of stages and equating to 0, we attain

γ +N√

F −N√

F lnF

N= 0

or , f = exp(1 +

γ

f

)This equation has to be solved numerically and gives anoptimum value of 4 for f .

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Rise and Fall Times of the Input

All expressions for delay derived so far assumes zero rise andfall times for the input signal. When the actual rise and falltimes are considered the delay expressions also get modifiedaccordingly.

For a single digital stage, the following correction is oftenused.

tpHL,actual =

√t2pHL,step +

( tr2

)2

tpLH,actual =

√t2pLH,step +

( tf2

)2

For an inverter chain topology, we use

t ip = t i

p,step + ηt i−1p,step

where η is an empirical constant around 0.25.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Rise and Fall Times of the Input

All expressions for delay derived so far assumes zero rise andfall times for the input signal. When the actual rise and falltimes are considered the delay expressions also get modifiedaccordingly.

For a single digital stage, the following correction is oftenused.

tpHL,actual =

√t2pHL,step +

( tr2

)2

tpLH,actual =

√t2pLH,step +

( tf2

)2

For an inverter chain topology, we use

t ip = t i

p,step + ηt i−1p,step

where η is an empirical constant around 0.25.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Rise and Fall Times of the Input

All expressions for delay derived so far assumes zero rise andfall times for the input signal. When the actual rise and falltimes are considered the delay expressions also get modifiedaccordingly.

For a single digital stage, the following correction is oftenused.

tpHL,actual =

√t2pHL,step +

( tr2

)2

tpLH,actual =

√t2pLH,step +

( tf2

)2

For an inverter chain topology, we use

t ip = t i

p,step + ηt i−1p,step

where η is an empirical constant around 0.25.

The Digital CMOSInverter

Anurup Mitra

Introduction

Delay Estimation

Design Perspective

Something