Lec_21 - Basic Structure of CMOS Inverter

-

Upload

api-3722592 -

Category

Documents

-

view

1.058 -

download

0

Transcript of Lec_21 - Basic Structure of CMOS Inverter

1Professor N Cheung, U.C. Berkeley

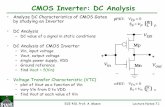

Lecture 21EE143 F05

Basic Structure of CMOS Inverter

2Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

The MOSISCMOS Process

MOSIS is a foundry service that providesstandard CMOS fabrication

P-well CMOS

3Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

Pattern mask openingFor p-well implant

Shallow implantation of boron

Diffusion drive-inTo form p-well in oxidizing ambient

Remove masking oxide

4Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

Pad oxide growth and CVD Si3N4.Pattern field oxide regions

Blanket implant of Boron for p channel stop inside p-well

Protect p-well regions with photoresist.Implant Ph to form n channel stop outside p-well regions

LOCOS Oxidation

Thermal oxidation of gate SiO2

5Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

Pattern poly-Si gates

Protect ALL n-channel transistors with photoresist.

Boron implantation to form source/drain of p-channel transistors and contacts to p-well

CVD poly-Si !!

6Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

Protect ALL p-channeltransistors with photoresist.

CVD SiO2(Low-temperature oxide)

Pattern and etch contact openings to source/drain, well contact, and substrate contact.

Arsenic implantation to form source/drain of n-channel transistors and contacts to n-substrate

7Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

Metal 1 deposition

Pattern and etch Metal 1 interconnects

CVD SiO2

8Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

Pattern and etch contact openings to Metal 1.

Metal 2 deposition.

Pattern, and etch Metal 2 interconnects.

9Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

3D view of a CMOS inverter after contact etch.

10Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

Well Engineering

P-tub

N-tub

Twin Tub

11Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

Twin Well CMOS Process Flow

12Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

C(x)

x

Conventional well (depth and profilecontrolled by diffusion drive-in)

Retrograde well (depth and profilecontrolled by implantation energy and dose)

Retrograde Well

- formed by high energy (>200keV) implantation

13Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

1) Very low thermal budget for well formation(no need for diffusion drive-in)

2) Retrograde Well is formed AFTER field oxidation⇒ small lateral diffusion and localized high conc under FOX

Conventional vs Retrograde Well

14Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

Example: Formation of Channel Stop and Retrograde Wellin a single step

Channel stop Retrograde well

15Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

Multiple Implants for Well Engineering

16Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

Basic Silicon-on-Insulator (SOI) CMOS Process Flow

17Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

SOI Process Flow (continued)

18Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

Smallest featureprintable bylithography

SiO2

CVD oxide CVD oxide

n+ n+ n+ n+

poly-Si gate

Thermal gate oxide

Oxide spacer

AngledImplantn+ pocket

NormalS/D implant

TiSi2

Self-Aligned Channel V-gate by Optical Lithography(SALVO) Process

* Sub-50nm channels

19Professor N Cheung, U.C. Berkeley

Lecture 21EE143 F05

or

SALVO Process Flow

Chang et al, IEDM 2000

See HW#9 Problem