Lecture 4 CMOS Inverter. References Section 4.2,4.3,4.6 (Hodges)

-

Upload

chester-haynes -

Category

Documents

-

view

221 -

download

0

Transcript of Lecture 4 CMOS Inverter. References Section 4.2,4.3,4.6 (Hodges)

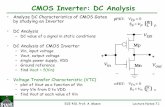

Lecture 4

CMOS Inverter

References

• Section 4.2,4.3,4.6 (Hodges)

5 Regions of Operations

I: N(off), P(lin)

As you increase Vin from 0 V to 1.8 V, you progress from region I to region V.

Current Draw of a CMOS Inverter

Ideal Voltage Transfer Characteristics of an Inverter

Large Input Range/Small Output Range →Noise Immunity.Range: the voltage interval over which the signal is either a 1 or a 0.

Practical VTC of an Inverter

Gain=ΔVout/ΔVin

Not GND

VS is defined by Vout=Vin

Effect of Input Noise on the Output

Noise Margin

Output of the Driving Stage

Input of the Receiving Stage

Unity Gain Noise Margin Definitions

NML=VIL-VOL

NMH=VOH-VIH

If Vin>VIL, the gain exceeds unity and the output begins to drop significantly.

General Analysis Methodology

Region I: N-OFF, P-TriodeRegion II: IDN(Sat)=IDP(Triode)→VIL(Cumbersome to calculate analytically)

Region III: IDN(Sat)=IDP(Sat)→VS(Switching voltage)

Region IV: IDN(Triode)=IDP(Sat) →VIH(Cumbersome to calculate analytically)

Region V: N-Triode, P-OFF

Current Consumed by a CMOS Inverter

TSMC 0.18 um Example

WN/LN=200nm/200nm WP/LP=200nm/200nm

Computation of VS

• See Derivation in the Handout• Assume: – 0.18 um TSMC CMOS– WN/LN=200nm/200nm; WP/LP=200nm/200nm

– ECNLN=4.8V; ECPLP=1.2V

• Hand Analysis using (EQ 4.15 /EQ 4.14): 0.76V• Spice: 0.748 V

VS of TSMC 0.18 um

Assume: 0.18 um TSMC CMOSWN/LN=200nm/200nm WP/LP=200nm/200nm

Adjust VS

• Knob:– χ as defined in EQ. 4.15– Increase WNLP/LNWP→ Decreased VS.

– Decrease WNLP/LNWP → Increased VS.

Increase WP to adjust VS

WN/LN=200nm/200nm WP/LP=200nm/200nm

WN/LN=200nm/200nm WP/LP=460nm/200nm

Noise Margin

• VOH=VDD

• VOL=0 V

• Determine VIL and VIH

from the -1 slope.

VIL

WN/LN=200nm/200nm WP/LP=460nm/200nm

VIH

WN/LN=200nm/200nm WP/LP=460nm/200nm

NM Calculation

• Process: TSMC 0.18 um– WN/LN=200nm/200nm; WP/LP=460nm/200nm

• VS=0.809 V

• VOH=1.8 V

• VOL=0 V

• VIL=0.66 V

• VIH=0.905V

• NML=VIL-VOL=0.66 V-0V=0.66V

• NMH=VOH-VIH=1.8 V-0.905V=0.895 V

50% Propagation Delay

Propagation Delay of CMOS Inverter

50% Propgation Dealay: 0.69 ReffCL

CMOS Inverter Calculation

tPHL

• Δt=CL ΔV/(IDS)

– ΔV=VDD/2 (from VDD to VDD/2)

– IDS

• NMOS is in Saturation (Hand Out)

• tpHL=0.69ReffnCL

• tpHL=CL ΔV/(IDSAT)

• Reffn=(VDD/2)/(0.69IDSAT)

tPLH

• Δt=CL ΔV/(IDS)

– ΔV=VDD/2 (from 0 to VDD/2)

– IDS

• PMOS is in Saturation (Hand Out)

• tpLH=0.69ReffpCL

• tpLH=CL ΔV/(IDSAT)

• Reffp=(VDD/2)/(0.69IDSAT)

Reff Comparison for 0.18 um Process

0.18 um NMOS 0.18 um PMOSReff,calc (kOhm/SQ) 11.911 28.026Reff,list (kOhm/SQ) 12.5 30

Reff: unit is Kohm/SQRN=ReffN(LN/WN)RP=ReffP(LP/WP)

Design Example• Design Constraints:

– tPHL<50 pS, tPLH<50 pS– Load Capacitor: 50 fF– Use minimum W and L to attain the specs.

• Determine W/L for PMOS and NMOS• Method:

– tPHL=tPLH=50 pS=0.7ReffCL

– Use Reffn=12.5 KOhm/SQ and Reffp=30 KOhm/SQ– Reff=1.4 Kohm– Reff=Reffn(Ln/Wn); Reff=Reffp(Lp/Wp)

– Use minimum Ln.

– Wn=1.784 um; Wp=4.284 um

tPLH

tPHL