Chap4 Field Effect Transistors

-

Upload

manh-cuong-tran -

Category

Documents

-

view

235 -

download

0

Transcript of Chap4 Field Effect Transistors

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 1/64

Chap4 - 1 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Chapter 4

Field-Effect Transistors

Microelectronic Circuit Design

Richard C. Jaeger

Travis N. Blalock

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 2/64

Chap4 - 2 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Chapter Goals

• Describe operation of MOSFETs and JFETs.

• Define FET characteristics in operation regions of cutoff, triode andsaturation.

• Develop mathematical models for i-v characteristics of MOSFETs and

JFETs.• Introduce graphical representations for output and transfer characteristic descriptions of electronic devices.

• Define and contrast characteristics of enhancement-mode anddepletion-mode FETs.

• Define symbols to represent FETs in circuit schematics.

• Investigate circuits that bias transistors into different operating regions.

• Learn basic structure and mask layout for MOS transistors and circuits.

• Explore MOS device scaling

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 3/64

Chap4 - 3 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Chapter Goals (cont.)

• Contrast 3 and 4 terminal device behavior.

• Describe sources of capacitance in MOSFETs and JFETs.

• Explore FET modeling in SPICE.

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 4/64

Chap4 - 4 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Types of Field-Effect Transistors

• MOSFET (Metal-Oxide Semiconductor Field-Effect

Transistor)

– Primary component in high-density VLSI chips such as

memories and microprocessors

• JFET (Junction Field-Effect Transistor)

– Finds application especially in analog and RF circuit

design

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 5/64

Chap4 - 5 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

MOS Capacitor Structure

• First electrode - Gate : Consists of

low-resistivity material such as

highly-doped polycrystalline

silicon, aluminum or tungsten

• Second electrode - Substrate or

Body: n- or p-type semiconductor

• Dielectric - Silicon dioxide: stablehigh-quality electrical insulator

between gate and substrate.

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 6/64

Chap4 - 6 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Substrate Conditions for Different Biases

Accumulation

V G << V TN

Depletion

V G < V TN

InversionV G > V TN

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 7/64

Chap4 - 7 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Low-frequency C-V Characteristics for MOS

Capacitor on P-type Substrate

• MOS capacitance is non-

linear function of voltage.

• Total capacitance in any

region dictated by theseparation between capacitor

plates.

• Total capacitance modeled as

series combination of fixedoxide capacitance and

voltage-dependent depletion

layer capacitance.

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 8/64

Chap4 - 8 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

NMOS Transistor: Structure

• 4 device terminals:

Gate(G), Drain(D),

Source(S) and Body(B).

• Source and drain

regions form pn

junctions with substrate.

• vSB , v DS and vGS always

positive during normal

operation.• vSB must always reverse

bias the pn junctions

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 9/64

Chap4 - 9 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

NMOS Transistor: Qualitative I-V

Behavior

• V GS << V TN : Only small leakage

current flows.

• V GS < V TN : Depletion region formed

under gate merges with source anddrain depletion regions. No current

flows between source and drain.

• V GS > V TN : Channel formed between

source and drain. If v DS

> 0, finite i D

flows from drain to source.

• i B = 0 and iG = 0.

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 10/64

Chap4 - 10 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

NMOS Transistor: Triode Region

Characteristics

Di

i D

K n

' W

LvGS

V TN

v DS

2

v DS

for vGS

V TN

v DS

0

where K n

K n

' W

L

K n

' nC

ox

" A V2

C ox

" ox

T ox

ox

oxide permittivity

F/cm

T ox

oxide thickness (cm

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 11/64

Chap4 - 11 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

NMOS Transistor: Triode Region

Characteristics (cont.)

• Output characteristicsappear to be linear.

• FET behaves like a

gate-source voltage-controlled resistor

between source anddrain with

Ron

1

K n' W

LV

GS V

TN

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 12/64

Chap4 - 12 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

MOSFET as Voltage-Controlled Resistor

Example 1: Voltage-Controlled Attenuator

vO

vS

Ron

Ron

R 1

1 K n R V

GGV

TN

vO

vS

1

1500 A

V2

2000

1.51

V

0.667

To maintain triode region operation,

0.667vS

(1.51)V or vS

0.750 V

v DS

vGS

V TN

or vO

vGG

V TN

If K n = 500A/V2, V TN = 1V, R = 2k and

V GG = 1.5V, then,

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 13/64

Chap4 - 13 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

MOSFET as Voltage-Controlled Resistor

(contd.)

Example 2: Voltage-Controlled High-Pass Filter

Voltage Transfer function,

T s V

Os

V S

s s

s o

where, cut-off frequency

o

1

RonC

K n(V

GS V

TN )

C

If K n = 500A/V2, V TN = 1V, C = 0.02F

and V GG = 1.5V, then,

f o

500 A

V2

1.51

V

2 (0.02 F) 1.99 kHz

To maintain triode region operation,

vS

V GG

V TN

0.5 V

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 14/64

Chap4 - 14 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

NMOS Transistor: Saturation Region

• If v DS increases above triode region limit,

the channel region disappears - also said to

be “pinched-off.”

• Current saturates at a constant value,

independent of v DS.

• Saturation region operation mostly used for

analog amplification.

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 15/64

Chap4 - 15 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

NMOS Transistor: Saturation Region

(contd.)

i D

K

n'

2

W

L

vGS

V TN

2

for v DS

vGS

V TN

v DSAT

vGS

V TN

is called the saturation or

pinch-off voltage

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 16/64

Chap4 - 16 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Transconductance of a MOS Device

• Transconductance relates the change in drain current to a

change in gate-source voltage

• Taking the derivative of the expression for the drain

current in the saturation region,

g m

di Ddv

GS Q pt

g m

K n' W

L(V

GS V

TN )

2 I D

V GS

V TN

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 17/64

Chap4 - 17 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Channel-Length Modulation

• As v DS increases above v DSAT , the

length of the depleted channel

beyond pinch-off point, DL,

increases and actual L decreases.

• i D increases slightly with v DS

instead of being constant.

i D

K

n

'

2

W

L

vGS

V TN

2

1 v DS

channel length modulation

parameter

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 18/64

Chap4 - 18 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Depletion-Mode MOSFETS

• NMOS transistors with

• Ion implantation process is used to form a built-in n-typechannel in the device to connect source and drain by a

resistive channel

• Non-zero drain current for vGS = 0; negative vGS required toturn device off.

V TN

0

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 19/64

Chap4 - 19 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Transfer Characteristics of MOSFETS

• Plots drain current versus gate-source voltage for a fixed

drain-source voltage

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 20/64

Chap4 - 20 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Body Effect or Substrate Sensitivity

• Non-zero vSB changes threshold

voltage, causing substrate

sensitivity modeled by

where

V TO = zero substrate bias for V TN (V)

body-effect parameter FF = surface potential parameter (V)

V TN V TO vSB 2 F 2 F

V

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 21/64

Chap4 - 21 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Enhancement-Mode PMOS Transistors:

Structure

• p-type source and drain regionsin n-type substrate.

• vGS < 0 required to create p-typeinversion layer in channelregion

• For current flow, vGS < vTP

• To maintain reverse bias onsource-substrate and drain-substrate junctions, vSB < 0 andv DB < 0

• Positive bulk-source potentialcauses V TP to become morenegative

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 22/64

Chap4 - 22 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Enhancement-Mode PMOS Transistors:

Output Characteristics

• For , transistor is

off.

• For more negative vGS , drain

current increases inmagnitude.

• PMOS is in triode region for

small values of V DS and in

saturation for larger values.

V GS

V TP

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 23/64

Chap4 - 23 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

MOSFET Circuit Symbols

• (g) and (i) are the

most commonly

used symbols in

VLSI logic design.

• MOS devices aresymmetric.

• In NMOS, n+

region at higher

voltage is the drain.

• In PMOS p+ region

at lower voltage is

the drain

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 24/64

Chap4 - 24 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Process-defining Factors

• Minimum Feature Size F : Width of smallest line or space that can

be reliably transferred to wafer surface using a given generation of lithographic manufacturing tools

• Alignment Tolerance T: Maximum misalignment that can occur

between two mask levels during fabrication

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 25/64

Chap4 - 25 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

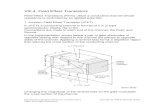

Mask Sequence for a Polysilicon-Gate

Transistor

• Mask 1: Defines active area or thin oxide region of transistor

• Mask 2: Defines polysilicon gateof transistor, aligns to mask 1

• Mask 3: Delineates the contactwindow, aligns to mask 2.

• Mask 4: Delineates the metal pattern, aligns to mask 3.

• Channel region of transistor

formed by intersection of firsttwo mask layers. Source andDrain regions formed wherever mask 1 is not covered by mask 2

n+ n+

n+n+n+ n+

(a) (b)

(c) (d)

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 26/64

Chap4 - 26 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Basic Ground Rules for Layout

• F = 2L

• T = F/2 = L Lcould be1, 0.5,

0.25 m, etc.Polysilicon Gate

AluminumInterconnection

Contact

Active Region

OxideMetal

n+

2 L 2 L 2 L1 L 1 L

12 L

L

L

L

L

L

L

B

B'

W

L

Polysilicon BelowMetal

n+

Oxide

Metal

n+

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 27/64

Chap4 - 27 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

Internal Capacitances in Electronic

Devices

• Limit high-frequency performance of the electronic device

• Limit switching speed of circuits in logic applications

• Limit frequency at which useful amplification can beobtained in amplifiers.

• MOSFET capacitances depend on operation region and are

non-linear functions of voltages at device terminals.

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 28/64

Chap4 - 28 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

NMOS Transistor Capacitances: Triode

Region

C ox” = Gate-channelcapacitance per unitarea(F/m2).

C GC = Total gate channel

capacitance.C GS = Gate-source

capacitance.

C GD = Gate-drain

capacitance.C GSO and C GDO = overlap

capacitances (F/m).

C GS

C GC

2C

GSOW C

ox" WL

2C

GSOW

C GD

C GC

2C

GSOW C

ox" WL

2C

GSOW

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 29/64

Chap4 - 29 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

NMOS Transistor Capacitances: Triode

Region (cont.)

C SB = Source-bulk capacitance.

C DB = Drain-bulk capacitance.

AS and A

D= junction bottom area

capacitance of the source and

drain regions.

P S and P D = perimeter of the

source and drain junction

regions.

C SB

C J A

S C

JSW P

S

C DB

C J A

DC

JSW P

D

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 30/64

Chap4 - 30 Jaeger/Blalock 11/15/03

Microelectronic Circuit DesignMcGraw-Hill

NMOS Transistor Capacitances:

Saturation Region

• Drain no longer connected to channel

C GS 2

3C

GC C GSO

W

C GD

C GDO

W

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 31/64

Chap4 - 31 Jaeger/Blalock 11/15/03 Microelectronic Circuit DesignMcGraw-Hill

NMOS Transistor Capacitances: Cutoff

Region

• Conducting channel

region completely

gone.

C GB = Gate-bulk

capacitance

C GBO = gate-bulk

capacitance per unit

width.

C GS

C GSO

W

C GD C

GDOW

C GB

C GBO

W

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 32/64

Chap4 - 32 Jaeger/Blalock 11/15/03 Microelectronic Circuit DesignMcGraw-Hill

SPICE Model for NMOS Transistor

Typical default values used by SPICE:

K n or K p: KP = 20 A/V2

: GAMMA= 0 : LAMBDA = 0

V TO = 1 V or V TO = -1 V

n or p UO = 600 cm2/V-s

2F F : PHI = 0.6 V

C GDO = C GSO = C GBO = C JSW = 0

T ox: TOX = 100 nm

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 33/64

Chap4 - 33 Jaeger/Blalock 11/15/03 Microelectronic Circuit DesignMcGraw-Hill

Bias Analysis Approach

• Assume a region of operation (generally the saturation

region)

• Use circuit analysis to find V GS

• Use V GS to calculate I D , and I D to find V DS

• Check validity of operation region assumptions

• Change assumptions and analyze again if required.

NOTE: An enhancement-mode device with V DS = V GS is

always in saturation

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 34/64

Chap4 - 34 Jaeger/Blalock 11/15/03 Microelectronic Circuit DesignMcGraw-Hill

Four-Resistor and Two-Resistor Biasing

• Provide excellent bias for transistors in discrete circuits.

• Stabilize bias point with respect to device parameter and

temperature variations using negative feedback.

• Use single voltage source to supply both gate-bias voltage

and drain current.

• Generally used to bias transistors in saturation region.

• Two-resistor biasing uses fewer components than four-

resistor biasing

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 35/64

Chap4 - 35 Jaeger/Blalock 11/15/03 Microelectronic Circuit DesignMcGraw-Hill

Bias Analysis: Example 1

(Four-Resistor Biasing)

Problem: Find Q-pt ( I D , V DS )

Approach: Assume operating

region, find Q-point, check to see if result is consistent with operation

region

Assumption: Transistor is saturated, I G= I B = 0

Analysis: First, simplify circuit, split

V DD into two equal-valued sources and

apply Thévenin transformation to findV EQ and R EQ for gate-bias voltage

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 36/64

Chap4 - 36 Jaeger/Blalock 11/15/03 Microelectronic Circuit DesignMcGraw-Hill

Bias Analysis: Example 1

(Four-Resistor Biasing - cont.)

V EQ

V GS

I D

RS

Since I G = 0,

V EQ

V GS

K

n R

S

2

V GS

V TN

2

4 V GS

25106

3.9104

2V

GS 1

2

V GS

2 0.05V GS 7.21 0

V GS

2.71V,2.66V

Since V GS < V TN for V GS = -2.71 V

and MOSFET will be cut-off,

V GS 2.66 V and I D 34.4 A

Also, V DD

I D

( R D

RS )V

DS

and V DS

6.08 V

V DS > V GS -V TN . Hence

saturation region assumption iscorrect.

Q-pt: (34.4 A, 6.08 V) with

V GS

= 2.66 V

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 37/64

Chap4 - 37 Jaeger/Blalock 11/15/03 Microelectronic Circuit DesignMcGraw-Hill

Bias Analysis: Example 2

(Four-Resistor Biasing)

• Estimate value of I D and use it

to find V GS and V SB

• Use V SB to calculate V TN • Find I D’ using above 2 steps

• If I D’ is not same as original I D

estimate, start again.

Analysis with body effect usingsame assumptions as in example 1:

V GS

V EQ

I D

RS

622000 I D

V SB

I D

RS

22000 I D

V TN

V TO

( V SB

2 F

2 F

)

V TN

10.5( V SB

0.6 0.6)

I D

'25106

2

V GS

V TN

2

Iterative solution can be found by

following steps:

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 38/64

Chap4 - 38 Jaeger/Blalock 11/15/03 Microelectronic Circuit DesignMcGraw-Hill

Bias Analysis: Example 2

(Four-Resistor Biasing - cont.)

The iteration sequence leads to I D = 88.0 A

V DS

V DD

I D

( R D

RS )10 40000 I

D6.48V

V DS

>V GS

-V TN

. Hence saturation region assumption is correct.

Q-pt: (88.0 A, 6.48 V)

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 39/64

Chap4 - 39 Jaeger/Blalock 11/15/03 Microelectronic Circuit DesignMcGraw-Hill

Bias Analysis: Example 3

(Two-Resistor Biasing)

Assumption: I G = I B = 0, transistor issaturated (since V DS =V GS )

Analysis:

V DS

V DD

I D

R D

V GS

V DD

K

n R

D

2V

GS V

TN

2

V GS

3.32.6104

104

2V

GS 1

2

V GS 0.769V, 2.00V

Since V GS <V TN for V GS = -0.769 V

and the MOSFET will be cut-off,

V DS >V GS -V TN . Hence saturation

region assumption is correct.

Q-pt: (130 A, 2.00 V)

V GS 2.00 V and I D 130 A

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 40/64

Chap4 - 40 Jaeger/Blalock 11/15/03 Microelectronic Circuit DesignMcGraw-Hill

Bias Analysis: Example 4 ( Biasing in

Triode Region)

Assumption: I G = I B = 0, transistor

is saturated (since V DS = V GS )

Analysis: V GS = V DD = 4 V

I D

2502

AV2

(41)2 1.13mA

V DD

I D

( R D

RS )V

DS

4 1600 I D

V DS

V DS

2.19 V

Also

But V DS < V GS -V TN . Hence,

saturation region assumption isincorrect. Try again using the triode

region equation:

4V DS

16002502

A

V2(41

V DS

2)V

DS

V DS 2.3 V and I D 1.06 mA

V DS <V GS -V TN , transistor is in triode

region

Q-pt: (1.06 mA, 2.3 V)

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 41/64

Chap4 - 41 Jaeger/Blalock 11/15/03 Microelectronic Circuit DesignMcGraw-Hill

Bias Analysis: Example 5 (Two-Resistor

biasing for PMOS Transistor)

Assumption: I G = I B = 0, transistor

is saturated (since V DS = V GS )Analysis:

V GS

(470k ) I G

V DS

0

Also

15V(220k ) I D

V DS

0

15V(220k )502 A

V2V

GS 2

2

V GS

0

V GS

0.369V, 3.45V

Since V GS = -0.369 V is less than V TP = -2V,

V GS = -3.45 V

I D = 52.5 A and V GS = -3.45 V

Hence saturation assumption is correct.

Q-pt: (52.5 A, -3.45 V)

V DS V GS V TP

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 42/64

Chap4 - 42 Jaeger/Blalock 11/15/03 Microelectronic Circuit DesignMcGraw-Hill

MOSFET as a Current Source

• Ideal current source

gives fixed output

current regardless of

voltage across it.

• MOSFET behaves as as

an ideal current source if

biased in the pinch-off

region (output current

depends on gate-sourceterminal voltage).

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 43/64

Chap4 - 43 Jaeger/Blalock 11/15/03 Microelectronic Circuit DesignMcGraw-Hill

NMOS Current Mirror

Assumption: M 1 and M 2 have identical V TN , K n’ ,

and W/L and are in

saturation.

I REF

K

n

2

W

L

V GS1

V TN 2 1 V

DS1

I O

K

n

2

W

L

V GS2

V TN 2 1 V

DS2

But V GS 2

V GS 1

and

I O

I REF

1 V DS2

1 V DS1

I REF

Thus, the output current precisely

mirrors the reference current if

V DS1 = V DS2.

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 44/64

Chap4 - 44 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

NMOS Current Mirror: Example

Given data: I REF = 50 A , V O = 12 V, V TN = 1 V , K n = 150 A/V2, =

0.0133 V-1

Determine: V GS , V DS1, I O

Analysis:

V DS 1

V GS 1

V TN

2 I

REF

K n

(1 V DS 1

)

Using trial-and-error,

V DS 1

1V 2(50 A)

150 A

V2

(1 0.0133

VV

DS 1)

Hence, V DS1 = 1.81 V. Also, V DS2 = 12 V

I O

(50 A)

1 0.0133

V(12V)

1 0.0133

V(1.81V)

56.6 A

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 45/64

Chap4 - 45 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOS Current Mirror Ratio

K n1 K n' W L

1 2 K n'

K n2

K n' W

L

2

10 K n'

I O

I REF

W / L 2

W / L 1

1 V DS2

1 V

DS1

5 I REF

1 V DS2

1 V

DS1

I O

5 I REF

Thus, the ratio between I O and I REF

can be modified by changing the

W/L ratios of the current mirror transistors (ignoring differences due

to V DS mismatch)

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 46/64

Chap4 - 46 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOS Current Mirror Output Resistance

• Output current changes with v DS due to channel length

modulation.

• Output resistance is given by

• In the current mirror, vO = v DS2

Ro iOv

O Q pt

1

iO

K

n

2

W

L

vGS2

V TN

21 v

O

Ro

I

O

1 I O

1

1 I

O

I O

1

I O

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 47/64

Chap4 - 47 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Current Mirror Layout

Two possible layouts

for a current mirror

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 48/64

Chap4 - 48 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Design of Multiple Current Mirrors:

Example

I D2

I REF

W / L 2W / L

1

50 A

I D3

I REF

W / L 3

W / L 1

125 A

I D5

I REF

W / L 5W / L

4

25 A

Choose R to set I REF = 25 A

R 10V

GSP V GSN

I REF

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 49/64

Chap4 - 49 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Design of Multiple Current Mirrors

(cont).

R101.711.4525

V

A 274k

V GSP

V TP

2 I

D

K p

1.71V and V GSN

V TN

2 I

D

K n

1.45V

R can be replaced by transistor M 6 for better

integration. We know that V GS6 = -6.84 V and I D

= 25 A and M 6 is in saturation

I D

K

p'

2W L

V

GS V

TP 2 and W L

1

13.6

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 50/64

Chap4 - 50 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOS Transistor Scaling

• Drain Current:

• Gate Capacitance and Circuit Delay:

where t is the circuit delay in a logic circuit.

K n*

n

ox

T ox

/

W /

L/

n

ox

T ox

W

L

K

n

i D*

n

ox

T ox /

W /

L/

vGS

v

TN

v

DS

2

v DS

i D

C GC * (C

ox" )*W * L*

ox

T ox

/

W /

L/

C GC

t *C GC

*DV *

i D

* C GC

DV /

i D

/

t

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 51/64

Chap4 - 51 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOS Transistor Scaling (cont.)

• Circuit and Power Densities:

• Power-Delay Product:

• Cutoff Frequency:

f T improves with square of channel length reduction

P *V DD

*i D* V

DD

i D

P

2

P *

A

* P *

W

*

L

* P / 2

(W / )( L/ ) P

WL P

A

PDP * P *t * P 2

t

PDP

3

f T

12

g mC

GC

12

n L2

V GS

V TN

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 52/64

Chap4 - 52 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOS Transistor Scaling (cont.)

• High Field Limitations: – High electric fields arise if technology is scaled down

with supply voltage constant.

– Cause reduction in mobility of the MOS transistors,

breakdown of the linear relationship between mobilityand electric field, and carrier velocity saturation.

– Ultimately results in reduced long-term reliability and breakdown of gate oxide or pn junction.

– Drain current in saturation region is linearized to

i D

C ox" W 2

(vGS

vTN

)vSAT

where, vSAT is the carrier

saturation velocity

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 53/64

Chap4 - 53 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

MOS Transistor Scaling (cont.)

• Sub-threshold Conduction:

– I D decreases exponentially for

V GS < V TN.

– Reciprocal of the slope in

mV/decade gives the turn off

rate for the MOSFET.

– V TN should be reduced if

dimensions are scaled down,

but curve in sub-thresholdregion shifts horizontally

instead of scaling with V TN .

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 54/64

Chap4 - 54 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Junction Field-Effect Transistor (JFET)

Structure

• Much lower input current andmuch higher input impedance than

the BJT.

• In triode region, JFET is a voltage-

controlled resistor,

r = resistivity of channel

L = channel length

W = channel width between pn

junction depletion regions

t = channel depth

• Inherently a depletion-mode device

• n-type semiconductor block

houses the channel region in n-

channel JFET.• Two pn junctions form the gate.

• Current enters channel at the drain

and exits at source.

RCH

r t LW

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 55/64

Chap4 - 55 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

JFET with Gate-Source Bias

• vGS = 0, gate isolated from channel.

• V P < vGS <0, W’ < W, and channel

resistance increases; gate-source

junction is reverse-biased, iG almost 0.

• vGS = V P < 0, channel region pinched-

off, channel resistance is infinite.

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 56/64

Chap4 - 56 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

JFET Channel with Drain-Source Bias

• With constant vGS , depletion regionnear drain increases with v DS .

• At v DSP = vGS - V P , channel is totally pinched-off; i D is saturated.

• JFET also suffers from channel-length modulation like MOSFET atlarger values of v DS .

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 57/64

Chap4 - 57 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

N -Channel JFET

i-v Characteristics

Transfer CharacteristicsOutput Characteristics

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 58/64

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 59/64

Chap4 - 59 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

P -Channel JFET

• Polarities of n- and p-type regions of the n-channel

JFET are reversed to get the p-channel JFET.• Channel current direction and operating bias voltages

are also reversed.

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 60/64

Chap4 - 60 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

JFET Circuit Symbols

• JFET structures are symmetric like MOSFETs.

• Source and drain determined by circuit voltages.

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 61/64

Chap4 - 61 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

JFET Capacitances and SPICE Modeling

• C GD and C GS are determined by depletion-

layer capacitances of reverse-biased pn

junctions forming gate and are bias

dependent.

• Typical default values used by SPICE: V p = -2 V

= C GD = C GD = 0

Transconductance parameter BETA

BETA = I DSS /V P 2 = 100 A/V2

Bi i JFET d D l ti M d

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 62/64

Chap4 - 62 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Biasing JFET and Depletion-Mode

MOSFET: Example

• Assumptions: JFET is pinched-off, gate-channel junction is reverse-biased,

reverse leakage current of gate, I G = 0

N -channel JFET Depletion-mode MOSFET

Bi i JFET d D l ti M d

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 63/64

Chap4 - 63 Jaeger/Blalock

11/15/03

Microelectronic Circuit Design

McGraw-Hill

Biasing JFET and Depletion-Mode

MOSFET: Example (cont.)

• Analysis:

Since I S

I D

, VGS

I D

RS

V GS

I DSS

RS

1V

GS

V P

2

5103A

1000 1

V GS

5V

2

V GS 1.91V

, 13.1V

Since V GS = -13.1 V is less than V P = -5 V, V GS = -1.91 V and, I D = I S =

1.91 mA. Also,

V DS

V DD

I D

( R D

RS )12(1.91mA)(3k ) 6.27V

V DS >V GS -V P . Hence pinch-off region assumption is correct and gate-source junction is reverse-biased by 1.91V.

Q-pt: (1.91 mA, 6.27 V)

7/27/2019 Chap4 Field Effect Transistors

http://slidepdf.com/reader/full/chap4-field-effect-transistors 64/64

End of Chapter 4