EEWeb Pulse - Issue 2, 2011

Transcript of EEWeb Pulse - Issue 2, 2011

-

8/6/2019 EEWeb Pulse - Issue 2, 2011

1/16w.eeweb.com Volume 1 - Edition

PULSE

EEWeb

IssJuly 12,

Selim nlPhotodetectors

and Nanophotonics

Electrical Engineering Commu

EEWeb

-

8/6/2019 EEWeb Pulse - Issue 2, 2011

2/16

Digi-Key is an authorized distributor for all supplier partners. New products added daily. 2011 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

www.digikey.com/techxchange

Its all about

connections.

The user-to-user forum is for everyone, fromdesign engineers to hobbyists, to discusstechnology, products, designs and more.

Join the discussions that match your interestor offer your expertise to others.

Join the discussion now at:

discussions

hobbyists

engineers

industry experts

resourceslinks

technical documentswhite papers

reference designs

application notes

community

power

microcontroller

lighting

wireless

sensor

students

http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7http://bit.ly/kDYHm7 -

8/6/2019 EEWeb Pulse - Issue 2, 2011

3/16EEWeb |Electrical Engineering Community Visit www.eeweb.com 3

TABLE OF C ONTENTS

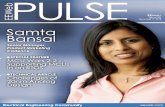

Selim nl 4ASSOCIATE DEAN FOR RESEARCH, BOSTON UNIVERSITY

Interview with Selim nl, an expert in the area of photodetectors and nanophotonics.

FPGAs Satisfying Demand for 9Higher BandwidthBY RISHI CHUGN WITH ALTERACurrent service providers are continuously looking for technology advancements to keep up

with network bandwidth demand, and seeking ways to optimize their network infrastructure.

The Ground Myth in Printed 12Circuit BoardsBY BRUCE ARCHAMBEAULT WITH IBM

RTZ - Return to Zero Comic 15

The term ground is probably the most misused and misunderstood term in EMC engineering,and in fact, in all of circuit design. This article provides insight into how you should think aboutground.

-

8/6/2019 EEWeb Pulse - Issue 2, 2011

4/16EEWeb |Electrical Engineering Community Visit www.eeweb.com 4

INTERVIEW

Selim nlNanophotonics ExpertHow did you originally get intoelectrical engineering?

Ive always said that what youdo in life is defined mostly bycoincidence. In elementary school,I always wanted to be either anelectrical engineer or an aviation

engineer, despite not even knowingwhat those professions entailed.Growing up in Turkey, I went to aspecialized high school that trainedpeople to become scientists. Abouta third of my classmates becameelectrical engineers, more than athird became medical doctors, andabout a fifth took other engineering

jobs. I chose electrical engineeringbecause I enjoyed the subjectmaterial. For two years, as a junior

and senior, I had a job at a factorybuilding electronic circuits for

handheld radios, transmitters, andreceivers. It was very satisfying tobuild things that could actually beput to use.

When I finished my undergraduatedegree, I applied to graduateprograms, and was admitted to

the Masters and PhD programs atthe University of Illinois at Urbana-Champaign. At the time, mybackground was in high-frequencydevices including electroniccircuits, electromagnetics,and microwaves. Based on myexperience with microwavedevices, my MS and PhDadvisor recruited me to work onsemiconductor devices. Althoughthis was a completely new field of

study for me, I accepted the offerand worked in his lab for six years.

I worked on a variety ofsemiconductor devices frombipolar transistors to diodes. Aftermy MS and a couple of yearsinto my PhD, I started to work on

optoelectronic devicesmostlyphotodetectors, which I becameinterested in enhancing with aninterference filter. One of themost significant coincidencesthat shaped my career washaving Katsumi Kishinoaprofessor from Tokyovisit ourlab while on sabbatical. Working

with Kishino, we developedresonant cavity enhanced (RCE)

photodetectors. The RCE conceptwas an interesting innovation andapplied to both detectors and lightemitting devices. Consequently,RCE attracted significant interestfrom researchers worldwide andbecame a very large research fieldover the next decade. Today, thereis even a Wikipedia listing.

What are your major researchareas now?

I work in a variety of applicationareas at Boston UniversitysCollege of Engineering, whichoffers a very collaborative,highly interdisciplinary, andstimulating work environment.Based at the B.U. PhotonicsCenter, my laboratory interfaces

with many research groups inengineering and the sciences,and has very strong ties to

the B.U. Medical School.

One of my major areas offocus is high-resolution opticalmicroscopy with an emphasison semiconductor circuitimaging and fault isolation. Mostrecently, I branched into doingconformational measurements of

Selim nl - Optical Characterization and Nanophotonics

-

8/6/2019 EEWeb Pulse - Issue 2, 2011

5/16EEWeb |Electrical Engineering Community Visit www.eeweb.com 5

INTERVIEW

biomolecules, biosensing, andneural stimulation. Our groupsname, Optical Characterizationand Nanophotonics (www.bu.edu/OCN), falls short of adequately

describing the breadth of ourmulti-disciplinary research.

Can you give a backgroundon each one of thoseapplications?

Let me start with our recent workon high resolution imaging ofsemiconductor circuits and devicesusing a solid immersion lens. Thetrend in the semiconductor industry

is to reduce the dimensions andincrease the number of transistorsin a chip, while increasing speedand reducing power. When

you are making these finerstructures, you have to use a veryshort wavelength of ultravioletlight in photolithography. Oncethe fabrication is completed,the top surface of the chip hasmany layers of metallic, opaque

structures, so you can no longerlook through the top surfaceto examine the semiconductorlayer and see what devicesare functioning as designed,or what is not working well.

If there is a fault, you cannotidentify it by looking from thetop surface. Instead, most ofthe technologies for isolatingfaults in semiconductor chips are

through backside imaging, thatis, through the silicon substrate.For inspection, you can no longeruse the very short wavelengthsin the UV range that are utilizedduring the manufacturing process.Instead, you have to use infrared

wavelengths because silicon is nottransparent in the visible. Basically,

you have to use a five-times-longer wavelength to measurethe things you have written withshort wavelengths. Thus, yourimaging resolution is no longer

compatible with the nanoscalestructures on the electronic circuit.

We have developed a very simpletechnique using a high-indexsilicon microlens that transformsthe back side of the substrate,

which is normally flat, into acurved surface, which allows tightfocusing of light. That way wecan achieve resolutions that are

compatible with the feature sizesthat engineers are trying to image.We pioneered this technology forcircuit and device design aboutten years ago, and have been

working on improving it ever since.

Recently we received substantialfunding from the Intelligence

Advanced Research ProjectsActivity (IARPA) totaling $5.3 millionas an interdisciplinary research

team from Boston Universityalong with an industrial partner,DCG Systems, Inc. of California.Our team will spend the next four

years applying novel imagingapproaches to pinpoint and resolvedefects on next-generation ICs.These tools, which enable rapidand accurate fault identification,are very important becausethe semiconductor industry is

very large and extremely time-sensitive; in the developmentcycle of new electronics chips,minutes are measured inmany thousands of dollars.

Are you building a prototype?

We will work indirectly withsemiconductor manufacturers

and state-of-the-art chips.Manufacturers will not reveal thespecific structure of the metallayers, materials in the chips, andother components, and chip layouts

are also closely guarded secrets,but many chip manufacturers areDCG Systems customers. Werely on our industrial partnersexpertise and connections toensure the relevance of ourtechnology development.

What size of structures areyou able to resolve withthe technology youvebeen developing?

In our current research program,the first milestone is to resolve faultisolation at 150 nanometers. Thesemiconductor technology doesnot arbitrarily reduce the size of thedevices continuously, but ratherfollows a roadmap with discreteimprovements termed nodes.

When we started to work onsolid immersion lens technology,

standard semiconductorIC technology nodes weretransitioning from 0.13 micronsto 90 nanometers. Subsequenttechnology nodes were 65 nm,45 nm, and 32 nm. The next-generation technology thats goinginto production is 22 nm. In thenext four years, we hope to achieve22-nm as well as 11-nm nodes.Our resolution requirements are150 nm for the first phase and 80nm for the next generation. It willbe very challenging to isolate faults

with that precision on the chip, butour strong team and innovativetechnology give us confidence.

-

8/6/2019 EEWeb Pulse - Issue 2, 2011

6/16EEWeb |Electrical Engineering Community Visit www.eeweb.com 6

INTERVIEW

What do you use as the imagesensor?

There are different modalities ofimaging semiconductor chips.

Obviously, you want to monitorhow well the electronic circuit isfunctioning. One of the specificanalysis techniques our industrypartner has developed is so-calledlaser voltage probing (LVP), orlaser voltage imaging (LVI). In thismodality, you have the chip workingas it would normally operate (witha clock driving the chip at a certainfrequency), and data flowing

through the chip at a differentrepetition rate. Thus, the transistorsare switching at these frequencies.If they are functioning properly, youknow that some of them have to beswitching at the data frequency andsome of them should be switchingat the clock frequency. And then

you shine a tiny spot of light on thecircuit and scan that light acrossthe chip. So, at a given time, lightis reflecting from a small area,

and the resolution is determinedby how tightly you can focus thatlight. When the transistors switch,there is a slight change in theoptical properties due to variationsin the carrier concentration.Observing the reflected light, youcan look at the changes at thoseparticular frequencies, eitherclock or data, and if you see asignal modulated at the clock

frequency, or data frequency, forexample, you can see the transistorswitching at that speed. Most ofthe signal is not modulated at thatfrequency; its a very small change(less than one part in 1,000).

Extracting that information is adetection problem, but we do use

somewhat ordinary photodetectorsfor this. The innovations aremostly in the optical systems.By scanning the focused lightacross the chip, we can form an

image. Alternatively, by focusingon a single point we can obtainthe switching characteristics as afunction of time. These are used todiagnose the circuits so you knowthat these transistors should beswitching at this frequency, and ifthey arent switching as expected,

you know that there is a fault.

We pioneered thistechnology for

circuit and devicedesign about ten

years ago, and havebeen working on

this ever since.

Another method is called photoemission microscopy. Whentransistors switch, they emit atiny bit of light. You can collectthat light, and from determiningthe timing of the emission andits location, intensity of the lightand timing of the signal, you

can diagnose the circuit. Ofcourse, that light is in very smallamounts, so you need to build

very sensitive detectors, very highcollection-efficiency optics, andhigh-resolution optics to operatethe transistor properly. You alsohave to work very closely with themanufacturers because, as the

transistor parameters change,the amount of light emitted andthe wavelength of the light is also

varying. Its a moving target, thusa very challenging project.

When we started working onthis project, we were the firstpeople who actually appliedsolid immersion techniques tosemiconductor circuit imaging.Now, all of the equipmentmanufacturers are using similartechnology. Almost invariably,everybody has to use this solidimmersion lens technology

to image chips. Its quitesatisfying to see that our hardwork is making an impact.

Can you tell us aboutyour other project onDisease Diagnostics?

The current industry techniquesfor diagnostics are based ona sandwich assay. Most of thedetection techniques rely onfluorescent labels for transduction.

A common way of detecting thepresence of a disease is to lookfor the protein biomarkers. Everypathogen has specific antigens andthe immune system will developantibodies against the infection.Typical assays use antibodiesas capture agents to detect thepresence of correspondingantigen proteins in a samplesuch as blood, urine, or saliva.

Capturing these proteins doesnot provide a sufficient signal.

A secondary antibody thatrecognizes the same antigen isused in a so-called sandwichassay, where the secondaryantibody has either an enzymeor some fluorescent moleculeslinked to it. Consequently, either

-

8/6/2019 EEWeb Pulse - Issue 2, 2011

7/16EEWeb |Electrical Engineering Community Visit www.eeweb.com 7

INTERVIEW

the solution color changes, orit fluoresces when excited byanother light source. Thats atransduction mechanism to makethe presence of small amountsof target proteins captured

visible. This kind of technologyis typically called enzyme-linkedimmunosorbent assay (ELISA). Itsa very common technology, but itdoes require a secondary antibody,and you have to refrigerate those,have a trained technician, etc.

The problem is, you cannotperform those types of tests in a

doctors office. Today, you go tothe doctor for an examination, thedoctor takes your blood, and youhave to come back three dayslater for the results. We want to

build systems where people can,around the world, be tested righton the spotat the point of care.

Are you at the point

where you will startworking on prototypes?

Label-free sensing is a recenttrend in disease diagnostics. Weall want to get rid of the secondaryantibodies, the additionalreagents, and the labels. But its achallenging project, because youhave to do the detection, not onlysensitively, but also specifically.There are a lot of steps that need

to be taken to prove these things.Using our knowledge of opticsand layered surfaces, based onour expertise in semiconductors,

we have recently been able to

build the technology for a veryinexpensive and compact system.

We can detect individual bio-particlessomething that people

werent able to do prior to our work.

Now, on a very simple surface,we can detect the presenceof individual nanoparticlesand viruses. We would liketo apply this to diagnostics,

which would allow multiplediagnoses on a single chip, withmuch more timely results.

Contact Us For Advertising Opportunities

www.eeweb.com/advertising

Electrical Engineering Community

EEWeb

http://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cx -

8/6/2019 EEWeb Pulse - Issue 2, 2011

8/16

To request a ree evaluation board go to:

Avago Technologies, an industry leader

in IGBT Gate Drive technology solutions

introduces our Next Generation series!

Based on BCDMOS technology Avago can

deliver higher peak output current, better rail-

to-rail output voltage perormance and aster

speed than previous generation products.

The increased drive and speed along with

the very high CMR (common mode rejection)

and isolation voltage will enable you to build

more efcient and reliable motor drive and

power conversion systems. In addition the

SO6 package which is up to 50% smaller than

conventional DIP packages acilitates smaller

more compact design.

www.avagotech.com/optocouplers

Avago Technologies Optocoupler Solutions

2 Times Faster, 50% Smaller,

True Rail-to-Rail Output VoltageIGBT Gate Drives

Benefts

Suitable or wide range o IGBT class or diferentmarket applications

High output peak current or ast and ecientIGBT operation

Rail-to-rail output voltage or reliable IGBToperation

Lower system power budget

Suitable or bootstrap power supply operation

Reduce dead time and improve system eciency

Prevent erroneous driving o IGBT in noisyenvironment

40%-50% smaller than DIP package or space andcost savings

Applications

IGBT/MOSFET Gate Drive

AC and Brushless

DC Motor Drives

Renewable EnergyInverters

Industrial Inverters

Switching Power Supplies

http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5http://bit.ly/jpn9V5 -

8/6/2019 EEWeb Pulse - Issue 2, 2011

9/16EEWeb |Electrical Engineering Community Visit www.eeweb.com 9

Higher BandwidthBy Rishi Chugh, Altera Corporation

FPGAs Satisfying the Demand for

Current service providers are continuouslylooking for technology advancements to keep up

with network bandwidth demand, and seekingways to optimize their network infrastructure. Theseservice providers must continue to make a profitby reducing the cost per bit while simultaneouslyextending their service offerings. High-speedEthernet, especially 100G Ethernet (100GE), offersthe key solution. As the demand for more bandwidthbecomes increasingly prevalent, service providersare looking at emerging 40-GE/100-GE standardsfor their next generation line cards (Figure 1).

A few key adopters like Data-Centers, cloudcomputing vendors, government/financial institutionsand large research labs are also driving todaysquest for ever-increasing high speed connectionand aggregation speeds. Companies like Google,Facebook, Yahoo, EBay and others have been forcedto use multiple 10GE links in parallel to meet their

bandwidth needs, however this creates problemswith port density, traffic management and powerconsumption. Currently they are desperatelyevaluating solutions and looking at both 40GE and100GE architectures. This would eventually drive100GE into the transport eco-system and this wouldbe an integral play in the edge router architecture.

Todays FPGA devices offer solutions to thebandwidth problem by providing integrated 10-Gbpstransceivers with integrated Physical Coding Sub-

layer (PCS) functions on the 28-nm process node.

Highest System Integration for Increased

Functionality in a Smaller Line Card

A key challenge in designing a 100-GbE line cardis determining the level of integration that can beachieved on a small form factor line card withoutexceeding the cost and power-consumption budget.

-

8/6/2019 EEWeb Pulse - Issue 2, 2011

10/16

-

8/6/2019 EEWeb Pulse - Issue 2, 2011

11/16EEWeb |Electrical Engineering Community Visit www.eeweb.com 11

TECHNICAL ARTICLE

performance-drive compiles, Advance Blockset,

and easy-to-use partial reconfiguration.100G system designs are gaining popularityas bandwidth requirements continue to growexponentially. An ideal FPGA solution for40-GbE/100-GbE systems that delivers integrated10 Gbps transceivers and hardened industry-standards is an IP that supports the emerging100-GbE standards and proprietary serial protocols

with line rate up to 28Gbps. It will perfectly fitthe design requirements of next generation 100-GbE system designs. Offering system designers

an accelerated time-to-market advantagewith reduced risk compared to ASSP or ASICsolutions is indeed the right path to follow.

100G Traffic Manager

100G Chip to Backplane 100G Chip-to-Chip Interlaken20-24 x 6.375 Gbps

100G Chip-to-ModuleCAUI (10 lanes x 10 Gbps)

Egress Traffic Manager

TMLinked

List

PacketBuffer LUT Statistics

Line/OpticalModule

Switch

fabric/10Gbackplane

100G MAC Packet Processing

DDR3

TCAMTCAM

QDR II/IIIRLDRAM IIQDR II/III

1 2 3

1 2 3

Stratix VFPGA

Stratix VFPGA

About the Author

As senior product marketing manager, RishiChugh is responsible for product marketingin Alteras wireline business group, as well asleading its specific product planning activities.Mr. Chugh joined Altera in March 2008, and hasover 15 years of industry experience with LSIand Artisan Components (acquired by ARM).

Figure 2: 100G Line Card using next generation FPGA devices

-

8/6/2019 EEWeb Pulse - Issue 2, 2011

12/16EEWeb |Electrical Engineering Community Visit www.eeweb.com 12

The term ground is probably themost misused and misunderstood

term in EMC engineering, andin fact, in all of circuit design.Ground is considered to be azero potential region with zeroresistance and zero impedanceat all frequencies. This is just notthe case in practical high-speeddesigns. The one thing that shouldbe remembered whenever the termground is used, is that Ground isa place where potatoes and carrotsthrive! By keeping this firmly inmind, many of the causes of EMCproblems would be eliminated.

The term ground is a fineconcept at DC voltages, but it justdoes not exist at the frequenciesrunning on todays typical boards.

All metal has some amountof resistance, and even if thatresistance was near zero ohms,the current flowing through a

conductor in a loop createsinductance. Current through that

inductance results in a voltagedrop. This means that the metalground plane/wire/bar/etc. hasa voltage drop across it, whichis in direct contradiction with theintention and definition of groundThe important point is that for

EMI/EMC we need to considerthe current, not the voltage, in our

signal paths. Since current mustalways flow in a loop back to itssource, the return current pathmust be considered as well asthe intended signal path alonga PCB trace. Any interruptionsto the return current path can

Signal Path Connector

GND

PWR

Signal Layers

Figure 1:Initial two board configuration

Myth in Printed Circuit Boards

The

Ground

By

Bruce Archambeault

Distinguished Engineer

-

8/6/2019 EEWeb Pulse - Issue 2, 2011

13/16EEWeb |Electrical Engineering Community Visit www.eeweb.com 13

TECHNICAL ARTICLE

have serious negative effects tothe EMI/EMC performance ofa PCB. A very slight deviationin return current path canresult in enough inductance to

dramatically increase emissions.

The return current path isalso very important whenconsidering mother/daughterboard configurations. Figure 1shows a simple four-layer boardexample of a mother/daughterboard configuration and a signalpath from the mother board tothe daughter card through a

connector. If we consider how thereturn current will flow from thisconfiguration, we should expectthat the return current will spreadout to include displacementcurrent through the dielectricbetween GND and PWR, as wellas local decoupling capacitors(depending on their distanceand the plane separation).

Figure 2 shows the return current

for this configuration. The addedreturn current path length resultsin additional inductance in thetotal path, resulting in a noise

voltage between the two GNDplanes (across the connector).This noise voltage will drive the

wide, thin, monopole-like antenna,resulting in increased emissions.

However, if we had simplyconsidered the return current pathand routed the signal trace sothat it was referenced to the sameplane (PWR or GND), the returncurrents are able to stay close tothe signal trace (Figure 3), andemissions are greatly reduced.

When we consider the returncurrent path, more ground is

not always the right answer! Forexample, on a recent design,there was a 144 pin connector

with many high speed signalstraveling from one board to theother. It was determined that 30pins could be used for powerand ground combined. At leastfive pins must be power so there

would not be an excessive DC

voltage drop across the connector.How many of the remaining25 pins should be ground?

In this particular design, it turnedout that about 2/3 of the total signalpins were referenced to the powerplane, and only 1/3 referencedagainst the ground plane. Thismeant that of the total 30 possiblepower/ground pins, 2/3 shouldbe power and only 1/3 should

be ground! More ground pinswas NOT the best design for thiscase. Of course, once we considerboth the power and the groundpins to be return current paths,it is obvious we should distributethem throughout the signal pins tokeep the return current deviationas small as possible (compared

to putting all the ground pins atthe ends of the connector, etc.).

When we consider the mostimportant concerns for good EMI/EMC design, the schematic is notas important as the physical layoutof the signal path and the returncurrent. Since todays high speedPCBs have many layers and are

very complex, it is difficult for anengineer to examine each criticalsignal path for a good returncurrent path. Automated EMC rulechecking tools can examine eachnet in turn, regardless of the PCBcomplexity. The key to selectingan automated rule checking tool isto make sure it can interface well

with your existing design process,it is easy to use, and it can displayrule violations in a graphical and

easy to understand manner.

The most important EMC designrules for high speed PCBs concernthe return current path. Since thereturn current will always find apath that minimizes the inductanceof that path, the return current willalways flow on the nearest plane,

Signal Path Connector

GND

PWR

Signal LayersReturn Current

Figure 2:Return current paths for initial configuration

-

8/6/2019 EEWeb Pulse - Issue 2, 2011

14/16EEWeb |Electrical Engineering Community Visit www.eeweb.com 14

TECHNICAL ARTICLE

whether it is called ground or

power or carrots. When tracesacross a split in the return plane(for example if a trace is routednext to a power layer with multiplepower islands), the return currentspath is interrupted. Changing

layers within the PCB so that thereturn current must also changeplanes will also interrupt thereturn current path. Remember,the return current must always getback to its source. It will get backto its source. The only question

is whether it will be a path that isbeneficial to you, or if it will causeproblems. So, Do you feel luckytoday? It is always best to designon purpose rather than by luck.

About the Author

Dr. Bruce Archambeault is anIBM Distinguished Engineer atIBM in Research Triangle Park,NC and co-founder of AppliedEM Technology. He receivedhis BSEE degree from theUniversity of New Hampshirein 1977 and his MSEE degreefrom Northeastern University in1981. He received his PhD fromthe University of New Hampshirein 1997. His doctoral research

was in the area of computationalelectromagnetics applied toreal-world EMC problems.

Signal Path

Connector

Decoupling

CapacitorsDisplacement

Current

GND

PWR

Signal Layers

Figure 3:Improved return current design

Join Today

www.eeweb.com/register

Electrical Engineering Community

EEWeb

http://bit.ly/jd6Wcwhttp://bit.ly/jd6Wcwhttp://bit.ly/jd6Wcwhttp://bit.ly/jd6Wcwhttp://bit.ly/jd6Wcwhttp://bit.ly/jd6Wcwhttp://bit.ly/jd6Wcwhttp://bit.ly/jd6Wcwhttp://bit.ly/jd6Wcwhttp://bit.ly/jd6Wcwhttp://bit.ly/jd6Wcwhttp://bit.ly/jd6Wcw -

8/6/2019 EEWeb Pulse - Issue 2, 2011

15/16

-

8/6/2019 EEWeb Pulse - Issue 2, 2011

16/16

RETURN TO ZERO

Contact Us For Advertising Opportunities

www.eeweb.com/advertising

Electrical Engineering Community

EEWeb

http://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cxhttp://bit.ly/l6u6Cx