EEWeb Pulse - Issue 21, 2011

description

Transcript of EEWeb Pulse - Issue 21, 2011

EEWeb

PULSE EEWeb.comIssue 21

November 22, 2011

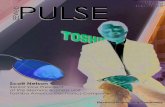

Dr. Holger Schmidt Nanoscale Optofluidics

Electrical Engineering Community

Contact Us For Advertising Opportunities

www.eeweb.com/advertising

Electrical Engineering CommunityEEWeb

Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2011 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USADigi-Key is an authorized distributor for all supplier partners. New products added daily.

www.digikey.com/techxchange

It’s all about connections.

The user-to-user forum is for everyone, from design engineers to hobbyists, to discuss technology, products, designs and more. Join the discussions that match your interest or offer your expertise to others.

Join the discussion now at:

discussions

hobbyists

engineers

industry experts

resourceslinks

technical documentswhite papers

reference designs

application notes

community

power

microcontroller

lighting

wireless

sensor

students

EEWeb | Electrical Engineering Community Visit www.eeweb.com 3

TABLE O

F CO

NTEN

TSTABLE OF CONTENTS

Dr. Holger Schmidt 4DIRECTOR, W.M. KECK CENTER FOR NANOSCALE OPTOFLUIDICSInterview with Dr. Holger Schmidt - Professor of Electrical Engineering, UC Santa Cruz.

Single Molecules on a Chip 7BY HOLGER SCHMIDT

Featured Products 10

Tradeoffs in New Generation ADCs 12BY ED KOHLER AND JASON MESSIER WITH INTERSIL

Hey You, Get Into My Cloud 19BY ROB IRWIN WITH ALTIUM

RTZ - Return to Zero Comic 24

Exploring chip-scale integration of nanotechnology and integrated optics for biomolecular science.

Analog-to-Digital Converters are becoming increasingly pervasive, and Kohler and Messier offer critical tradeoffs for product design success.

How web-based services will change the future of the electronic design process.

EEWeb | Electrical Engineering Community Visit www.eeweb.com 4

INTERVIEWFEA

TURED IN

TERVIEW

W.M. Keck Center for Nanoscale Optofluidics

How did you get into engineering and when did you start?My original degree is in physics. My M.S. thesis project dealt with semiconductor devices with direct applications in fiber-optic communications. After my PhD work in Electrical Engineering on a similar topic, I decided to develop new optical devices and methods with real-world applications.

What are your favorite hardware tools that you use?I enjoy working with a variety of lasers, in particular ultrafast lasers that produce short optical pulses only about 100 femtoseconds long. With these lasers, we can study materials on time scales that cannot be reached electronically. We also have recently set up a dual beam electron/ion beam microscope in our W.M. Keck Center for Nanoscale Optofluidics. An optofluidic device combines integrated optics with microfluidics. This can be a fluidically tuneable optical device, for example a fluidic dye laser, in which the active laser dye solution is contained in a microchannel on a chip. It can also be a device that uses integrated optical elements (waveguides, filters, splitters) to investigate or manipulate particles in a microfluidic channel, for example an integrated biosensor.

This is an extremely versatile nano-fabrication and nanocharacteriza-tion tool that is a lot of fun to work with and allows us to both sculpt and image objects on the nanoscale.

What are your favorite software tools that you use?I mostly work with MATLAB, do some programming in C, and design optical waveguide structures using simulation packages from Photon Design.

What is on your bookshelf?I have recently read The Master Switch: The Rise and Fall of Information Empires by Tim Wu

which deals with the fascinating story of the people and companies that invented new communication technologies and how they deal with issues of information control. The Elegant Universe by Brian Greene also tells a great story on the cosmic scale, presenting an introduction to string theory and its implications. I also read contemporary and classic fiction, plus a lot of children’s books with my family. Most recently, I read Aaron Hawkins’ The Year Money Grew on Trees which tells a great coming-of-age story that shows how hard work, persistence, and a great group of friends can accomplish almost anything.

Dr. Holger SchmidtDr. Holger Schmidt - Professor of Electrical Engineering; UC Santa Cruz

EEWeb | Electrical Engineering Community Visit www.eeweb.com 5

INTERVIEWFEA

TURED IN

TERVIEW

Do you have any tricks up your sleeve?In my view, the keys to achieving breakthroughs in the lab are a combination of good planning ahead of time, persistence, the ability to recognize problems or new directions, and a bit of luck at the right time.

We need to stay one step ahead by providing cutting-

edge training to our bright and

motivated students.

What has been your favorite project?For a number of years, I have had the vision of realizing optical quantum interference effects on a chip. Quantum coherence produces strange effects such as making opaque materials transparent, slowing light down, or making single photons “talk to each other.” Possible applications for quantum coherence devices include all-optical nonlinear devices (e.g., switches) that work on the few to single photon level, optical storage and memory, extremely sensitive metrology devices (magnetometers, interferometer), or single photon light sources and detectors.In collaboration with our colleagues at BYU, we have recently succeeded in slowing light down over a 1,000 times on a tiny silicon chip. Viewed

differently, we have taken a 20 foot long optical pulse and compressed it to a fraction of an inch on a chip.

Do you have any note-worthy engineering experiences?Being exposed to a one million volt spark from a Tesla coil (http://photon.soe.ucsc.edu/classes.htm ) while standing in a metal suit that acted as a Faraday cage and NOT getting shocked was one of the most exhilarating experiences of my teaching career.

What are you currently working on?We’re using laser optics in a number of ways. We are studying nanomagnets for next-generation data storage media, will attempt to stop light on a chip to create optical memory devices, and are developing optofluidic chips for biomolecular diagnostics such as virus detection at the point of care.

We use different methods to make the magnets. We make our own magnets using electron beam lithography. A photoresist is patterned with nanoscale holes; magnetic material (e.g., nickel) is deposited, followed by a liftoff process. We also get samples from Western Digital, San Jose, formerly Hitachi Global Storage Technologies. These are metallic multilayers deposited on nanosize islands that were etched into a substrate wafer. Finally, we work with a group at the University of Chemnitz, Germany, which deposits magnetic layers on top of self-assembled silica nanospheres. The spheres produce ordered patterns as they are spread on a wafer which

can make for a very quick and inexpensive patterning step. The main application we are interested in at the moment is bit-patterned magnetic storage media for next-generation hard drives. However, nanomagnets are also relevant for memory devices (MRAM) or other emerging spintronic applications.

What direction do you see your business heading in the next few years?I see a lot of potential in optofluidic technology—the combination of microfluidics and integrated optics. It allows us to look at devices that have been used for optoelectronic and communication applications in a new light. Their combination with non-solid media such as gases and liquids poses new research questions, but also has a lot of applications in the life sciences, biomedicine, toxicology, pollution monitoring, and other fields.

What challenges do you foresee in our industry?We need to stay one step ahead, which will provide cutting-edge training to our bright and motivated students. ■

Avago Technologies new AEAT-6600 Hall E� ect Magnetic Encoder delivers optimal solutions for Robotic, Industrial and Medical systems designers.

• World’s highest resolution

• 16-bit absolute positiion through SSI

• Programmable Magnetic Rotary Encoder IC

• 16-pin TSSOP package

• Power down mode

New Encoder for the Worst Case Environments

Avago Technologies Motion Control Products

For more information and to requesta free sample go to: www.avagotech.com/motioncontrol

EEWeb | Electrical Engineering Community Visit www.eeweb.com 7

PROJECTFEA

TURED PRO

JECT

By Dr. Holger Schmidt

The history of integrated photonics dates back to the late 1960s when researchers at Bell Labs proposed the use of thin film technology to create planar optical structures that would mimic the successful integration paradigm of integrated electronic circuits. The field grew rapidly along with the burgeoning area of fiber-optic communications. Even though early approaches to long-haul fiber links considered liquid-filled fibers, integrated optics was implemented almost exclusively in solid-state materials due to the challenges of guiding light through substances with low refractive indices such as gases and liquids. Unfortunately, this has prevented the creation of integrated optical devices and systems for a large class of areas, in particular the life sciences for which fluids (air, water) are the natural environment. It has only been over the past few years that rapid advances in microfluidics, silicon photonics, and integrated optics have converged into the new, burgeoning field of optofluidics, the combination of integrated optics and fluidics in a single system.

The groups of Holger Schmidt at UC Santa Cruz and Aaron Hawkins at Brigham Young University have developed a unique approach to optofluidics that is based on creating micron-scale channels that simultaneously guide light and liquids on a silicon chip.

The combination of these “liquid-core waveguides” with more conventional solid-state structures creates fully self-contained, planar chips that allow for the study and manipulation of fluids and particles therein with the convenience of off-the-shelf fiber optics equipment. Much of the early work focused on exploration of basic photonic properties such as low-loss light propagation, optical mode structure, and implementation of optical signal processing such as spectral filtering in the liquid-core waveguides. The greatest potential of the technology, however, lies in the application of these devices to fields that historically were off limits for integrated optics, for example molecular biology, medical diagnostics, toxicology, or gas spectroscopy. In particular, the demonstration of optical detection of single fluorescent molecules showed a sensitivity normally seen in expensive and bulky microscopy equipment, and provided much stimulation for new research and applications dealing with single particles on a chip.

To this end, the W.M. Keck Foundation supported the creation of the Center for Nanoscale Optofluidics at UC Santa Cruz. Directed by Professor Holger Schmidt, the Center brings together faculty from five different departments (H. Noller, Molecular Biology; M. Akeson and D. Deamer, Biomolecular Engineering; J. Zhang,

SingleMolecules on a Chip

EEWeb | Electrical Engineering Community Visit www.eeweb.com 8

PROJECTFEA

TURED PRO

JECT

Figure 1: Cartoon of optofluidic chip; photograph of chip during experiment; scanning electron images of Waveguide cross sections with hollow and solid cores along with guided light mode.

Chemistry; and W. Dunbar, Computer Engineering). In this Center, the researchers are able to take an interdisciplinary approach to exploring the use of nanoscale elements in conjunction with optofluidic waveguides to address problems in molecular biology, biophysics, and medical diagnostics.

One focus area of research within the Center is the incorporation of nanopores into optofluidic devices. The concept of nanopore biophysics was proposed by D. Deamer who recognized that a molecule passing through a nanoscale hole in a membrane could partially block the opening, and therefore reduce the amount of electric (ionic) current flowing through that hole. Effectively, such a structure functions as an electric, single molecule detector that can distinguish molecular signatures on the picoampere level. Recently, the groups of Professors Schmidt and Noller have demonstrated the first detection of single ribosomes using nanopores that were incorporated into a dielectric layer that comprises the liquid-core optofluidic waveguide. Moreover, they

were able to control the amount of nanoparticles that entered the fluidic channel by changing the applied electrical voltage. This opens up the possibility to use the nanopores as “smart gates” to introduce individual fluorescent particles into the liquid-core waveguides where they can then be investigated “on demand.” Additional collaborations are under way to apply this principle to quantum dot labeled DNA for genetic analysis and controlled nanopore translocation for DNA sequencing.

Another focus area of the Center expands on the theme of particle control. Professor Schmidt’s group has recently developed new implementations of optical particle trapping (i.e., the control over a particle’s motion and position using optical forces). Using the intrinsic optical properties of the liquid-core waveguides, they were able to hold particles in place at any position along the fluidic channel. In addition, they used light beams to accumulate over 100 particles at a single spot within the waveguide, effectively creating the equivalent of an

multi-mode fiber

single-mode fiber

EEWeb | Electrical Engineering Community Visit www.eeweb.com 9

PROJECTFEA

TURED PRO

JECT

optical leaf blower. Current efforts are directed at using optical forces to create optofluidic devices for particle sorting as well as to examine new trapping paradigms and the potential of moving particles between well-defined chemical microenvironments.

A third thrust area deals with single molecule

spectroscopy for biomedical applications. The demonstrated ability to detect fluorescent signatures from single molecules opens up the possibility to observe and count individual, labeled bioparticles such as nucleic acids (DNA, RNA) and proteins. These play a central role in molecular diagnostics applied to infectious disease detection, genetic screening, and genomics-based personalized medicine. The ability to identify single molecules on an integrated platform has the potential to break with the current diagnostic paradigm of amplifying the genomic material to create detectable signals. Schmidt’s group is working with a number of clinical researchers to explore the potential of optofluidics as a diagnostic platform.

This snapshot of the research pursued at the Keck Center at UCSC provides a glimpse at the potential of optofluidics. It opens new windows for optical and device engineers to use traditional engineering skills in new contexts that interface electrical engineering with chemists, biologists, toxicologists, and medical researchers. Thus, this emerging area provides an extremely stimulating environment for the development of new optical technology in the years to come. ■

Figure 2: Cut-open views of waveguide intersection with fluorescent particles (green) in light beam (red).

Figure 3: Optofludic waveguide chip with nanopore. Applied voltage is used

to drive nanoparticles through Nanopore into fludic channel.

EEWeb | Electrical Engineering Community Visit www.eeweb.com 10

FEATURED

PROD

UCTS

FEATURED PRODUCTS

Stellaris® Robotic Evaluation BoardThe Stellaris® Robotic Evaluation Board (EVALBOT) is a robotic evaluation platform for the Stellaris LM3S9B92 microcontroller. The board also uses a range of Texas Instruments’ analog components for motor drive, power supply, and communications functions. After a few minutes of assembly, the EVALBOT’s electronics are ready-to-run. When roaming, three AA batteries supply power to the EVALBOT. The EVALBOT automatically selects USB power when tethered to a PC as a USB device or when debugging. Test points are provided to all key EVALBOT signals. Two 20-pin headers enable future wireless

communications using standardized Texas Instruments’ low-power embedded radio modules (EM boards). Additional microcontroller signals are available on break-out pads arranged in rows adjacent to the microcontroller.The EVALBOT has factory-installed quickstart software resident in on-chip Flash memory. For software debugging and Flash programming, an integrated In-Circuit Debug Interface (ICDI) requires only a single USB cable for debug and serial port functions.For more information, please click here.

Capacitors for High Pulse Current ApplicationsVishay Intertechnology, Inc. introduced a new multilayer ceramic chip capacitor (MLCC) featuring an integrated resistor and low electrostrictive ceramic formulation. For high-pulse-current applications, the VJ controlled discharge capacitor (CDC) offers excellent reliability, high voltage ratings from 1,000 VDC to 1,500 VDC, and a capacitance range from 33 nF to 560 nF. The integration of a high-capacitance MLCC with a bleed resistor on its surface allows the VJ CDC to discharge more rapidly, while also reducing board space requirements and

assembly costs. Typical applications for the device include detonation devices (munitions, pyrotechnics, blasting) and electronic fuzing. The capacitor released today is manufactured in Noble Metal Electrode (NME) technology with a wet build process. The VJ CDC features a low electrostrictive ceramic formulation for repeated charge and discharge cycles, allowing the device to achieve very high field reliability. For more information, please click here.

among dissimilar signals within a device. The 89600 VSA software’s new multi-measurement capability has been engineered to deliver the power of multiple signal analyzers with the convenience of a single, optimized user interface. The software’s advanced architecture will enable engineers to configure multiple measurements simultaneously. For more information, please click here.

RF Multi-Measurement Signal AnalyzerAgilent Technologies Inc. announced that an innovative, new multi-measurement capability is being added to its 89600 VSA software, enabling simultaneous signal analysis of multiple carriers and signal formats for more efficient testing and deeper signal insight in wireless test. With wireless R&D and manufacturing engineers increasingly working with more than one signal at a time?whether for multi-format/multi-carrier devices or for viewing both uplink and downlink signals at the same time?analyzing one signal at a time is no longer efficient. Moreover, it fails to provide intelligence about the subtle interactions

14-Bit, 500MSPS ADCISLA214P50The ISLA214P50 is a 14-bit, 500MSPS analog-to-digital converter designed with Intersil’s proprietary FemtoCharge™ technology on a standard CMOS process. The ISLA214P50 is part of a pin-compatible portfolio of 12 to 16-bit A/Ds with maximum sample rates ranging from 130MSPS to 500MSPS.The device utilizes two time-interleaved 250MSPS unit ADCs to achieve the ultimate sample rate of 500MSPS. A single 500MHz conversion clock is presented to the converter, and all interleave clocking is managed internally. The proprietary Intersil Interleave Engine (I2E) performs automatic correction of offset, gain, and sample time mismatches between the unit ADCs to optimize performance.A serial peripheral interface (SPI) port allows for extensive configurability of the A/D. The SPI also controls the interleave correction circuitry, allowing the system to issue offline and continuous calibration commands as well as configure many dynamic parameters.Digital output data is presented in selectable LVDS or CMOS formats. The ISLA214P50 is available in a 72 Ld QFN package with an exposed paddle. Operating from a 1.8V supply, performance is specified over the full industrial temperature range (-40°C to +85°C).

Key Specifications• SNR @ 500MSPS

= 72.7dBFS fIN = 30MHz = 70.6dBFS fIN = 363MHz

• SFDR @ 500MSPS= 84dBc fIN = 30MHz = 76dBc fIN = 363MHz

• Total Power Consumption = 835mW @ 500MSPS

Features• Automatic Fine Interleave Correction Calibration• Single Supply 1.8V Operation• Clock Duty Cycle Stabilizer• 75fs Clock Jitter

• 700MHz Bandwidth

• Programmable Built-in Test Patterns

• Multi-ADC Support

- SPI Programmable Fine Gain and Offset Control- Support for Multiple ADC Synchronization- Optimized Output Timing

• Nap and Sleep Modes- 200µs Sleep Wake-up Time

• Data Output Clock

• DDR LVDS-Compatible or LVCMOS Outputs

• User-accessible Digital Temperature Monitor

Applications• Radar Array Processing• Software Defined Radios• Broadband Communications• High-Performance Data Acquisition• Communications Test Equipment

DIGITALERROR

CORRECTION

SHA

VINP

VINN

14-BIT250 MSPS

ADC

CLOCKMANAGEMENT

SHA14-BIT

250 MSPSADC

CLKP

CLKN

SPICONTROL

CS

BS

CLK

SD

IO

VREF

OV

SS

AV

SS

AV

DD

CLKOUTP

CLKOUTN

D[13:0]P

D[13:0]N

ORP

ORN

OV

DD

CLK

DIV

NA

PS

LP

SD

O

+–VCM

RES

ETN

VREF

I2EGain, Offsetand Skew

Adjustments

CLK

DIV

RS

TP

CLK

DIV

RS

TN

RLV

DS

Pin-Compatible Family

MODEL RESOLUTIONSPEED(MSPS)

ISLA216P25 16 250

ISLA216P20 16 200

ISLA216P13 16 130

ISLA214P50 14 500

ISLA214P25 14 250

ISLA214P20 14 200

ISLA214P13 14 130

ISLA212P50 12 500

ISLA212P25 12 250

ISLA212P20 12 200

ISLA212P13 12 130

March 15, 2011FN7571.1

Intersil (and design) is a registered trademark of Intersil Americas Inc. Copyright Intersil Americas Inc. 2011All Rights Reserved. All other trademarks mentioned are the property of their respective owners.

Get the Datasheet and Order Samples

http://www.intersil.com

EEWeb | Electrical Engineering Community Visit www.eeweb.com 12

Tradeoffsin New-generation

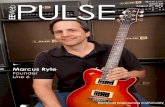

ADCs Jason MessierStaff Applications Engineer

Edward KohlerStrategic Marketing Manager

Driven by a widening range of high-performance application

requirements, Analog-to-Digital Converters (ADCs) are becoming an increasingly pervasive design element, and numerous tradeoffs between performance, cost, and complexity are critical factors for the overall success of product designs.

Although there will never be a simple one-size-fits-all solution for ADCs, a number of ongoing technology trends in ADC design now offer designers the ability to closely tailor ADC selection to optimize cost and performance for their specific application requirements. This article is intended to provide an overview of these technology trends, along with some design examples to provide context for understanding the real-

world tradeoffs between different approaches.

ADC Trends: Balancing between SNR, Resolution, Sample Rates, and Power

ADC designs must achieve an appropriate balance between given performance criterion, such as signal-to-noise (SNR), resolution, and sample rates while also conforming to often very tight power budgets.

One overarching trend in ADC capabilities has been the ongoing push for higher resolution and SNR performance at a given sample rate. For example, for 500 mega-samples per second (MSPS), today’s newest high-performance ADCs can provide 72.5dB at 14-bits compared to previous ADC

capabilities that were limited to 66-67dB at 12-bits. This progress, enabled by the advance of both state-of-the-art design techniques and semiconductor processing capabilities, represents essentially a 100 percent improvement in achievable signal-to-noise ratio, evolving over approximately five years.

Another trending axis of improvement has been to increase the available maximum sample rate for a given resolution and SNR. As recently as one year ago, there were only two major ADC vendors offering 14-bit ADCs that provided sampling rates above 155 MSPS. Now, most ADC manufacturers are pushing sample rates to 250 MSPS with 14-bit devices that can deliver 70dB or better SNR performance,

EEWeb | Electrical Engineering Community Visit www.eeweb.com 13

TECHN

ICA

L ARTIC

LETECHNICAL ARTICLE

and some are providing a second generation that can deliver over 73dB. Similarly, the maximum sample rate for 16-bit converters has been improved from 200 MSPS in 2008 to 250 MSPS in late 2010 while maintaining SNR above 75dB. This continual improvement in sample rate of high-resolution ADCs is being driven by the increasing resolution and speed requirements of applications such as broadband communications test equipment and advanced medical imaging.

Low-power operation is also an increasingly critical factor for many ADC applications. This is especially true for handheld devices that must live within a tight power budget as well as for designs that require many ADCs where the combined power usage becomes an important issue. As will be discussed in subsequent sections of this article, the ability to minimize power for a given level of SNR, resolution, and sample rate performance can be the vital linchpin issue in success of the overall product design, and at least one low-power ADC architecture has emerged to meet this need.

Another arena of trending change within ADC designs is the variety of interface technologies for getting data on and off the chip. In the beginning, CMOS I/O was sufficient for supporting most applications. However, increasing performance requirements have led to an evolution of faster I/O approaches including DDR, LVDS, Serial LVDS, and potentially SERDES interfacing (While this article focuses primarily on the key performance and power tradeoffs, in a future article we will explore the ongoing ADC interface evolution in more depth).

Scenario #1: Critical Goal: Achieving High SNR and Dynamic Range

For many higher-performance applications, the overriding requirement is achievement of the SNR and dynamic range parameters without regard to power usage issues.

Prime examples of these performance-first applications are mission-critical military designs such as radar signal processing. Among the key characteristics driving this type of design is the need to deal with both large and small signals simultaneously, and to be able to discriminate both, which requires excellent dynamic range and SNR performance. For instance, in a radar system, strong and weak return signals from both near and distant objects must be processed at the same time with consistent accuracy and speed. If the ADC does not have sufficient dynamic range, then the larger signals will completely dominate the entire range of the converter, and the system will not be able to see the weaker signals. Filtering out the large signals is typically not an option in these types of systems because of the inherently random and changing nature of the signal levels and mix.

Another type of application that often falls into this category is high-performance measurement instrumentation, such as signal analyzers. The system designer typically has to create a robust set of capabilities, and a performance window that spans a wide range of signal sensitivity instead of pre-tailoring the box for a fixed set of

parameters. Here again, building from the ground up around ADCs with maximum dynamic range and robust SNR characteristics at a high sample rate is the way to enable instrumentation platforms that can provide the widest performance window.

Similar challenges exist in many communications applications such as wireless base stations that must distinguish between strong and weak signals to determine proper routing and handoff procedures. In all of these applications, the only option is to design with ADCs that provide the highest possible dynamic range and SNR characteristics at the required sampling rates.

One advanced design approach that is proving very useful in these applications is the tight integration of multiple ADC cores that are interleaved using advanced on-chip hardware such as the proprietary Intersil Interleave Engine (I2E). In this approach, hybrid digital/analog background calibration techniques continuously adjust the gain, offset, and sample phase of the multiple interleaved ADC cores, removing inherent manufacturing mismatch as well as adjusting, in real-time, for any mismatches induced by temperature and voltage variations (See Figure 1).

Interleaving lower-resolution ADCs at the system level (such as 6-bit, 8-bit, or even 10-bit devices) has become a fairly standard practice, especially for time domain applications where spurious free dynamic range (SFDR) is not a major concern. However, for high-performance applications requiring

EEWeb | Electrical Engineering Community Visit www.eeweb.com 14

TECHN

ICA

L ARTIC

LETECHNICAL ARTICLE

converter resolutions of 12-bits and above, interleaving ADCs can become very complex and are best implemented at the chip level. Die-level interleaving of the ADC cores overcomes the dynamic variances in performance that become roadblocks when trying to interleave separate ADCs at higher resolutions. Well-controlled process matching as well as common voltage and temperature characteristics provide inherently better uniformity between the cores that cannot be achieved with separate devices.

To achieve nearly perfect matching, the on-chip I2E calibration transparently fine tunes performance on the fly to ensure consistency and to eliminate variances. The real-time adjustments by the I2E make use of arbitrary application sample data to estimate and correct for interleave mismatch of gain, offset, and sample time skew. This enables the multiple cores to perform together as a single high-performance ADC that can effectively multiply the sample rate by the number of cores, all without requiring any

12E: Offset/Gain/Phase ErrorEstimation and Correction

Figure 1: Intersil Interleave Engine (I2E)

compromises on dynamic range, SNR, or robustness.

As shown in Figure 2, ADC architectures with advanced interleaving can provide the highest levels of resolution, at high sample rates, as compared to Sigma-Delta, SAR, or pipelined architectures without advanced interleaving. For example, Intersil’s ISLA214P50 incorporates two time-interleaved 14-bit 250MSPS ADCs to achieve the sample rate of 500MSPS with SNR performance of 72.7dBFS.

Scenario #2: Need Flexibility for Tradeoffs between Performance, Power, & Design Complexity

In these situations, the designer typically has some flexibility to approach the application in different ways, thereby enabling tradeoffs in ADC selection between performance, power, and other design considerations. For example, this category includes applications where the signal level might vary, but the variations are either predictable or manageable, such

that the system could be designed to adjust and accommodate the variability.

For instance, a point-to-point microwave communications link between two stations would typically involve less signal variation because it uses focused antennas with minimal blockage between the sending and receiving points. However, signal levels are occasionally impacted by weather conditions (e.g., rain, sleet). This allows for multiple approaches to the system design. One design option would be to use a high-end ADC such as described in the previous scenario with sufficiently wide dynamic range to simply capture and process the diminished signal on the fly. Alternatively, the designer could tradeoff by selecting an ADC with lower dynamic range and using gain control circuitry to adjust the signal path based on weather conditions so that the signal is always provided to the ADC at a consistent level. Of course, the efficacy of one approach versus the other would depend on specific application requirements, such as

EEWeb | Electrical Engineering Community Visit www.eeweb.com 15

TECHN

ICA

L ARTIC

LETECHNICAL ARTICLE

ADC Architecturevs Resolution and Sample Rate

Sampling Rate (MHz)

Reso

lutio

n (b

its, ~

SNR)

24

22

20

18

16

14

12

10

8

0.1 0.5 1 5 10 50 100 500 1000 2000

Sigma-Delta

SAR

Pipeline

Flash

Pipeline withInterleaving

the frequency and variability of the signal changes, as well as the power requirements for using a higher SNR ADC versus the external gain control circuitry.

Another interesting application in this category could be laser range finders, where a signal of fixed strength is sent out in multiple directions and then both the strength and time signature of the return signals are used to perform distance measurements to create 3D mapping of complex spaces. The signal measurements need to take into account both the surface reflectivity and the distance to the objects being measured. From a signal processing standpoint, a number of design tradeoffs come

into play for such applications.

For example, a higher-resolution ADC could be used to resolve the signals more quickly by eliminating the need to average when a lower resolution ADC is used, thereby allowing faster measurements with fewer pulses. With potentially millions of measurements required to map some locations, the amount of time per measurement can be a significant factor. On the other hand, the nature of laser mapping applications can require a certain degree of system portability or even require battery operated platforms for some outdoor applications such as mapping bridge supports. Depending on the specific application requirements,

a designer might opt for lower-power, lower-resolution ADCs in combination with external circuitry for averaging the results, or he or she might choose to build the system around higher-resolution ADCs to increase accuracy and speed while minimizing the number of measurements required.

For these application areas that require a variety of tradeoffs in ADC capabilities, it can be advantageous to leverage pin-compatible families of devices that give the designer a broader range of choices than with single-point products. For example, a designer that needs to make tradeoffs between resolution and sample rate could start by prototyping with a 14-bit 500 MSPS part and, if needed, could move to a 16-bit 250 MSPS pin-compatible device within the same family without making any changes to the design.

Similarly, if the designer needed to tradeoff SNR versus power for a given resolution and sample rate, it is helpful to use a pin-compatible family that provides multiple options. For instance, some families offer multiple performance grades that can provide two or more levels of SNR with the higher SNR coming at the price of increased power consumption. Product designs for increased battery life or higher performance can again be offered without making any changes to the underlying hardware.

This flexibility allows designers to tailor and fine-tune the ADC capabilities to meet the specific application requirements without necessitating changes to the overall product design and support

Figure 2: Comparison of ADC Architectures vs. Resolution and Sample rate

EEWeb | Electrical Engineering Community Visit www.eeweb.com 16

TECHN

ICA

L ARTIC

LETECHNICAL ARTICLE

circuitry. The ability to leverage pin-compatible families also opens up options for marketing multiple versions of the same basic product design at different performance levels to meet a broader set of market requirements.

Scenario #3: Minimizing Power Usage is the Critical Factor

In this final group of applications, providing ultra low-power operation is the overarching factor for design success. Typical products in this category are handheld devices that need higher bandwidth combined with portability, such as military and law enforcement radios, ultrasonic non-destructive scanners, and

portable cable TV signal analyzers. Sometimes also included in this category are applications where the shear number of ADCs being deployed has a cumulative power usage impact that needs to be minimized, such as some wire-line communication systems with thousands of ADCs, where the overall infrastructure’s power budget becomes an important factor.

In all of these cases, designers need to have a given amount of dynamic range but must achieve that performance at the lowest possible power level. ADC manufacturers therefore must deliver the performance requirements with ultra low-power

chip level architectures. In addition, the ADC architectures should provide designers with the flexibility to minimize power requirements in the support circuitry and the overall design.

A significant step forward in the creation of ultra low-power ADC implementations is represented by Intersil’s FemtoCharge® technology, which fundamentally changes the approach for pipelined signal processing designs. For any pipelined ADC signal processing chain, gain is required between stages. In conventional architectures, signals in each gain stage have traditionally been represented by voltages. In contrast, the FemtoCharge architecture shifts

2x gain

Voltage passedbetween stages

1-bit to DEC

2x gain

1-bit DAC

2x gain

Traditional ADC

Stage N-1 Stage N+11-bit ADC

Charge passedbetween stages

1-bit to DEC

Cfd Cfd2*Cfd

1-bit DAC

Femtocharge ADC

Stage N-1 Stage N+11-bit ADC

Stage N

Stage N

VQC=

12

Figure 3: Comparison of Voltage-based and Charge-based Pipeline Architectures

EEWeb | Electrical Engineering Community Visit www.eeweb.com 17

TECHN

ICA

L ARTIC

LETECHNICAL ARTICLE

the approach and represents signals using electrical charge. This may seem like a subtle difference but in practice, it has major implications for lowering power usage.

In most pipelined ADC designs, the signal must be amplified from stage-to-stage to get the necessary conversion resolution. Voltage-based designs have two limitations. First, signal gain requires an operational amplifier (Op-Amp) and these have high power consumption and limit overall ADC performance due to the dual requirement of high speed and high accuracy. And second, voltage-based designs necessitate that the signal be recreated at each stage. By comparison, charge-based ADCs use the scaling of capacitance to achieve gain from stage-to-stage. In a capacitor, Voltage = Charge/Capacitance. Therefore the voltage gain needed in each successive stage can be created simply by reducing its capacitance in relation to the preceding stages. And, rather than having to recreate a voltage-based signal from scratch for each stage, in a charge-based pipeline, the original signal is conserved by simply transferring it from one stage to the next (See Figure 3).

The FemtoCharge approach enables creation of high performance ADCs with ultra-low-power characteristics. For example, the ISLA216P25IRZ, a 16-bit 250 MSPS ADC, is the first and only 16-bit converter with a sample rate over 175 MSPS that consumes less than one watt (786 mW at 250 MSPS). Furthermore, a charge-based ADC such as the ISLA214P50IRZ is not only the first 14-bit 500MSPS

converter, but it also provides 73dB of SNR and consumes only 835-900 mW, providing approximately 3dB more SNR at one third the power of its only competitor above 250 MSPS. Charge based designs are thereby giving system designers a whole new set of options for minimizing power without compromising performance.

The Bottom Line: More Options Enable Better Design Tradeoffs

Although new-generation product requirements continue to escalate and require more demanding signal processing at ever-lower power budgets, the good news for designers is that new-generation ADC architectures are staying ahead of the curve.

New advances such as shared-die, multi-core interleaved architectures with transparent on-chip calibration now enable the creation of very high-resolution, high sampling rate ADCs that do not compromise SNR performance, while minimizing design complexity and power. In addition, breakthroughs such as FemtoCharge are enabling even greater power savings by fundamentally shifting the approach to pipelined ADC design.

The bottom line for designers is a much broader set of options to choose from, which leads to better tradeoffs and more effective tailoring of the ADC functionality to meet overall design objectives.

About the Authors

Edward Kohler is Intersil’s strategic marketing manager for high-speed data converters and ADC drivers.

To begin his career, Edward spent eight years developing high speed, charge domain, analog-to-digital converters and was one of the inventors of Intersil’s Femtocharge technology. He earned his bachelor’s and master’s degrees in electrical engineering at Michigan Technological University and the University of Michigan and his MBA from Yale University.

Jason Messier works as a staff applications engineer in Intersil’s high-speed converter group. He holds a BSEE from Northeastern University, an MSEE from Carnegie Mellon University, and an MBA from Babson College. Jason spent eight years in the automatic test equipment industry before joining Intersil in 2006 to design and later support high-speed converters. ■

You can’t design for the future with yesterday’s technology. With a robust product portfolio, a proven track record of industry innovation and an unwavering commitment to engineering excellence—Silicon Labs’ technology is ready to meet your isolation needs.

Find out what you need to know to reduce EMI for medical applications: www.silabs.com/low-emi-medical

OPTOCOUPLERS ARE OLD TECHNOLOGY

OPTOCOUPLERS1960s–2009

Say hello to the Silicon Labs’ family of digital isolator and ISOdriver solutions and say goodbye to the limitations

of optocouplers. Silicon Labs’ isolators feature ultra low power consumption even at incredibly fast data

rates, robust multi-channel and bi-directional communications and reliability unachievable with optocouplers.

ISOdrivers combine our digital isolator technology with gate drivers, delivering up to 4 A peak output current.

DIGITAL ISOLATION SOLUTIONS FROM SILICON LABS—ISOLATION TECHNOLOGY FOR THE 21ST CENTURY.

ROBUST AND RELIABLE OPERATION THAT YOUR APPLICATIONS DEMAND

Silicon Labs’ isolators and ISOdrivers lead the industry in data rate, propagation delay, RF immunity, ESD and jitter performance. And they excel in even the harshest environments.

THE LOWEST POWER CONSUMPTION EVEN AT VERY HIGH DATA RATES

Based on our patented RF isolation architecture, Silicon Labs’ digital isolators offer the lowest power consumption at data rates up to 150 Mbps. Power consumption stays low even as data rates increase.

MULTI-CHANNEL AND BI- DIRECTIONAL COMMUNICATIONS— IT’S ALL IN THE FAMILY

Silicon Labs’ digital isolators are designed for a wide range of demanding applications. With a small footprint, up to 5 kV isolation and up to 6 channels, we’ve got a solution for all of your isolation needs.

FLOPPY DISKS1980s–1990s

VHS TAPES1970s–1990s

ROTARY PHONES1920s–1980s

VACUUM TUBES1910–1958

©20

11 S

ilic

on L

abor

ator

ies

Inc.

All

rig

hts

rese

rved

.

EEWeb | Electrical Engineering Community Visit www.eeweb.com 19

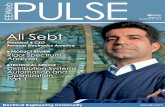

Rob IrwinProduct Manager

HEY,YOU!

Get intomy Cloud

You know it’s a brave new world when board design and cloud computing get mentioned in the same

breath. But it seems that internet-based services and ecosystems—also known as “the cloud”—and electronic devices are colliding with ever-increasing force. Today electronic products have evolved beyond the box that houses the chips and boards, and developed intelligence that transcends their inbuilt logic and programming. Devices are now intimately connected to remote services, and indeed the true value of electronic devices is shifting from the device itself to the online systems that support it.

On the surface it would seem that electronics designers should be able to go about their business largely as usual, connecting components to provide a hardware infrastructure and developing the embedded software that provides the base functionality. After all, the hardware still needs to be built and function. But this value shift has some subtle but profound implications on the industry moving forward.

IDC has predicted that there will be 15 billion connected devices by 2015. Ericsson has put the figure at 50 billion devices by 2020. Whatever the real number, the fact is the market is going to demand a real lot of devices real quick, all of them connected to the cloud and utilizing sophisticated web services to provide functions and features we haven’t even thought of yet.

The question is, who will create these devices and the ecosystems that support them, and how can they build the systems fast enough?

A Problem of Scalability

If we shuffle back in time a little to when analog was king, an electronic system was effectively the board and the components sitting on it. The design engineer’s job was essentially to electrically connect the components in many and varied forms in order to make the electrons flow in useful ways. Fast-forward to the microcontroller era and the job not only involved connecting the components, but also providing the ones and zeros

EEWeb | Electrical Engineering Community Visit www.eeweb.com 20

TECHN

ICA

L ARTIC

LETECHNICAL ARTICLE

that powered the processor and drove the system—the embedded software. The electronic system had evolved from a purely hardware problem, to a hardware and software problem.

What we’re seeing now is the evolution of software development from being a purely embedded prospect, to one that is distributed between the intelligence built into a device and provided by its supporting online ecosystem. As well as that, the hardware itself is moving increasingly to reprogrammable platforms to cope with the rapid and ongoing development of devices beyond their initial release.

What we have here is a problem of scalability. The challenges of marrying programmable hardware, embedded software, and web services can all be overcome with our current methodologies given time and suitable engineering and Web development resources.

Figure 1: Today, the design of the humble PCB encompasses much more than the fixed components and copper it’s made of, relying on a complex interaction between hardware, software and online services to deliver features and functionality to the end user.

But if we’re to get 50 billion devices into production in the next ten years then we really need to radically rethink how we go about taking designs from concept to production.

To Catch a Thief

It’s interesting to reflect that one of the most important enabling elements in building today’s computers is in fact the computer itself. The earliest digital computers were designed with nothing much more than paper and drafting pens. But it wasn’t long before we pressed these basic machines into a service to aid us in building more complex computers. Repeat this cycle a few times and pretty soon you have a billion transistors on a chip and a complex system to support it—all delivered in a neat package with keyboard and mouse for a few hundred dollars. It’s fair to say computer-aided design (CAD) and electronics design automation (EDA) have revolutionized the process of capturing our ideas and turning them into manufactured products.

As devices move into the realm of cloud connectivity, becoming far more complex distributed systems than we’ve ever designed before, it’s worth considering whether the cloud itself could provide a possible way forward in bringing scalability to next-generation device design. There’s an old saying that it takes a thief to catch a thief. In this case, perhaps it takes a cloud-based approach to design to build a mass market of cloud-enabled devices.

Taking EDA Into the Cloud

Electronics design tool vendors have often been criticized for lagging the technology that they’re ostensibly charged with enabling. As devices become increasingly internet-enabled, and depend more and more on back-end, cloud-based ecosystems to provide critical functionality, this criticism could justifiably be leveled again.

That’s not to say EDA tool companies are ignoring the cloud. Many of the chip tool vendors are actively looking to provide some design functions, such as complex verification, as cloud-based services. So indeed, EDA companies are looking at how they can use the cloud as a way to deliver their tools in a more cost-effective and scalable way. While this is, on the surface, a reasonable course of action, it really ignores the bigger issue for EDA vendors when it comes to the cloud.

Connectingto people

Connecting toother ecosystems

Connecting toother devices

EmbeddedSoftware

ProgrammableLogic

EEWeb | Electrical Engineering Community Visit www.eeweb.com 21

TECHN

ICA

L ARTIC

LETECHNICAL ARTICLE

It’s not really about tool vendors using the cloud to simply provide the tools and services they currently offer in a better or more efficient way. The real game changer comes in the broader product development arena, and it will happen when the tool vendors ask themselves one simple question: How can they use the cloud to help their customers design for the cloud, and not just design the devices that connect to it?

If we hark back to the computer design example mentioned earlier, simply using the computer as a glorified drafting table (which was essentially the basis

Figure 2: Design tool company Altium has launched its AltiumLive online portal that connects directly to its Altium Designer software and Design Vault technology to bring web services directly into the electronics design space.

of first board design programs) didn’t really raise the abstraction level at which we could design. It just let us do what we’d always done, only a bit faster and more conveniently. It wasn’t until we used the computational power and logic available to automate processes and help make and enforce design decisions that we were able to move forward at the pace necessary to make the digital age a reality.

Similarly, electronics designers today need tools that allow them to harness their device design experience

and extend it to the design of device ecosystems. What’s needed is a unification of device and web applications development within a single tool framework. When we start to apply the power inherent in connecting devices and applications to Web-based services and infrastructure to actually developing new, internet-connected devices, we’ll see the ‘internet of things’ really start to take shape.

Cloud-Based Design for Everyone

A simple example of the power of device-to-cloud connectivity is the way Amazon’s Kindle book reader system synchronizes itself across multiple platforms. Regardless of which device you use—Kindle for PC, Kindle for iPad, the Kindle device itself—when you open any device you’ll be presented with the last page you were reading, regardless of which device you were last reading it on. Amazon uses a person’s Kindle account in the cloud to transparently synchronize this information across all devices in the ecosystem.

Now Amazon is a large company with huge resources available, so it has the ability to push through the development of such a system with the tools currently available by gathering together hardware, software and web development teams, each working within their individual realms of expertise.

But imagine if cloud connectivity and a range of cloud service building blocks and templates were standard parts of an electronic product developer’s design tool. And imagine if the design environment on the designer’s desktop was part of a larger, cloud-based ecosystem that provided automatic hosting and deployment services (among other things) that allowed designers to connect the devices they design directly to the cloud and utilize the services they create.

With such a system, even developers with limited resources could bring the potential of cloud-based services and functions directly and easily to their products and the people using them.

The Shape of Things to Come

One could argue that the entire history of solid-state electronics has been one of unification. Multiple transistors were brought together on a single piece of silicon. Functional circuit blocks have been combined to create large-scale integrated circuits. Software has been

AltiumLiveSubscriber AltiumLive

SubscriberNot an

AltiumLiveSubscriber

Company Network

AltiumLive

Satellite Vault

AltiumLiveSubscriber

Alti

umLi

veID

Acc

ess

Perm

issi

ons

Access

Contro

lled vi

a Altiu

mLiv

e ID

Access Controlled via AltiumLive ID

Acc

ess

Con

trol

led

via

Alti

umLi

ve ID

Data

Dat

a

Data

Local Access O

nly

EEWeb | Electrical Engineering Community Visit www.eeweb.com 22

TECHN

ICA

L ARTIC

LETECHNICAL ARTICLE

unified with hardware to create programmable platforms. At each stage, the technology and the tools have evolved to raise the level of abstraction at which we can work. It’s this principle that has allowed us to achieve the many orders of magnitude increase in system complexity in the relative short lifetime of the industry.

Today we’re reaching another technological turning point, and once again we need to unify processes and evolve the tools in order to progress. A number of companies and products have demonstrated the power of connecting devices to Web-based ecosystems. Increasingly, this cloud connectivity is automated and does not require human interaction. As we move forward, cloud connectivity will be a necessary part of all devices across the spectrum of markets from consumer and industrial through to military. This will happen because the potential of ubiquitous device connectivity is too great to ignore, similar to past state changes such as the digital and embedded software revolutions.

For engineers and designers this will mean changing their mindsets to incorporate online components directly

into the hardware and embedded design process right from the start of a project. For tool providers it means finding ways to utilize the cloud to provide “plug and play” access to online services, real-time connections into supply chain and manufacturing information via the web, and an expanded definition of design components to include functionality provided remotely to hardware devices via back-end, online ecosystems.

Whichever way you look at it, electronics designers and engineers are headed for the cloud. The real question is, when they get there will they be able tap into that silver lining?

About the Author

Rob Irwin has a Bachelor of Engineering (Electrical) from the University of Sydney, Australia. He has over 20 years of experience in the electronic design industry including several years as editor of Australian Electronics Engineering. Rob currently holds the position of Product Manager at Altium Limited. ■

Altium VaultDesign Space Supply Chain Space

Procurement

Vault-Based ComponentsReusable Design ContentProduction Release Data

Fabrication

Assembly

Testing

Coil Comparator.PrjPcbSchematicsPCBDevice SheetsLibrariesOutput JobsHarness DefinitionsAnnotation File

Feedback_Resonator.PrjPcb

Flux_Triangulator.PrjPcb

Figure 3: Design tool company Altium’s Vault technology uses web-based services to connect components in the design space to the wider supply chain, allowing designers to get real-time price, availability, and other information on parts as they use them within the Altium Designer software.

EEWebElectrical Engineering Community

Contact Us For Advertising Opportunities

www.eeweb.com/advertising

BeStar®

ACOUSTICS & SENSORS

Teamwork • Technology • Invention • Listen • Hear

PRODUCTSSpeakers

Buzzers

Piezo Elements

Back-up Alarms

Horns

Sirens/Bells

Beacons

Microphones

Sensors

INDUSTRIESAutomotive

Durables

Medical

Industrial

Mobile

Fire / Safety

Security

Consumer

Leisure

QS9000 • TS/ ISO16949 • ISO14001 • ISO13485 • ISO9001

bestartech.com | [email protected] | 520.439.9204

Preferred acoustic componentsupplier to OEMs worldwide

EEWeb | Electrical Engineering Community Visit www.eeweb.com 24

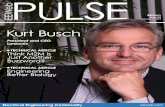

RETURN TO

ZERORETURN TO ZERO

EEWeb | Electrical Engineering Community Visit www.eeweb.com 25

RETURN TO

ZERORETURN TO ZERO