Modeling HDL components for FPGAs in control applications · Modeling HDL components for FPGAs in...

Transcript of Modeling HDL components for FPGAs in control applications · Modeling HDL components for FPGAs in...

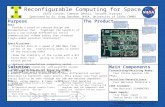

1© 2014 The MathWorks, Inc.

Modeling HDL components for

FPGAs in control applications

Mark Corless, Principal Application Engineer, Novi MI

2

High resolution

voltage

modulation

Low latency

control loops

Critical

diagnostics

Position

sensing

System cost

reduction

Why would I use an

FPGA for a controls application?

FPGA = Field Programmable Gate Array

3

How do I get an idea

out of my head

and into an

FPGA?

4

How do I get an idea

out of my head

and into an

FPGA?

How do I get an idea

out of my head

and into a microprocessor?

5

desktop simulation

rapid prototyping

production code generation

6

That sounds nice, but…

Show me!

7

Begin with existing C component models

Position

Velocity

Units

Open

Loop

Disabled

Encoder

CalibrationVoltage

Units

Current

Units

Mode

Scheduler

Field

Oriented

Control

Velocity

Control

8

Create new HDL component models

Position

Velocity

Units

Open

Loop

Disabled

Encoder

CalibrationVoltage

Units

PWM

Peripheral

Current

Units

Encoder

Peripheral

Mode

Scheduler

Field

Oriented

Control

Velocity

Control

C HDL

HDL = Hardware Description Language

9

Migrate some component models from C to HDL

Position

Velocity

Units

Open

Loop

Disabled

Encoder

CalibrationVoltage

Units

PWM

Peripheral

Current

Units

Encoder

Peripheral

Mode

Scheduler

Field

Oriented

Control

Velocity

Control

C HDL

10

How did models help us design C

components?

11

Baseline three-phase motor control hardware setup

FPGA

with vendor

provided

peripherals

Simulink Real-TimeTM

scheduler and peripheral interface

Controller model for C

implementationWe will use this for

HDL implementation

12

Rapid prototyping model with Speedgoat bitstream

Controller model for C

implementation

Field-oriented controller

is the fastest loop and

runs at 25 kHz

13

Rapid prototyping model with Speedgoat bitstream

Interface block to

encoder peripheral

on FPGA

Interface block to

PWM peripheral on

FPGA

Controller model for C

implementation

14

Rapid prototyping model with Speedgoat bitstream

This is the end

result, but it’s

not where we

started…

15

Simulate design on the desktop

Controller model for C

implementation

We started

designing the

controller at our

desktops…

Mathematical models

of motor, load, and

peripherals

16

Simulate design on the desktop

“Lumped parameter”

model of encoder sensor

and peripheral

17

Compare desktop simulation and hardware data

Correlation of simulation and

hardware results provided

confidence in the workflow

18

How do I create a new HDL

component model?

19

Begin with existing C component models

Position

Velocity

Units

Open

Loop

Disabled

Encoder

CalibrationVoltage

Units

Current

Units

Mode

Scheduler

Field

Oriented

Control

Velocity

Control

20

Create new HDL component models

Position

Velocity

Units

Open

Loop

Disabled

Encoder

CalibrationVoltage

Units

PWM

Peripheral

Current

Units

Encoder

Peripheral

Mode

Scheduler

Field

Oriented

Control

Velocity

Control

C HDL

21

Example workflow to design an HDL component

1. Design the component with a unit-level testbench

2. Integrate the component with the system-level testbench

3. Partition the design for code generation

4. Generate a bitstream for the FPGA

5. Prototype the design on real-time hardware

22

1. Design the component with a unit-level testbench

Peripheral will

run at

33 MHz on the

FPGA

Lo-fidelity model to capture

25 kHz dynamics of combined

sensor and peripheral

23

1. Design the component with a unit-level testbench

24

1. Design the component with a unit-level testbench

25

1. Design the component with a unit-level testbench

Simulation results provide

confidence in lo-fidelity and

implementation fidelity

peripheral models

26

2. Integrate the component with the system-level testbench

Implementation fidelity peripheral models require a

1/33 MHz simulation step size so simulation time will be

longer than the testbench with lo-fidelity peripherals

27

2. Integrate the component with the system-level testbench

Use lo-fidelity peripheral

models for interactive

control design

Use hi-fidelity peripheral implementation

models to confirm integrated behavior

28

3. Partition the design for code generation

Group C components Group HDL components

Optionally generate

algorithmic

HDL code

29

4. Generate a bitstream for the FPGA

Use HDL Workflow Advisor

to specify additional

information required to

create a bitstream

30

4. Generate a bitstream for the FPGA

Specify card and FPGA

toolchain

31

4. Generate a bitstream for the FPGA

Associate ports in model

with pins on FPGA or PCI

interface to processor

HDL Workflow Advisor will

automate interacting with the

Xilinx toolchain to create the

bitstream for the FPGA

32

4. Generate a bitstream for the FPGA

HDL Workflow Advisor also

generates an interface block

which can be used with

Simulink Real-Time

33

4. Generate a bitstream for the FPGA

We use a MATLAB® script

to only expose ports of

interest and make a prettier

mask

34

5. Prototype the design on real-time hardware

Integrate bitstream interface

block into Simulink Real-

Time model

35

5. Prototype the design on real-time hardware

Correlation of simulation and

hardware results provides

confidence in the workflow

36

How do I migrate a component model

from C to HDL?

37

Migrate some component models from C to HDL

Position

Velocity

Units

Open

Loop

Disabled

Encoder

CalibrationVoltage

Units

PWM

Peripheral

Current

Units

Encoder

Peripheral

Mode

Scheduler

Field

Oriented

Control

Velocity

Control

C HDL

38

Migrate some component models from C to HDL

Position

Velocity

Units

Open

Loop

Disabled

Encoder

CalibrationVoltage

Units

PWM

Peripheral

Current

Units

Encoder

Peripheral

Mode

Scheduler

Field

Oriented

Control

Velocity

Control

C HDL

39

Example workflow to migrate a component to HDL

1. Design the component with a unit-level testbench

2. Integrate the component with the system-level testbench

3. Partition the design for code generation

4. Generate a bitstream for the FPGA

5. Prototype the design on real-time hardware

Modify component to

account for differences

between C and HDL

Model to simplify timing

constraints for disparate rates

Add timing constraint file to

FPGA project

40

Modify to account for differences between C and HDL

States can be reset through

enable or trigger portsStates are explicitly reset

using signals

41

Modify to account for differences between C and HDL

“Tunable” parameters are

explicitly routed to ports

Parameters are “tunable”

directly from blocks or

data objects

42

Modify to account for differences between C and HDL

Typically floating point for rapid

prototyping

Typically fixed-point for rapid

prototyping

43

Model to simplify timing constraints for disparate rates

Integrate 25 kHz control loop

with 33 MHz peripheral

components

44

Model to simplify timing constraints for disparate rates

Insert slow delay at fast to

slow rate transitions, this

makes it simple to author

timing constraint file

Example constraint file

45

Compare simulation and hardware results

Correlation of simulation and

hardware results provides

confidence in the workflow

46

What did we learn?

47

High resolution

voltage

modulation

Low latency

control loops

Critical

diagnostics

Position

sensing

System cost

reduction

Models can help you design FPGA components for

control applications

48

Through this exercise we learned that…

C and HDL components often run at disparate rates

– Design components with similar rates of interest

– Confirm system level behavior by integrating components

– Consider low fidelity peripheral models for control design tasks

There are some differences when modeling for HDL than C

– Explicitly reset states and route tunable parameters for HDL

– Typically model HDL algorithms in fixed-point

– Consider adding delays to simplify timing constraint specification

Overall Model-Based Design is similar for C and HDL

– Simulate components to reduce dependency on hardware

– Rapid prototype to verify behavior on hardware

– Generate algorithm code for integration into production environment