Introduction to VLSI Testing

description

Transcript of Introduction to VLSI Testing

VLSI Testing Class

Introduction to VLSI Testing

李昆忠 Kuen-Jong Lee

Dept. of Electrical EngineeringNational Cheng-Kung University

Tainan, Taiwan

VLSI Testing NCKUEE-KJLEEIntroduction.2

Problems to Think

How are you going to test

• A 32 bit adder

• A 32 bit counter

• A 32Mb cache memory

• A 107-transistor CPU

• A 109-transistor SOC

VLSI Testing NCKUEE-KJLEEIntroduction.3

OUTLINE• Introduction• Fault modeling• Fault simulation• Test generation• Automatic test pattern generation

(ATPG)• Design for testability• Built-in self test• Synthesis for testability• An example

VLSI Testing NCKUEE-KJLEEIntroduction.4

Basic Concept of Testing

Related fields Verification: To verify the correctness of a design Diagnosis: To tell the faulty site

Reliability: To tell whether a good system will work correctly or not after some time. Debug: To find the faulty site and try to eliminate the fault

VDD

0/10

000 0

Testing: To tell whether a circuit is good or bad

VLSI Testing NCKUEE-KJLEEIntroduction.5

Why Studying Testing?

• Economics! Reduce test cost (enhance profit)

Automatic test equipment (ATE) is extremely expensive

Shorten time-to-market Market dominating or sharing

Guarantee IC quality and reliabilityDefects detected in CostWafer 0.01 – 0.1Packaged chip 0.1 – 1Board 1 – 10System 10 – 100Field 100 – 1000

Rule of Ten: Cost to detect faulty IC increases by an order of magnitude

VLSI Testing NCKUEE-KJLEEIntroduction.6

Principle of Testing

• Testing typically consists of Applying set of test stimuli (input patterns, test

vectors) to inputs of circuit under test (CUT), and Analyzing output responses

• The quality of the tested circuits will depend upon the thoroughness of the test vectors

Circuit under Test

(CUT)

-101111-00-0-1-01--00-101

1-0010011--11011001-01-11

ComparatorStoredCorrect

ResponseTest Result

Input Patterns Output Response

VLSI Testing NCKUEE-KJLEEIntroduction.7

Importance of testing

N = # transistors in a chipp = prob. (a transistor is faulty)Pf = prob. (the chip is faulty)

Pf = 1- (1- p) N

If p = 10-6

N = 106

Pf = 63.2%

VLSI Testing NCKUEE-KJLEEIntroduction.8

Introduction• Integrated Circuits (ICs)

have grown in size and complexity since the late 1950’s Small Scale Integration (SSI) Medium Scale Integration

(MSI) Large Scale Integration (LSI) Very Large Scale Integration

(VLSI)• Moore’s Law: scale of ICs

doubles every 18 months Growing size and complexity

poses many and new testing challenges

VLSIVLSI

LSILSIMMSSII

SSSSII

VLSI Testing NCKUEE-KJLEEIntroduction.9

Importance of Testing• Moore’s Law results from decreasing feature

size (dimensions) from 10s of m to 10s of nm for transistors and

interconnecting wires• Operating frequencies have increased from

100KHz to several GHz• Decreasing feature size increases probability

of defects during manufacturing process A single faulty transistor or wire results in faulty

IC Testing required to guarantee fault-free products

VLSI Testing NCKUEE-KJLEEIntroduction.10

Difficulties in Testing• Fault may occur anytime - Design - Process - Package - Field• Fault may occur at any place

• VLSI circuit are large

- Most problems encountered in testing are NP-complete • I/O access is limited

Vss

Vdd

VLSI Testing NCKUEE-KJLEEIntroduction.11

How to do testing

• Circuit modeling• Fault modeling

• Logic simulation• Fault simulation• Test generation

• Design for test• Built-in self test

• Synthesis for testability

Modeling

ATPG

Testable design

From designer’s point of view:

VLSI Testing NCKUEE-KJLEEIntroduction.12

Circuit Modeling

• Structural model--- collection of interconnected components or elements

• Functional model--- logic function - f(x1,x2,...)=... - Truth table

• Behavioral model--- functional + timing - f(x1,x2,...)=... , Delay = 10

AB

E

0

CD F

G1

1

0

0

VLSI Testing NCKUEE-KJLEEIntroduction.13

Levels of Structural Description

• Switch level

• Higher/ System level

• Circuit level

• Gate level

B

E

C1

C2C3

C4

C

E

CD F

G

AB

VDD VDD VDD

VLSI Testing NCKUEE-KJLEEIntroduction.14

Fault Modeling• The effects of physical defects• Most commonly used fault model: Single stuck-at fault

AB

CD

E

F

G

A s-a-1A s-a-0

E s-a-1E s-a-0

D s-a-1D s-a-0

C s-a-1C s-a-0

B s-a-1B s-a-0

F s-a-1F s-a-0

G s-a-1G s-a-0

14 faults• Other fault models: - Break faults, Bridging faults, Transistor stuck-open faults, Transistor stuck-on faults, Delay faults

VLSI Testing NCKUEE-KJLEEIntroduction.15

Fault Coverage (FC)

FC =# faults detected# faults in fault list

ab

c 6 stuck-at faults( a0,a1,b0,b1,c0,c1 )

Test faults detected FC{(0,0)}{(0,1)}{(1,1)}

{(0,0),(1,1)}{(1,0),(0,1),(1,1)}

c1

a1,c1

a0,b0,c0

a0,b0,c0,c1

all

16.67%33.33%50.00%66.67%

100.00%

Example:0 00

1 11

1 00

VLSI Testing NCKUEE-KJLEEIntroduction.16

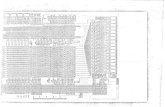

Wafer Yield (Chip Yield, Yield)

Wafer yield = 12/22 = 0.55 Wafer yield = 17/22 = 0.77

Wafer

Defects

Good Chip

Faulty Chip

VLSI Testing NCKUEE-KJLEEIntroduction.17

Testing and Quality

• Quality of shipped parts is a function of yield Y and the test (fault) coverage T

• Defect level (DL, reject rate in textbook): fraction of shipped parts that are defective

ICFabrication Testing

Yield:Fraction of good parts

Rejects

Shipped Parts

Quality:Defective parts

per million (DPM)

VLSI Testing NCKUEE-KJLEEIntroduction.18

Defect Level, Yield & Fault Coverage

Yield (Y)50%75%90%95%99%

90%90%

90%90%

Fault Coverage (T)

90%90%

90%90%90%

95%90%

99%99.9%

DPM (DL)

28,00067,000

10,000 5,000 1,000

5,00010,000

1,000 100

DL: defect level Y: yieldT: fault coverage

DL = 1 - Y (1-T)~

VLSI Testing NCKUEE-KJLEEIntroduction.19

Logic simulation • To determine how a good circuit should work

• Given input vectors, determine the normal circuit response

A

B

E

C

G

F

I

HD

C

E

CC

1

B RB

IR

IF

CC2

CDE CJE

A

B

EC

D

F

VLSI Testing NCKUEE-KJLEEIntroduction.20

Fault simulation

0

• Given a test vector, determine all faults that are detected by this test vector.Example:

AB

CTest vector (1 1) detects

{ a0, b0, c1}

• To determine the behavior of faulty circuits

F

D

B

CG

1/01/0

1

A 10

0

1

10

11

E s.a.0

VLSI Testing NCKUEE-KJLEEIntroduction.21

Test generation

To detect D s-a-0, D must be set to 1. Thus A=B=1.

To propagate fault effect to the primary output E must be 1. Thus C must be 0.

Test vector: A=1, B=1, C=0

• Given a fault, identify a test to detect this faultExample:

AD

B

EC

F

0 1/01

1

1

0

1/0

VLSI Testing NCKUEE-KJLEEIntroduction.22

Automatic Test Pattern Generation ATPG: Given a circuit, identify a set of test vectors to detect all faults under consideration.

Input circuit

Form fault list

More faults?

Select a fault

Test generation

Fault simulation

Exit

Faultdropping

No

Yes

VLSI Testing NCKUEE-KJLEEIntroduction.23

Difficulties in Test Generation

E

B F

C

A

D

1. Reconvergent fanout

s-a-10/1

0

1

1 0

1

10

0/1

Cannot detect the fault

Fault detected

VLSI Testing NCKUEE-KJLEEIntroduction.24

Difficulties in Test Generation (cont.)

2. Sequential test generation

JK

CK

Y

PIs POs

clk

Combinational part

Y

VLSI Testing NCKUEE-KJLEEIntroduction.25

Testable Design

• Design for testability (DFT) • ad hoc techniques

• Scan design• Boundary Scan

• Built-In Self Test (BIST)

• Random number generator (RNG)• Signature Analyzer (SA)

• Synthesis for Testability

VLSI Testing NCKUEE-KJLEEIntroduction.26

Example of ad hoc Techniques

Insert test points

MUX

T/N

VLSI Testing NCKUEE-KJLEEIntroduction.27

Scan Design

Combinationallogic

PIs POs

FF

FF

FF

Combinationallogic

PIs POs

SFF

SFF

SFF

SO

SIT/N

Original design Modified design

VLSI Testing NCKUEE-KJLEEIntroduction.28

Scan Cell Design

DI

DI

D Q

CK

DI D Q Q,SOSI

MU

X

CKN/T(SE)

DIQ,SO

SI

T

T +

Q

Q

Most cell libraries now have scan cells!

VLSI Testing NCKUEE-KJLEEIntroduction.29

Scan Register

DQ

SI

DQ

SI

DQ

SI

DQ

SISO

CLKSE

CombinationalCircuits

VLSI Testing NCKUEE-KJLEEIntroduction.30

Boundary Scan

Instruction register

Bypass registerMUX

TAP

Misc. registers

TRST*

TMS

TCK

TDO

I/O Pad Boundary scan cell Boundary scan path

APPLICATION LOGIC

BIST register

Scan register

TRST*:Test rest (Optional)TDI: Test data inputTD0: Test data output TCK: Test clockTMS: Test mode select

TDISout

Sin

VLSI Testing NCKUEE-KJLEEIntroduction.31

Boundary Scan (Cont.)

Instruction register

Bypass register

MUX

TAP

Misc. registers

TRST*

TMS

TCK

TDO

APPLICATION LOGICTDI Sout

Sin

Instruction register

Bypass register

MUX

TAP

Misc. registers

TRST*

TMS

TCK

TDO

APPLICATION LOGIC

Scan register

TDI Sout

Sin

Instruction register

Bypass register

MUX

TAP

Misc. registers

TRST*

TMS

TCK

TDO

APPLICATION LOGIC

BIST register

Scan register

TDI Sout

Sin

Instruction register

Bypass register

MUX

TAP

Misc. registers

TRST*

TMS

TCK

TDO

APPLICATION LOGIC

BIST register

Scan register

TDI Sout

Sin

BIST register

Scan register

BIST register

VLSI Testing NCKUEE-KJLEEIntroduction.32

Places the job of device testing inside the device itself

Generates its own stimulus and analyzes its own response

circuit under testmux

from system

patte

rnge

nera

tor

BISTController

bistonR

espo

nse

Ana

lyze

r

to system

good/fail

bistdone

Built-In-Self Test (BIST)

VLSI Testing NCKUEE-KJLEEIntroduction.33

Built-In-Self Test (BIST) (Cont.)

F/F

• Two major tasks - Test pattern generation - Test result compaction • Usually implemented by linear feedback shift register

F/F F/F

VLSI Testing NCKUEE-KJLEEIntroduction.34

Random Number Generator (RNG)

000110000100001010011100

011010110101101011011110

1. Generate “pseudo” random patterns2. Period is 2n - 1

1111 0111 0011 0001 (repeat)

F/F F/F F/F F/F

VLSI Testing NCKUEE-KJLEEIntroduction.35

Signature Analyzer (SA)

5421 xxxxP

Input sequence 10101111 (8 bits) 1 2 3 4 5+ Z

Remainder Quotient

Time Input stream Register contents Output stream01..5678

1 0 1 0 1 1 1 1 0 0 0 0 0 Initial state 1 0 1 0 1 1 1 1 0 0 0 0 . . . . 1 0 1 0 1 1 1 1 1 0 0 0 0 1 0 1 1 0 0 0 0 1 0 1 0 0 1 0 1 1 0 1

++

42 xxxR 21 x

765421 xxxxxxG

VLSI Testing NCKUEE-KJLEEIntroduction.36

Signature Analyzer (SA) (cont.)

• A LFSR performs polynomial division

• Probability of aliasing error = 1/2n (n: # of FFs)

1:

1: 2

245

xxQ

xxxxP

1

1567

2452467

xxx

xxxxxxx

xGxxxxxxRxQxP 124567

VLSI Testing NCKUEE-KJLEEIntroduction.37

Memory BIST Architecture

MemoryModule

di

addr

wen

data

sys_disys_addrsys_wen

MemoryModulerst_l

clkhold_l

test_hsise

data

q

so

Before After

VLSI Testing NCKUEE-KJLEEIntroduction.38

Memory BIST Architecture (Cont.)

BIST Circuitry

MemoryModule

Alg

orith

m-B

ased

Patte

rn G

ener

ator

Com

pres

sor

diaddrwen

data

compress_h

sys_addrsys_disys_wen

rst_lclk

hold_ltest_h

q

so

clkrstsise

VLSI Testing NCKUEE-KJLEEIntroduction.39

CPU Test Control Architecture

TDI

TCK

compressor

Scan_i

Scan_en

Bist

controlMemory

logic

Scan_oScan path

clkrst_l

TAP ControllerIR

scandecoder

MU

X

decoder

bistdecoder

mbistint_scan

bist_se

test_h

hold_l

bist_so

TMS

TDO

bist

_si

VLSI Testing NCKUEE-KJLEEIntroduction.40

Problems re-thinking

• A 32-bit adder --- ATPG

• A 32-bit counter --- Design for testability + ATPG

• A 32MB Cache memory --- BIST

• A 107-transistor CPU --- All test techniques

• An SOC

VLSI Testing NCKUEE-KJLEEIntroduction.41

Conclusions• Testing is becoming a major factor in design optimization• Conventionally, the designer often optimize one of the three

attributes: speed, area, and power.• At present, a fourth attribute is considered: Testability. • Two major fields in testing

ATPG --- Fault simulation --- Test generation

Testable design --- Design for testability --- Built-in self-test --- Synthesis for testability