Chapter 2 MOS Transistor Theory

description

Transcript of Chapter 2 MOS Transistor Theory

Chapter 2Chapter 2

MOS Transistor TheoryMOS Transistor Theory

Boonchuay SupmonchaiIntegrated Design Application Research (IDAR) Laboratory

June 16th, 2004; Revised June 16th, 2005

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 2

B.SupmonchaiB.Supmonchai

Goal of this chapterGoal of this chapter Present intuitive understanding of device

operation

Introduction of device basic equations

Introduction of models for manual analysis First-Order ModelFirst-Order Model

Analysis of secondary and deep-sub-micron deep-sub-micron effectseffects

Future trends

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 3

B.SupmonchaiB.Supmonchai

n

p

A

B

Al

One-dimensionalrepresentation

A

B

diode symbol

Mostly occurring as parasitic element in Digital ICsMostly occurring as parasitic element in Digital ICs

The DiodeThe Diode

p

n

B A SiO2Al

Cross-section of pn-junction in an IC process

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 4

B.SupmonchaiB.Supmonchai

hole diffusionelectron diffusion

p n

hole driftelectron drift

ChargeDensity

Distancex+

-

ElectricalxField

x

PotentialV

ξ

ρ

W2-W1

ψ0

( ) .a Current flow

( ) .b Charge density

( ) .c Electric field

( ) d Electrostatic.potential

Diode - Depletion RegionDiode - Depletion Region

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 5

B.SupmonchaiB.Supmonchai

Diode - Zero BiasDiode - Zero Bias Build-in (Electrostatic) Potential:

€

φ0 = φT lnNA ND

ni2

⎛

⎝ ⎜

⎞

⎠ ⎟

TT = Thermal Voltage = kt/q = 26 mV at 300 K26 mV at 300 K (Si)

nnii = Intrinsic carrier concentration ~ 1.5 x 101.5 x 101010 cm cm-3-3

NNAA = Acceptor concentration (atoms/cm3)

NNDD = Donor concentration (atoms/cm3)

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 6

B.SupmonchaiB.Supmonchai

Typically avoided in Digital ICsTypically avoided in Digital ICs

Diode - Forward BiasDiode - Forward Bias

Excess Carriers

Excess Carriers

DiffusionDiffusion

currentcurrent

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 7

B.SupmonchaiB.Supmonchai

The Dominant Operation ModeThe Dominant Operation Mode

Diode - Reverse BiasDiode - Reverse Bias

DiffusionDiffusion

currentcurrent

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 8

B.SupmonchaiB.Supmonchai

Diode TypesDiode Types

Linear ApproximationLinear Approximation Exponentially DistributedExponentially Distributed

0.370.37ppn0n0

Short-Base Diode is the standard in semiconductor devicesShort-Base Diode is the standard in semiconductor devices

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 9

B.SupmonchaiB.Supmonchai

Diode CurrentDiode Current

VVDD = Diode Bias Voltage, = Diode Bias Voltage, IIDD = Diode Current = Diode Current

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 10

B.SupmonchaiB.Supmonchai

Models for Diode Manual AnalysisModels for Diode Manual Analysis

VD

ID = IS(eVD/φT – 1)+

–

VD

+

–

+

–VDon

ID

( ) a Ideal diode model ( ) - b First order diode modelIdeal Diode ModelIdeal Diode Model

€

ID = IS eVD φT −1( )

€

ID = IS eVD φT −1( )

VD

ID = IS(eVD/φT – 1)+

–

VD

+

–

+

–VDon

ID

( ) a Ideal diode model ( ) - b First order diode modelFirst-order Diode ModelFirst-order Diode Model

(typ. 0.7 V)

IIss = Saturation Current = Saturation Current ~ 10~ 10-17-17 A/ A/mm22

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 11

B.SupmonchaiB.Supmonchai

Example: A Diode CircuitExample: A Diode Circuit

1: 1: IIDD = = IIS S [exp([exp(VVD D //TT) - 1]) - 1]

2: 2: IIDD = ( = (VVS S - - VVDD)/)/RRSS

Using VD(ON) = 0.7 V

IIDD = 0.23 mA = 0.23 mA

VVDD= 0.7 V= 0.7 V

IIDD = 0.224 mA = 0.224 mA

VVDD= 0.757 V= 0.757 V

Graphic SolutionGraphic Solution

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 12

B.SupmonchaiB.Supmonchai

€

C j =C j 0

1−VD φ0( )m

CCjj00 = Zero-Biased Junction Capacitance = Zero-Biased Junction Capacitance = = ff(physical parameters)(physical parameters)

mm = Grading Coefficient = Grading Coefficient (0.5 - Abrupt, 0.33 - linear )(0.5 - Abrupt, 0.33 - linear )

Diode - Junction CapacitanceDiode - Junction Capacitance

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 13

B.SupmonchaiB.Supmonchai

Diode - Diffusion CapacitanceDiode - Diffusion Capacitance

€

Cd =dQD

dVD

= τ T

dID

dVD

≈τ T ID

φT

= mean transit time= mean transit time= average time for a carrier to be transported

from the junction to the metallic contact

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 14

B.SupmonchaiB.Supmonchai

Diode Switching TimeDiode Switching Time

TimeTime

VVDD

ON OFF ON

Space chargeSpace chargeExcess chargeExcess charge

t t == 00

VV11

VV22 t t == TT

Vsrc

VV DD

Rsrc

ID

Switching TimeSwitching Time is is strongly determined by strongly determined by how fast the charge can how fast the charge can be moved aroundbe moved around

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 15

B.SupmonchaiB.Supmonchai

Diode - Secondary Effects IDiode - Secondary Effects IAvalanche BreakdownAvalanche Breakdown

At Critical Field At Critical Field EEcritcrit, carriers crossing the depletion region is , carriers crossing the depletion region is accelerated to high velocity such that when they collide with accelerated to high velocity such that when they collide with immobile silicon atoms, electron-hole pairs are created immobile silicon atoms, electron-hole pairs are created

-20-20

EEcritcrit = 2x10= 2x1055 V/cm V/cm

Breakdown VoltageBreakdown Voltage

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 16

B.SupmonchaiB.Supmonchai

Diode - Secondary Effects IIDiode - Secondary Effects II

TT T T

IISS = f(T) = f(T) Theory: 2X2X every 5ºCExperiment: 2X2X every 8ºC

(For fixed I(For fixed IDD) V) VDD decreases 2mV per ºC decreases 2mV per ºC

IIDD increases 6% per ºC increases 6% per ºC(2X every 12 º C)(2X every 12 º C)

Temperature EffectsTemperature Effects

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 17

B.SupmonchaiB.Supmonchai

+

VD

-

ID

ID

RS

CD

+

-

VD

€

ID = IS eVD nφT −1( )

€

C j =C j 0

1−VD φ0( )m +

τ T IS

φT

eVD nφT

nn = emission coefficient (≥ 1) = emission coefficient (≥ 1)

Diode SPICE ModelDiode SPICE Model

NeutralRegions

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 18

B.SupmonchaiB.Supmonchai

SPICE Diode Model ParametersSPICE Diode Model Parameters

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 19

B.SupmonchaiB.Supmonchai

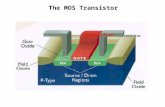

What is a MOS(FET) Transistor?What is a MOS(FET) Transistor? MMetal-OOxide-SSemiconductor FField-EEffect

TTransistor (MOSFETMOSFET, or MOSMOS, for short)

A Four-terminal device GateGate controls how much current can flow from the

SourceSource to the Drain.Drain.

BodyBody modulates device characteristics and parameters - secondary effect.

A switch!

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 20

B.SupmonchaiB.Supmonchai

MOS Transistors - Types and SymbolsMOS Transistors - Types and Symbols

D

S

G

NMOS Depletion

G

S

D

PMOS Enhancement

D

S

G B

NMOS with Bulk Contact

D

S

G

NMOS Enhancement

The The BodyBody terminal, if not shown, is assumed to be connected to terminal, if not shown, is assumed to be connected to the appropriate supply.the appropriate supply.

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 21

B.SupmonchaiB.Supmonchai

| V| VGS GS | < | V| < | VTT | | | V| VGS GS | > | V| > | VTT | |

GateGate

SourceSource(of carriers)(of carriers)

DrainDrain(of carriers)(of carriers)

| V| VGS GS ||

Open (off)Open (off) (Gate = ‘0’‘0’) Closed (on)Closed (on) (Gate = ‘1’‘1’)

RRonon

Switch Model of NMOS TransistorSwitch Model of NMOS Transistor

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 22

B.SupmonchaiB.Supmonchai

| V| VGS GS | > | V| > | VDDDD – | V – | VT T | || | | V| VGS GS | < | V| < | VDDDD – |V – |VTT| || |

Switch Model of PMOS TransistorSwitch Model of PMOS Transistor

Open (off)Open (off) (Gate = ‘0’‘0’) Closed (on)Closed (on) (Gate = ‘1’‘1’)

RRonon

GateGate

SourceSource(of carriers)(of carriers)

DrainDrain(of carriers)(of carriers)

| V| VGS GS ||

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 23

B.SupmonchaiB.Supmonchai

Why MOS Transistor?Why MOS Transistor? MOS performs well as a switch with very few

parasitic effects.

Relatively “Simple” manufacturing process (compared to other types of transistor)

High Integration Density Large and Complex circuits can be created

economically.

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 24

B.SupmonchaiB.Supmonchai

The NMOS TransistorThe NMOS Transistor

Polysilicon Aluminum

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 25

B.SupmonchaiB.Supmonchai

p+ stopperp+ stopper

Gate oxideGate oxide

n+

SourceSource DrainDrain

p substrate

Bulk (Body)Bulk (Body)

Field-OxideField-Oxide(SiO(SiO22))n+

Polysilicon Polysilicon GateGate

L

W

The NMOS Transistor Cross SectionThe NMOS Transistor Cross Section

• nn areas have been doped with donordonor ions (arsenic) of concentration NNDD - electronselectrons are the majority carriers

• pp areas have been doped with acceptoracceptor ions (boron) of concentration NNAA - holesholes are the majority carriers

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 26

B.SupmonchaiB.Supmonchai

MOS Transistors - BehaviorsMOS Transistors - Behaviors StaticStatic Behavior:

Threshold Voltage Channel-Length Modulation Velocity Saturation Sub-threshold Conduction

Dynamic (Transient)Dynamic (Transient) Behavior: MOS Structure Capacitances Channel Capacitances Junction Capacitances Sources-Drain Parasitic Resistance

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 27

B.SupmonchaiB.Supmonchai

Threshold Voltage ConceptThreshold Voltage Concept

VVGS GS +

SS DD

p substratep substrate

BB

GG

n+n+n+n+ n+n+

p substratep substratedepletion region

n channeln channel

The value of The value of VVGSGS where strong inversion occurs is called where strong inversion occurs is called

thethe threshold voltage, Vthreshold voltage, VTT

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 28

B.SupmonchaiB.Supmonchai

Threshold Voltage Components IThreshold Voltage Components I Work function differenceWork function difference between the gate and

the channel, GCGC

• GC GC = = FF(substrate) - (substrate) - MM for metal gate

• GC GC = = FF(substrate) - (substrate) - FF(gate)(gate) for polysilicon gate

Gate voltage component to change (invert) the surface potential, 22F F

• Fermi Potential, Fermi Potential, F F = = T T ln(Nln(NA A / n/ nii))

• F F ~ -0.3 V-0.3 V for p-type silicon substrate

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 29

B.SupmonchaiB.Supmonchai

Threshold Voltage Components IIThreshold Voltage Components II Gate voltage component to offset the depletion

region charge, QQB B / C/ Coxox

• Gate Oxide Capacitance per unit areaGate Oxide Capacitance per unit area, CCoxox = = oxox / t / toxox• Depletion region charge,

€

QB = 2qNAεsi ⋅ −2φF −VSB

Voltage component to offset fixed charges in the gate oxide and in the silicon-oxide surface, QQS S / C/ Coxox

Threshold adjustment by applying the ion implant-ation into the channel, QQI I / C/ Cox ox

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 30

B.SupmonchaiB.Supmonchai

The Threshold VoltageThe Threshold Voltage

€

VT =φGC −2φF −QB

Cox

−QS

Cox

−QI

Cox

€

VT =VT 0 + γ⋅ −2φF +VSB − −2φF( )

€

VT 0 =VT VSB=0

€

γ =2q⋅NAsi

Cox

Body-effect Body-effect coefficientcoefficient

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 31

B.SupmonchaiB.Supmonchai

The Body Effect - EmpiricallyThe Body Effect - Empirically

0.4

0.45

0.5

0.55

0.6

0.65

0.7

0.75

0.8

0.85

0.9

-2.5 -2 -1.5 -1 -0.5 0

VVSBSB (V) (V)

VVTT (

V)

(V

)

VVSBSB normally positive for n-channel devices with the body tied to ground

A negative bias causes VVTT to increase from 0.45V to 0.85V

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 32

B.SupmonchaiB.Supmonchai

SS

DD

BB

GG

n+n+n+n+

VVGSGS VVDSDS

Transistor in Resistive (Linear) ModeTransistor in Resistive (Linear) Mode

The current is a The current is a linearlinear function of both function of both VVGSGS and and VVDSDS

Assume VAssume VGS GS > V> VTT

IIDD

x

V(x)V(x)-- ++ n+n+

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 33

B.SupmonchaiB.Supmonchai

SS

DD

BB

GG

n+n+n+n+

VVGSGS

Transistor in SaturationTransistor in Saturation

Assume VAssume VGS GS > V> VTT

x

VVGSGS-V-VTT-- ++

VVDS DS > V> VGSGS - V - VTT

Pinch-offPinch-off

The current remains The current remains constant (saturates)constant (saturates)..

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 34

B.SupmonchaiB.Supmonchai

I-V Relations: Long-Channel DeviceI-V Relations: Long-Channel Device

Effective Length of the conductive channel is Effective Length of the conductive channel is inversely proportionalinversely proportional to V to VDSDS

Quadratic Relationship

Linear Relationship

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 35

B.SupmonchaiB.Supmonchai

Long-Channel I-V Plot (NMOS)Long-Channel I-V Plot (NMOS)

0

1

2

3

4

5

6

0 0.5 1 1.5 2 2.5

I D (

A)

VDS (V)

X 10-4

VVGSGS = 1.0V = 1.0V

VVGSGS = 1.5V = 1.5V

VVGSGS = 2.0V = 2.0V

VVGSGS = 2.5V = 2.5V

LinearLinear SaturationSaturation

VVDSDS = V = VGSGS - V - VTT

NMOS transistor, 0.25um, Ld = 10um, W/L = 1.5, VDD = 2.5V, VT = 0.4V

cut-offcut-off

Qu

adr

atic

dep

end

en

ce

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 36

B.SupmonchaiB.Supmonchai

€

υ =nξ

1+ ξ ξ c

for ξ ≤ ξ c

υ sat for ξ > ξ c

⎧ ⎨ ⎪

⎩ ⎪

Velocity SaturationVelocity Saturation

ξξ (V/µm)(V/µm)ξξcc = 1.5= 1.5

υυ nn (( mm

// ss))

υυsatsat = 10= 1055

Constant mobility (slope = µ)

Constant velocity

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 37

B.SupmonchaiB.Supmonchai

Short-Channel DevicesShort-Channel Devices

For an NMOS device with For an NMOS device with LL of .25 of .25mm, only a couple of volts , only a couple of volts between between SS and and DD are needed to reach velocity saturation are needed to reach velocity saturation

Short-channel device

VVDSADSATT

ExtendedExtendedsaturationsaturation

II

VVGS GS = V= VDDDD

DD

VVDSDS

Long-channel device

VVGSGS - V- VTT

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 38

B.SupmonchaiB.Supmonchai

I-V Relation: Short-Channel DevicesI-V Relation: Short-Channel Devices Linear RegionLinear Region: VDS VGS – VT

IIDD = = ((VVDSDS) ) k’k’nn W/LW/L [( [(VVGSGS – – VVTT))VVDSDS – – VVDSDS22/2]/2]

where ((VV) = 1/(1 + () = 1/(1 + (VV//ξξccLL)))) is a measure of the degree of velocity saturation

Saturation ModeSaturation Mode: VDS = VDSAT VGS – VT

IIDSATDSAT = = ((VVDSATDSAT) ) k’k’nn W/LW/L [( [(VVGSGS – – VVTT))VVDSATDSAT – – VVDSATDSAT22/2]/2]

where VVDSATDSAT = ( = (VVGSGS – – VVTT ) )((VVGSGS – – VVTT))

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 39

B.SupmonchaiB.Supmonchai

0

0.5

1

1.5

2

2.5

0 0.5 1 1.5 2 2.5

I D (

A)

VDS (V)

X 10-4

VVGSGS = 1.0V = 1.0V

VVGSGS = 1.5V = 1.5V

VVGSGS = 2.0V = 2.0V

VVGSGS = 2.5V = 2.5V

Short-Channel IV Plots (NMOS) Short-Channel IV Plots (NMOS)

Lin

ear

de

pen

den

ce

Early VelocityEarly VelocitySaturationSaturation

LinearLinear SaturationSaturation

NMOS transistor, 0.25um, Ld = 0.25um, W/L = 1.5, VDD = 2.5V, VT = 0.4V

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 40

B.SupmonchaiB.Supmonchai

Velocity Saturation EffectsVelocity Saturation Effects Short-Channel Devices

tend to operate in saturation conditions more often than the long-channel devices.

Velocity-saturation causes the short-channel device to saturate at substantially smaller values of VDS resulting in a substantial drop in current drive(for V(for VDS DS = 2.5V, W/L = 1.5)= 2.5V, W/L = 1.5)

0

1

2

3

4

5

6

0 0.5 1 1.5 2 2.5

VVGSGS (V) (V)

II DD (

A)

(A

)

long-channel long-channel quadraticquadratic

short-channel short-channel linearlinear

X 10-4

IIDD-V-VGSGS Characteristics Characteristics

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 41

B.SupmonchaiB.Supmonchai

A PMOS TransistorA PMOS Transistor

-2.5 -2 -1.5 -1 -0.5 0-1

-0.8

-0.6

-0.4

-0.2

0x 10

-4

VDS (V)

I D (

A)

VVGSGS = -1.0V = -1.0V

VVGSGS = -1.5V = -1.5V

VVGSGS = -2.0V = -2.0V

VVGSGS = -2.5V = -2.5V Assume all voltageAssume all voltageVariables negative!Variables negative!

PMOS transistor, 0.25um, Ld = 0.25um, W/L = 1.5, VDD = -2.5V, VT = -0.4V

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 42

B.SupmonchaiB.Supmonchai

Sub-Threshold ConductionSub-Threshold Conduction

0.0 1.0 2.0 3.0VGS (V)

10−12

10−10

10−8

10−6

10−4

10−2

ln(ID) (A)

Subthreshold exponential region

Linear region

VT

I D (A

) Quadratic region

€

S = nkT

q

⎛

⎝ ⎜

⎞

⎠ ⎟ln 10( )

90 mv/decade90 mv/decade

Charges are “Charges are “leakingleaking” through the devices, of which the rate is ” through the devices, of which the rate is determined by the determined by the slope factor Sslope factor S in the subthreshold region in the subthreshold region

SS

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 43

B.SupmonchaiB.Supmonchai

A Unified Model for Manual analysisA Unified Model for Manual analysis

S D

G

B

For NMOS, all five parameters For NMOS, all five parameters ((VVTOTO, , γγ, , VVDSATDSAT, , k’k’, , ) are positive.) are positive.

For PMOS, they are negative.For PMOS, they are negative.

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 44

B.SupmonchaiB.Supmonchai

0 0.5 1 1.5 2 2.50

0.5

1

1.5

2

2.5x 10

-4

VDS

(V)

I D (

A)

Model

SPICE

Simple Model versus SPICE Simple Model versus SPICE

VelocityVelocitySaturatedSaturated

LinearLinear

SaturatedSaturated

VVDSATDSAT=V=VGTGT

VVDSDS=V=VDSATDSAT

VVDSDS=V=VGTGT

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 45

B.SupmonchaiB.Supmonchai

VVT0T0(V)(V) γγ(V(V0.50.5)) VVDSATDSAT(V)(V) k’(A/Vk’(A/V22)) (V(V-1-1))

NMOSNMOS 0.43 0.4 0.63 115 x 10-6 0.06

PMOSPMOS -0.4 -0.4 -1 -30 x 10-6 -0.1

Transistor Model for Manual analysisTransistor Model for Manual analysis

Parameters for manual model of generic 0.25 um CMOS processParameters for manual model of generic 0.25 um CMOS process(Minimum length device)(Minimum length device)

CautionCaution! Try to extrapolate the behavior of the device other than W and L given in the table can lead to sizable errors.

Digital Circuits usually use Minimum Length devices

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 46

B.SupmonchaiB.Supmonchai

The Transistor Modeled as a SwitchThe Transistor Modeled as a Switch

0

1

2

3

4

5

6

7

0.5 1 1.5 2 2.5

VDD (V)

Req

(O

hm)

x105

S DRo

n

VGS VT

VVDDDD(V)(V) 11 1.51.5 22 2.52.5

NMOS(kNMOS(k)) 35 19 15 13

PMOS (k) 115 55 38 31

(for VGS = VDD, VDS = VDD VDD/2)

Modeled as a switch with infinite off resistance and a finite on resistance, Ron

Resistance inversely proportional to W/L (doubling W halves Ron)

For VDD>>VT+VDSAT/2, Ron independent of VDD

Once VDD approaches VT,

Ron increases dramatically

RRon on (for W/L = 1) (for W/L = 1)For larger devices For larger devices divide Rdivide Reqeq by W/L by W/L

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 47

B.SupmonchaiB.Supmonchai

Dynamic Behavior of MOS TransistorDynamic Behavior of MOS Transistor

DS

G

B

CGDCGS

CSB CDBCGB

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 48

B.SupmonchaiB.Supmonchai

MOS Transistor CapacitancesMOS Transistor Capacitances

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 49

B.SupmonchaiB.Supmonchai

Overlap CapacitancesOverlap Capacitances

ttoxox

n+ n+

Cross sectionCross section

LL

Gate oxide

xxdd xxdd

LL dd

Polysilicon gate

Top viewTop view

Gate-bulkGate-bulkoverlapoverlap

Source

n+

Drain

n+WW

€

Col=CoxxdW=CoW

Cgso=Cgdo=Col

€

Col=CoxxdW=CoW

Cgso=Cgdo=Col

€

Cox=εox

tox

(F/m(F/m22))

*C*Cfringefringe = (2 = (2oxox//) ln (1+) ln (1+TTpolypoly//ttoxox))

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 50

B.SupmonchaiB.Supmonchai

Gate-Channel CapacitancesGate-Channel Capacitances

Most important regions in digital design: saturation and cut-offMost important regions in digital design: saturation and cut-off

Cut-offCut-off

GG

SS DD

BB

ResistiveResistive

GG

SS DD

BB

SaturationSaturation

GG

SS DD

BB

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 51

B.SupmonchaiB.Supmonchai

WLCox

WLCox

2

2WLCox

3

CGC

CGCS

VDS /(VGS-VT)

CGCD

0 1

Capacitance as a function of the Capacitance as a function of the degree of saturationdegree of saturation

Variation of Gate-Channel CapacitancesVariation of Gate-Channel Capacitances

CGC

CGCS = CGCDCGCB

WLCox

WLCox

2

VGS

Capacitance as a function of VCapacitance as a function of VGSGS

(with V(with VDSDS = 0) = 0)

VT

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 52

B.SupmonchaiB.Supmonchai

Diffusion CapacitancesDiffusion Capacitances

€

Cdiff = CBottom + CSidewall = C1 + (C2 + C3 + C4 + C5)

WW

55

22

33

4411

GateGate

SiOSiO22

pp SubstrateSubstrate

n+n+ xxjj

LLSS

€

Cdiff = C jLSW + C jsw (2LS + W )

€

Cdiff = C jLSW + C jsw (2LS + W )

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 53

B.SupmonchaiB.Supmonchai

Junction Capacitance: RecapJunction Capacitance: Recap

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 54

B.SupmonchaiB.Supmonchai

Replace non-linear capacitance byReplace non-linear capacitance bylarge-signal equivalent linear capacitancelarge-signal equivalent linear capacitance

which displaceswhich displaces equal charge equal charge over voltage swing of interestover voltage swing of interest

Linearizing the Junction CapacitanceLinearizing the Junction Capacitance

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 55

B.SupmonchaiB.Supmonchai

MOS Transistor Capacitance: SummaryMOS Transistor Capacitance: Summary

GateGate

SourceSource DrainDrain

BodyBody

CCDBDB = = CCdiffdiffCCSBSB = = CCdiffdiff

CCGDGD = = CCgd gd + + CCgdogdoCCGSGS = = CCgs gs + + CCgsogso

CCGBGB = = CCgbgb

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 56

B.SupmonchaiB.Supmonchai

Capacitances in 0.25 Capacitances in 0.25 m CMOS processm CMOS process

Capacitance parameters of NMOS and PMOS transistors in 0.25 Capacitance parameters of NMOS and PMOS transistors in 0.25 m CMOS process.m CMOS process.

For an NMOS transistor with tox = 6 nm, L = 0.24 m, W = 0.36 m, LD = LS = 0.625 m

Total Gate Capacitance Total Gate Capacitance CCGG = = CCgg + 2 + 2CColol = 0.7 fF = 0.7 fF

CCSBSB = = CCDBDB = 0.89 fF = 0.89 fF

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 57

B.SupmonchaiB.Supmonchai

W

LD

Drain

Draincontact

Polysilicon gate

DS

G

RS RD

VGS,eff

Parasitic ResistanceParasitic Resistance

W

LD

Drain

Draincontact

Polysilicon gate

DS

G

RS RD

VGS,eff

€

RS,D =LS,D

WRsq + RC

RRsqsq = Sheet Resistance per square (20 - 100 ohms/sq.)= Sheet Resistance per square (20 - 100 ohms/sq.)

RRC C = Contact Resistance= Contact Resistance

Careless Layout may lead to resistances that severely degrade Careless Layout may lead to resistances that severely degrade device performance.device performance.

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 58

B.SupmonchaiB.Supmonchai

The DSM MOS TransistorThe DSM MOS Transistor Secondary Effects become more pronounce in

the deep-submicron transistor. Threshold VariationsThreshold Variations

Hot Carrier EffectsHot Carrier Effects

CMOS LatchupCMOS Latchup

Designing the circuits with all secondary effects taken into account is intractableintractable and results can be obscure.

Analyze with first-order model, then readjust the model with the help of CAD simulation tools.

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 59

B.SupmonchaiB.Supmonchai

Drain-induced barrier lowering Drain-induced barrier lowering or DIBL (for low or DIBL (for low LL) )

VVTT

Low Low VVDSDS thresholdthreshold

VVDSDS

Threshold VariationsThreshold Variations

LL

Long-channelLong-channelthresholdthreshold

Threshold as a function of the Threshold as a function of the length (for low length (for low VVDSDS))

VVTT

Short-channelShort-channelthresholdthreshold

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 60

B.SupmonchaiB.Supmonchai

Hot Carrier EffectsHot Carrier Effects Electrons become “hothot”, i.e. reaching a critical

high level of energy, under intense electric field which occurs when the channel is short.

EEcritcrit ≈ 10 ≈ 1044 V/m V/m

Hot electrons can leave the silicon and tunnel into the gate oxide.

Electrons trap in the gate oxide increase NMOS threshold and decrease PMOS threshold.

Hot electron phenomenon leads to a long-term reliability problem.

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 61

B.SupmonchaiB.Supmonchai

(a) Origin of latchup (b) Equivalent circuit

VDD

Rpsubs

Rnwell p-source

n-source

n+ n+p+ p+ p+ n+

p-substrateRpsubs

Rnwell

VDD

n-well

CMOS Latch-upCMOS Latch-up

(a) Origin of latchup (b) Equivalent circuit

VDD

Rpsubs

Rnwell p-source

n-source

n+ n+p+ p+ p+ n+

p-substrateRpsubs

Rnwell

VDD

n-well

Latchup causes positive feedback of the current until the circuit fails or burns out.

To avoid Latchup, RRnwellnwell and RRpsubspsubs should be minimized.

Devices carrying a lot of current need Guard RingsGuard Rings.

2102-545 Digital ICs2102-545 Digital ICs MOS Transistor Theory 62

B.SupmonchaiB.Supmonchai

Future PerspectivesFuture Perspectives

25 nm FINFET MOS transistor