An SEM/STM based nanoprobing and TEM study of breakdown...

Transcript of An SEM/STM based nanoprobing and TEM study of breakdown...

Microelectronics Reliability xxx (2015) xxx–xxx

MR-11722; No of Pages 5

Contents lists available at ScienceDirect

Microelectronics Reliability

j ourna l homepage: www.e lsev ie r .com/ locate /mr

An SEM/STM based nanoprobing and TEM study of breakdown locations in HfO2

dielectric stacks for failure analysis

K. Shubhakar a,⁎, M. Bosman b, O.A. Neucheva b, Y.C. Loke b, N. Raghavan a, R. Thamankar a, A. Ranjan a,S.J. O'Shea b, K.L. Pey a

a Singapore University of Technology and Design (SUTD), 138682, Singaporeb Institute of Materials Research and Engineering (IMRE), A*STAR, 3 Research Link, 117602, Singapore

⁎ Corresponding author.E-mail address: [email protected] (K. Shubhakar

http://dx.doi.org/10.1016/j.microrel.2015.07.0270026-2714/© 2015 Elsevier Ltd. All rights reserved.

Please cite this article as: K. Shubhakar, et al.,failure analysis, Microelectronics Reliability (

a b s t r a c t

a r t i c l e i n f oArticle history:Received 26 May 2015Received in revised form 25 June 2015Accepted 7 July 2015Available online xxxx

Keywords:High-kDielectricsNanoscaleFailureReliability

The formation of conductive percolation path is accompanied by dynamic changes in the electrical and materialproperty of the breakdown (BD) sites in high-κ (HK) dielectrics at the nanometer scale. It is therefore essential tostudy these BD events using high-precision nanoscale characterization tools to investigate the physical mecha-nisms of failure for advanced HK based devices. In this work, we carry out electrical nanoprobing of the HfO2

HK dielectric based nanoscale MOS devices for failure using a combined UHV-scanning electron microscopy/scanning tunneling microscopy (SEM/STM) combined system to locally stress HfO2/SiOx stacks, followed by fo-cussed ion-beam (FIB) sample preparation of these isolated failed devices and physical analysis of the BD sitesusing transmission electronmicroscopy (TEM). Our results clearly confirm themultiple physical phenomena as-sociatedwith localized BD, such as Si epitaxial growth, percolation of the dielectric layers, gate electrodematerialmigration and melting of the Si substrate at the BD region of HfO2/SiOx dielectric stacks. The physical analysis ofthe different BD sites is in good agreement with the previous observations on HfO2-based MOSFET devices. Thismethod of nanoprobing and correlated TEM analysis would be very useful in better localizing the BD defects forTEM studies thereby enhancing the success rate for failure defect detection and enabling better reliability study ofthe advanced nanoscale devices.

© 2015 Elsevier Ltd. All rights reserved.

1. Introduction

Reliability and failure analysis of advanced high-κ (HK) based CMOSdevices play a critical role in shortening the time to get these devicescommercialized. However, it is becoming increasingly difficult to identi-fy and locate the cause of device failure due to the complex structure ofthe devices and its scaling trend [1,2]. Physical analysis along withelectrical characterization of the device is very much essential to studythe root cause of device failures. Therefore, special techniques to locateand analyze the breakdown (BD) sites at a nanometer resolution are re-quired to investigate the nature of localized dielectric property changesin detail.

Here, we demonstrate a scanning electron microscopy/scanningtunneling microscopy (SEM/STM) enabled nanoprobing of HfO2 HK di-electric based nanoscale MOS devices by inducing soft and hard BD ofthe HfO2/SiOx dielectric stacks. Then, correlated physical analysis ofthese BD events using TEM is performed to study the nature of BDmechanisms.

).

An SEM/STMbased nanoprob2015), http://dx.doi.org/10.1

2. Experiments

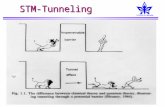

A schematic and an optical image of the SEM/STM equipment [3,4]with the STM tip over a sample and the SEM electron gun mountedabove the sample, are shown in Fig. 1(a) and (b), respectively. A pat-terned sample was prepared to aid and identify the breakdown loca-tions during the focused ion-beam (FIB) sample preparation aftersubjecting the selected devices for electrical stressing, and subsequentlyto navigate to the breakdown location during the TEManalysis. Triangu-lar electrode contacts of TiN/Ti (~3× 10−4 nm2 area)were patterned onthe blanket HfO2 dielectric to form individual devices for acceleratedstressing and initiating breakdown. The patterned samplewasmountedon a sample holder and transferred to the main UHV chamber of theSTM/SEM system to perform stressing of nanoscale MOS devices. Atop-view SEM micrograph of an area of interest containing patterneddevices is shown in Fig. 1(c). The STM tip was approached towardsthe sample to control the tunneling distance (b1 nm separation) witha voltage bias applied to the STM tip and performed localized rampedvoltage stressing (RVS) on the desired devices under substrate and tipinjection modes. Since the vacuum has a dielectric constant of “κ ~ 1”,a significant portion of the applied sample bias drops across the vacuumgap and hence the voltage drop across the HfO2/SiOx dielectric stack

ing and TEM study of breakdown locations in HfO2 dielectric stacks for016/j.microrel.2015.07.027

Fig. 1. (a) Schematic representation and (b) optical image of the SEM/STM system with STM tip placed over the patterned surface. (c) SEM micrograph of the sample showing e-beampatterned triangular gate electrodes on HfO2 dielectric.

2 K. Shubhakar et al. / Microelectronics Reliability xxx (2015) xxx–xxx

during RVS stressing is only around 40–50% of the applied samplebias [5].

Fig. 2(a) shows the STM tip placed over the gate electrode areaon the HfO2 dielectric during nanoprobing. The BD events with

Fig. 2. (a) SEMmicrograph showing an STM tip placed on top of the device (TiN/Ti/HfO2/SiOx stBD I–V characteristics of the devices under substrate injection.

Please cite this article as: K. Shubhakar, et al., An SEM/STMbased nanoprobfailure analysis, Microelectronics Reliability (2015), http://dx.doi.org/10.1

soft BD (SBD, Fig. 2(b)) (~3–4 times the initial leakage current at4 V), moderate BD (Fig. 2(c)) and hard BD (HBD, Fig. 2(d)) (~2–3 or-ders of the initial leakage current at 3 V) were performed on differ-ent devices. Moderate BD lies between these extremes.

ack). (b) Pre- and post-soft BD, (c) pre- and post-moderate BD and (d) pre- and post-hard

ing and TEM study of breakdown locations in HfO2 dielectric stacks for016/j.microrel.2015.07.027

Fig. 3. SEMmicrographs showing the FIB procedure after STM stressing of the devices to SBD/HBD. (b) Deposition of a protective layer at the area of interest for FIBmilling; (c) FIB thinningof the selected area on both sides; and (d) and (e) detached TEM lamella “attached” onto a W-probe with Pt-welding for TEM analysis.

3K. Shubhakar et al. / Microelectronics Reliability xxx (2015) xxx–xxx

After STM stressing experiments, the sample was removed from theSEM/STM and a thin protective layer of SiO2 (~1 nm) was depositedusing thermal evaporation method over the area of interest, containingthe BD devices as shown in Fig. 3(a). Subsequently, selected area wasisolated and prepared by FIB. Fig. 3(b)–(e) show the different stages of“pre-thinning” and “lift-off” in FIB sample preparation. The samplewas then subjected to TEM analysis to study the physical changes thatmay have occurred at the BD locations (which is easier to spot giventhe small sized, triangular patterned device structures).

Fig. 4. Cross-sectional TEMmicrographs of three devices after a soft BD (a) under tip injection,the devices exhibit no visible microstructural damage in the TEM micrographs.

Please cite this article as: K. Shubhakar, et al., An SEM/STMbased nanoprobfailure analysis, Microelectronics Reliability (2015), http://dx.doi.org/10.1

3. Results and discussion

3.1. Soft breakdown

Fig. 4 shows the cross-sectional TEMmicrographs of devices (TiN/Ti/HfO2/SiOx stack) subjected to a soft BD under tip injection (a) and sub-strate injection (b and c). Even though the dielectric suffers a soft BDand shows an increase in the leakage current, devices exhibit no visiblemicrostructural damage in the TEM micrographs. The percolation path

and (b, c) substrate injection. The soft BDwas observed in localized I–V characteristics, but

ing and TEM study of breakdown locations in HfO2 dielectric stacks for016/j.microrel.2015.07.027

4 K. Shubhakar et al. / Microelectronics Reliability xxx (2015) xxx–xxx

formed during the soft BD changes the chemical composition of the di-electric locally [6], but is invisible in the TEM diffraction mode. In thiscase, the dielectric stack can sustain and maintain the percolation leak-age path without inducing any physically observable damage.

3.2. Hard breakdown

Fig. 5(a) shows the cross-sectional TEM micrograph of the BD loca-tion of the device (marked by the dotted rectangle in the inset figure)stressed tomoderate BD under substrate injection. The TEMmicrographshows epitaxial Si hillocks extending from the Si substrate into theHfO2/SiOx dielectric stack. This is caused by DBIE at the BD site. It hasbeen reported that the DBIE formation is polarity dependent and nucle-ates in the direction of electron flow [7,8]. Here,DBIE nucleates fromSisubstrate towards HfO2 dielectric under substrate injection with theelectrons flowing from the Si substrate to the STM tip during the BD.

The TEMmicrograph also clearly shows the rupture of the SiOx inter-facial layer with the DBIE process. The change in the contrast of the Sisubstrate (darker regions) observed is believed to be due to metal ionsmigrating from the TiN/Ti electrode through the nearby BD path. Peyet al. [7] have reported that the primary driving force for the formationof DBIE is an enhanced thermal effect initiated by joule heating due tothe high current density surging through the percolation path duringthe BD event [7–9]. Fig. 5(b) shows a cross-sectional TEM micrographof another device stressed to HBD under substrate injection. Alongwith DBIE and rupture of the SiOx, amorphous regions of the Si substrateand HfO2 dielectric at the BD site were also observed, indicating in-creased BD hardness and increased structural disruption during theHBD. At the BD spot, thermal joule heating can raise the device temper-ature higher than the Si melting point [7–9], which leads to anamorphization of the Si substrate at the BD site, as highlighted inFig. 5(b). Due to high thermal joule heating an amorphization of theHfO2 also occurred near the BD region.

Fig. 5. Cross-sectional TEMmicrographs of two different failed devices under substrate in-jectionmode, showing (a)DBIE hillock from the Si substrate through theHfO2/SiOx dielec-tric stack, gate metal diffusion and rupture of SiOx (moderate BD). (b) In addition to DBIE,melting of the Si substrate and HfO2 dielectric were also observed, indicating higher im-pact of BD (hard BD) in this device. The insets show low magnification TEMmicrographsof the two failed devices.

Please cite this article as: K. Shubhakar, et al., An SEM/STMbased nanoprobfailure analysis, Microelectronics Reliability (2015), http://dx.doi.org/10.1

Similarly, stressing to BD under tip injection also lead to severemicrostructural damage of the HfO2/SiOx dielectric stacks. Fig. 6(a)shows a cross-sectional TEM micrograph of the BD spot (moderateBD) highlighted in dotted rectangle in the inset figure. The TEMmicro-graph showsmelting of a large area of the Si substrate near the BD area.The HfO2 dielectric remains intact because HfO2 has relatively a highermelting point than SiOx and Si [9]. Fig. 6(b) shows a cross-sectionalTEM micrograph of a HBD region highlighted in dotted rectangle inthe inset figure, displaying severe damage at the BD site with both rup-ture of the SiOx,melting of Si-substrate andHfO2 dielectric occuring. Thesevere damage is due to the creation of a high local temperature at theBD site due to thermal joule heating [9]. It was reported that the DBIEunder tip injectionwas observed from top electrode towards the dielec-tric region [6–8]. The results also suggest that the BD of SiOx dielectricoccurs initially, eventually triggering the overall BD of HfO2/SiOx dielec-tric stack, which is in good agreement with the earlier reports [10–12].

Previously reported failure mechanisms in MOSFET devices areshown in Fig. 7 [9,13,14]. The TEM micrograph of a device subjected tosoft BD shows no visible changes in the structure as shown inFig. 7(a). Fig. 7(b) shows the DBIE formed in the direction of electronflow at the BD site of a device under substrate injection. Fig. 7(c) and(d) show the metal migration, melting of substrate and dielectric BDin devices under gate injection and substrate injection, respectively[13,14]. The BD events observed in this work can be clearly correlatedto the BD phenomena observed in HfO2/SiOx based MOSFET devices[9,13,14] as highlighted in Fig. 7. Our results provide a direct proof toshow that the BD occurs locally and trigger the structural changessuch as DBIE, rupture of the dielectric stack, metal migration and local-ized melting of silicon in the substrate.

Fig. 6. Cross-sectional TEMmicrographs of two different failed devices under tip injectionmode showing, (a)melting of Si substrate and rupture of SiOx (moderate BD). (b) In addi-tion tomelting of Si substrate and rupture of SiOx, amorphous HfO2 dielectric was also ob-served indicating higher impact of BD (hard BD) in this device. The insets show lowmagnification TEMmicrographs of different failed devices.

ing and TEM study of breakdown locations in HfO2 dielectric stacks for016/j.microrel.2015.07.027

Fig. 7.Cross-sectional TEMmicrographs of HfO2 basedMOSFETdevices showing (a) soft BD, (b)DBIEunder substrate injection and (c,d)metalmigration and substratemelting effects afterBD under (c) gate injection, and (d) substrate injection after the BD [9,13,14].

5K. Shubhakar et al. / Microelectronics Reliability xxx (2015) xxx–xxx

4. Conclusions

We have demonstrated a new approach of localized electrical mea-surement and stressing using combined SEM/STM system with subse-quent physical analysis using TEM. This is shown to be an effectiveapproach to understand the physical and electrical nature of failures inadvance HK dielectric based electronic devices. We observed the phys-ical phenomena associated with localized BD using TEM, such as polar-ity dependent DBIE, rupture of dielectric layers, polarity independentgate electrode material migration and melting, and melting of the Sisubstrate at the breakdown region of HfO2/SiOx dielectric stacks. Thephysical analysis of the different BD sites is in good agreementwith pre-vious observations in HfO2-based MOSFET devices [9,13,14].Nanoprobing followed by TEM analysis could thus be an effective andpowerful technique in studying the advanced nanoscale devices forlogic and memory technology.

Acknowledgments

This work was funded by the research grant SUTD-ZJU RP1300104.The first author would like to thank Dr. X.A. Tran (previously withNTU Singapore) for fabricating blanket samples.

Please cite this article as: K. Shubhakar, et al., An SEM/STMbased nanoprobfailure analysis, Microelectronics Reliability (2015), http://dx.doi.org/10.1

References

[1] M. Porti, et al., Microelectron. Eng. 84 (2007) 1956–1959.[2] M. Lanza, et al., IEEE-TDMR 9 (2006) 529.[3] A. Kaneko, et al., Rev. Sci. Instrum. 76 (2005) 083709.[4] A. Wiessner, et al., Rev. Sci. Instrum. 68 (1997) 3790.[5] Y.C. Ong, et al., Appl. Phys. Lett. 91 (2007) 102905.[6] X. Li, et al., IEDM Tech. Digest 2008, pp. 779–782.[7] K.L. Pey, et al., IEEE proc. IRPS 2004, pp. 117–121.[8] M.K. Radhakrishnan, et al., Microelectron. Eng. 42 (2002) 565–571.[9] R. Ranjan, et al., IEEE proc. IRPS 2004, pp. 347–352.

[10] M. Lanza, et al., Appl. Phys. Lett. 100 (2012) 123508.[11] N. Raghavan, et al., IEEE International Reliability Physics Symposium (IRPS) 2012,

p. 6A.1.1-11.[12] K. Shubhakar, et al., Microelectron. Eng. 109 (2013) 364–369.[13] R. Ranjan, et al., IEDM Tech. Digest 2004, pp. 1–4.[14] R. Ranjan, et al., Appl. Phys. Lett. 87 (2005) 242907.

ing and TEM study of breakdown locations in HfO2 dielectric stacks for016/j.microrel.2015.07.027