– 1 – A circuit-level simulation approach for VCSEL-based optical interconnect System level...

-

Upload

herbert-andrews -

Category

Documents

-

view

222 -

download

1

Transcript of – 1 – A circuit-level simulation approach for VCSEL-based optical interconnect System level...

A circuit-level simulation approach for VCSEL-based optical interconnect

– 1 –

System level behaviour of System level behaviour of VCSEL-based optical VCSEL-based optical

interconnects:interconnects:a circuit-level simulation a circuit-level simulation

approachapproachMichiel De WildeElectronics and Information Systems dept.

Olivier RitsInformation Technology dept.

Ghent University — IMEC, BelgiumIST project “Interconnect by

Optics”

A circuit-level simulation approach for VCSEL-based optical interconnect

– 2 –

Optical interconnect rationaleOptical interconnect rationale

(ww

w.in

tel.c

om

)

A circuit-level simulation approach for VCSEL-based optical interconnect

– 3 –

Optical interconnect rationale Optical interconnect rationale (2)(2)

0101

1011

01010011

10110010

• Packet routers

• Parallel and distributed processing systems

A circuit-level simulation approach for VCSEL-based optical interconnect

– 4 –

Optical interconnect rationale Optical interconnect rationale (3)(3)

AL

Wire capacitance + resistance & skin effect bit-rate limit:

s/bits10 217

LA

B

(Miller-Özaktas)

A circuit-level simulation approach for VCSEL-based optical interconnect

– 5 –

Optical interconnect rationale Optical interconnect rationale (4)(4)

• Physical solution: use of optics– No electromagnetic wave phenomena

(crosstalk)– Losses barely sensitive to distance & frequency– Potential to scale much better than wires

• Advantage in using optical interconnectsfor ever decreasing distances– From chip to chip: onboard, and board to board

A circuit-level simulation approach for VCSEL-based optical interconnect

– 6 –

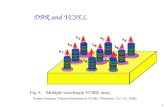

VCSEL-based parallel optical I/OVCSEL-based parallel optical I/O

Hybridised 2D VCSEL array Hybridised 2D photodetector array

Parallel waveguides (e.g. POF flexes)

Multi-waveguide connectors (e.g. overmoulded POF bundles)

silicon

optical devices

A circuit-level simulation approach for VCSEL-based optical interconnect

– 7 –

Design spaceDesign space

Waveguide & interconnection technology(ribbons, flexes, planar integration)

VCSEL technology family Photodetector technology family

Chip packaging technology

for optical access

CMOS hybridisation

Digital encoding & clock recovery systems

Interface circuits of electro-optical devicesTX

A circuit-level simulation approach for VCSEL-based optical interconnect

– 8 –

Design space (2)Design space (2)

• Continuously-valued design parameters as well– λ, operating currents, numerical aperture…

• Choices affect system-level characteristics– Technological feasibility (interoperability, yield)

– Timing characteristics (delay, skew)

– Reliability(spikes, power temperature, misalignment)

– Monetary cost

A circuit-level simulation approach for VCSEL-based optical interconnect

– 9 –

Increase of numerical aperture

Better coupling

Worse couplingLess losses

• Tradeoffs between choices

– Multi-objective

– Counteracting effects

Design space explorationDesign space exploration

VCSEL

photodiode bend

• Find: systematic way of making choices= design methodology

• Goal: formalized into a design tool1. The designer states system-level characteristics

2. The design tool assists in making product and parameter choices

A circuit-level simulation approach for VCSEL-based optical interconnect

– 10 –

Design methodology Design methodology developmentdevelopment

VCSEL drive current

Photodetector sensitivity

Fiber numerical aperture

Interface technology…

Product and parameter choices

Power dissipationLink latency

Link reliabilityLink skew

Implementation cost

System-level link properties

…

STAGE 1predict

STAGE 2Construct multi-objective solution

(e.g.) link bit error rate

(e.g.) total power dissipation

Infeasibledesign region

Sub-optimaldesigns

Pareto-optimaldesigns

STAGE 3target

A circuit-level simulation approach for VCSEL-based optical interconnect

– 11 –

Design methodology focus: step Design methodology focus: step 11

Predicting effect of design Predicting effect of design alternativesalternatives

• Issues for direct estimation(e.g. from tabular data)– Difficult prediction of noise/variation propagation

– Dynamic multi-domain interactions (electrical, optical, thermal)

• Implement framework for time-domain link simulation to– Estimate system-level properties for various setups

– Verify behaviour of optical interconnect within a digital system (mixed-signal simulation)

A circuit-level simulation approach for VCSEL-based optical interconnect

– 12 –

Simulation framework:Simulation framework:link “building block” modelslink “building block” models

• Circuit-level behavioural modelsinstead of physical models– Only time-dependent equations

– No spatial dependency

• Mixed-signal Verilog-AMS (or VHDL-AMS)instead of SPICE– Direct expression of differential equations

– Native support for signals in different domains

A circuit-level simulation approach for VCSEL-based optical interconnect

– 13 –

Example: photodiode modelExample: photodiode model

module pin_photodiode(in,anode,cathode); input in; inout anode, cathode; power in; electrical anode, cathode; parameter real Cdep=0, Cbo=0, Rbas=0, Resp=0, Id=0; parameter real pole=-1/(Cdep*Rbas); parameter real laplace_coeff_0=Cdep+Cbo; parameter real laplace_coeff_1=Cdep*Cbo*Rbas; charge rc; analog begin I(cathode,anode) <+ laplace_zp(Resp*Pwr(in)+Id,{},{pole,0}); Q(rc) <+ laplace_np(V(cathode,anode),{laplace_coeff_0,laplace_coeff_1},{pole,0}); endendmodule

•Terminals•Model parameters•Equations describing internal state and outputs

A circuit-level simulation approach for VCSEL-based optical interconnect

– 14 –

Simulation framework:Simulation framework:model hierarchymodel hierarchy

Behavioural models (Verilog-AMS) – with symbolic parameters

DriverDriver VCSEL #1VCSEL #1 VCSEL #2VCSEL #2 Optical pathOptical path PhotodetectorPhotodetector ReceiverReceiver

Model instantations with parameters (Spectre netlist files)

Driver #1Driver #1 VCSEL #1VCSEL #1 #2#2 Optical pathOptical path PhotodetectorPhotodetector ReceiverReceiver#2#2

Complete interconnect specifications (Spectre netlist files)

Interconnect specification #1Interconnect specification #1 Interconnect specification #2Interconnect specification #2

A circuit-level simulation approach for VCSEL-based optical interconnect

– 15 –

Driver/receiver modelDriver/receiver model

• Normal analog electrical circuits• IP protection: no real circuit provided

• Alternative: parameterised flowchart

Receiver flowchart

Transimpedance preamplifier Postamplifier

Decision circuit

Equaliser

Limiting amplifier

Photocurrentinput

Digital output

A circuit-level simulation approach for VCSEL-based optical interconnect

– 16 –

VCSEL modelVCSEL model• Nonlinear 1st order differential equation system

• Issue: getting an initial solution

VCSEL current

Output power

Bad steady state solution

Steady state solution

• VCSEL characterisation is hard

(M.X

. Ju

ng

o)

A circuit-level simulation approach for VCSEL-based optical interconnect

– 17 –

Fiber-based optical pathFiber-based optical path

• TBD: Statistical modelling of misalignment

VCSELadacentphotodetector

photodetectoradjacent

VCSEL

Macrobendlosses

Absorption

Connectorlosses & crosstalk

VCSEL-fibercoupling losses

VCSEL-fibercrosstalk

Fiber-detectorcrosstalk

& coupling losses

• Coupling coefficients for losses & crosstalk

• Abstraction of dispersion (short distance)

A circuit-level simulation approach for VCSEL-based optical interconnect

– 18 –

Fiber bend lossesFiber bend losses

• TBD: Take into account that the mode distributions do not directly stabilise after a bend

• Currently: accumulate bend lossesusing a table obtained by raytracing (H. Lambrecht)

90° bendX axis: NA fiberY axis: bending radiusBlue color = high losses

A circuit-level simulation approach for VCSEL-based optical interconnect

– 19 –

Simulation featuresSimulation features

• Process corner simulation– Best-case or worst-case value for all model parameters– Lower and upper boundaries are not very tight

• Statistical simulation (partly TBD)– Time-invariable statistics:

• Inter-process & intra-process variations• Misalignment

– Dynamic statistics:• Noise (e.g. VCSEL RIN noise)• Effects like power supply spikes

A circuit-level simulation approach for VCSEL-based optical interconnect

– 20 –

Simulation example: transientSimulation example: transient

1 link with 10dB attenuation in the optical path

(exaggerated VCSEL model parameters)

A circuit-level simulation approach for VCSEL-based optical interconnect

– 21 –

ConclusionConclusion

• Framework for simulation of guided wave optical interconnect systems– Design methodology development: enable

prediction of system-level interconnect characteristics

– Mixed-signal simulation of optical interconnect within a digital system

• Operational, but not yet mature– Simulation is doable, characterisation is hard

(especially statistical characterisation)

A circuit-level simulation approach for VCSEL-based optical interconnect

– 22 –

AcknowledgementsAcknowledgements

• IST Interconnect by Optics Project

– Helix AG: driver/receiver block diagrams

– Avalon Photonics: VCSEL measurements

– Hannes Lambrecht (Ghent University, IMEC-

INTEC): macrobend losses

• Fund for Scientific Research – Flanders

(Belgium) (F.W.O.)

– Research assistantship

A circuit-level simulation approach for VCSEL-based optical interconnect

– 23 –

Thermal effectsThermal effects

• Temperatures are difficult to predict• VCSELs are very temperature sensitive• Operating temperature of up to 85°C

• Temperature distribution in the simulation– Simulator implementation: not difficult– TBD: Estimate expected temperature

differences in a VCSEL array