Vlsi design notes(1st unit) according to vtu syllabus.(BE)

-

Upload

instrumentationvtu -

Category

Engineering

-

view

1.005 -

download

1

description

Transcript of Vlsi design notes(1st unit) according to vtu syllabus.(BE)

1

VLSI Design

UNIT -1

Introduction to MOS technology

Moore’s law

Speed- power performance

nMos fabrication

CMOS fabrication

n-well process

p-well process

BiCMOS

Comparison of bipolar and CMOS

2

1 INTRODUCTION

Integrated circuit (IC):- an IC is a combination of interconnection circuit

elements on a continuous substrate.

Substrate:- substrate is a supporting material upon which an IC is fabricated.

Wafer:- a wafer is a basic physical unit used in processing. It usually

contains large number of identical IC’s.

Transistor was invented in 1947.

The very first IC emerged at the beginning of 1960.

Chip

Wafer

Generation of IC’s

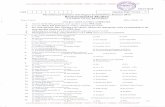

Year generation number of transistors typical products

1961 SSI 10-100 logic gates, flip-flop

1966 MSI 100-1000 counters, mux, adders

1971 LSI 1000-20,000 8bit μps, RAM, ROM

1980 VLSI 20,000-106(1 million) 16-32 bit μps, DRAM

1990 ULSI 1-10 million DSPs, smart sensor

2000 GSI >10million ASIC

2 Moore’s first law:

Predicted

Actual

1961 1964 1967 1970 1973 1994 1997

It states that the number of transistors per chip doubles every 18months

3

3 Speed/power performance of available technologies:

In order to improve the through put rate it will be necessary to improve the

technology both in term of scaling and processing, and through the

incorporation of other enhancements such as BICMOS to CMOS.

Above 100million instruction/sec, one must look to other technology like

gallium Arsenide (GaAs) based technology.

GaAs in combination with silicon will provide designer some exciting

possibilities.

4 Basic MOS transistor symbol

E-MOSFET DE-MOSFET

DE-MOSFET conducts when Vgs=0, Vgs=+ve and Vgs=-ve as a channel

exist between source(S) and drain (D).

E-MOSFET does not conduct when Vgs=0.

4

For E-MOSFET For DE-MOSFET

There are 2 types of nMOS

1. Enhancement mode transistor (E-MOSFET)

2. Depletion mode transistor(DE-MOSFET)

In depletion mode channel is established between S and D during

manufacturing process itself by implanting suitable impurities. Therefore

DE-MOSFET conducts when Vgs=0.

In E-MOSFET there is no channel between S and D. therefore device is

not conducting when Vgs=0.

a. nMOS Enhancement mode transistor

5

b. nMOS Depletion mode transistor

c. pMOS Enhancement mode transistor

d. pMOS Depletion mode transistor

Enhancement mode transistor action:

In nMOS enhancement mode transistor, there exist no physical layer

between source(S) and drain (D).

A minimum voltage level of threshold voltage (Vt) must be provided

between source(S) and gate (G) to establish channel between S and D.

Enhancement mode device operates under 3 set of conditions.

6

1. When Vgs > Vt and drain to source voltage Vds=0. There is a channel

between S and D, but no current is flowing in channel. Transistor is in

cut-off region.

2. When Vgs>Vt and Vds<Vgs-Vt, current flows from D to S. it operates

in non-saturation region.

As Vds increase current flow increases the current increases the

voltage drop increases in the channel. As a results between gate and

channel varies with distance along the channel and is maximum at

source end (as Vds is +ve)

3. When Vds>Vgs-Vt, the transistor operates ib saturates region

Here depletion region increases as voltage drops in maximum at drain

end and cause pinch off at channel. Now constant current flows from

D to S as channel exhibits high resistance.

For enhancement mode device Vt=0.2Vdd

If VDD=5v then Vt=1v.

Depletion mode transistor action:

Here channel is established between S and D during the construction of

transistor so when Vgs=0, the current flows between S and D.

1. When Vgs=0 and Vds=0, there exists a channel between S and D but not

current flows from D to S.

7

2. When Vgs>=0 and Vds<Vgs-Vt, current will flow from D toS.as the

current flows, there will voltage drop.

3. When Vgs>=0 and Vds>Vgs-Vt, the voltage drop in channel near drain is

maximum and equal to pinch off voltage. The transistor here operates in

saturation region, constant flow from D to S.

Vtd is typically <-0.8Vdd.

5 nMOS fabrication

Processing is carried out on a thin wafer cut from a single crustal of

silicon of high purity into which the required p-impurities are introducer.

The wafer is typically 75-150mm in diameter and 0.4mm thick. The

substrate is doped with boron to give impurity concentration of 1015

/cm3

to 1016

/cm3, giving the resistivity of 25Ωcm to 2Ωcm.

8

A silicon dioxide (Sio2) layer of typically 1µm thick is grown all over the

surface of the wafer, this protective layer act as barrier to dopants during

processing.

Photo resist is deposited on the wafer to get even distribution required

thickness.

The photo resist layer is exposed to UV light by means of required mask.

The exposed areas UV are polymerized (hardened) and unexposed areas

remain unaffected.

These areas (hardened areas) are etched away along underlying Sio2 so

that the wafer surface is exposed in the window defined by mask.

9

The photo resist is removed and thin layer of Sio2 is grown over the entire

surface. Then polysilicon is deposition on top of this to form the gate

structure. The polysilicon layer consists of heavily doped polysilicon

deposition by chemical vapour deposition (CVD).

Thin oxide is removed to expose areas into which n-type of impurities are

to be diffused to form S and D. diffusion is achieved by heating the wafer

to high temperature and passing a gas containing the desire n- impurity

over the surface. Polysilicon and thin oxide act as masks during diffusion

called as “self aligning”.

Sio2 is grown over all and is masked with photoresist and etched to

exposed selected areas of gate, drain and source areas where connections

are to be made.

10

.

Metal of 1µm thickness is deposited overall the chip’s surface. this metal

layer is then masked and etched to form the required interconnected

pattern

6 CMOS fabrication:

CMOS can be fabricated by P-well, n-well and twin tub process.

6.1 P-well process

11

On n-type substrate, p-well is diffused by suitable masking. The depth of

p-well is 4-5 µm.

p-well doping concentration will affect the threshold voltage and

breakdown voltage of n-transistor, hence p-well diffusion must be out

with care.

To achieve low threshold voltage, we need either deep-well diffusion or

high well resistivity. But limitation is that chip area becomes large due to

lateral diffusion.

Within the parent n-substrate, the p-well act as a substrate for the n

device. As there are two substrate, these devices are to be electrically

isolated.

Due to two substrate, it require two substrate connections VDD and Vss

that are connection by means of n+ and p

+ diffusion.

In all other respects-masking, patterning and diffusion process are similar to

that of nMOS fabrication.

Processing steps are:

Mask 1: p-well diffusion in n-substrate.

Mask 2: defines thin oxide region, namely those areas where the thick oxide

is stripped and thin oxide is grown to accommodate p- and n- transistor and

wires.

Mask 3: polysilicon layer is deposited on thin oxide and then patterned.

Mask 4: P+ mask is used to define the area where p-diffusion is to take place.

12

Mask 5: p+

mask is used for n-diffusion.

Mask 6: contact cut are defined.

Mask 7: metal layer pattern is defined.

Mask 8: passivation (over glass) layer is applied.

Fig:-CMOS p-well inverter showing VDD and VSS substrate connection.

6.2 n-well process:

n-well is superior to p-well because of the low substrate biase effects on

transistor threshold and lower capacitance associated with source and drain

region

Fig: cross sectional view of n-well CMOS inverter.

N-well is diffusion into the p-substrate.

Within the parental p-substrate, n-well act as a substrate to diffuse p-

device.

Two substrates two separate substrate connection i.e VDD and Vss for n+

and p+

respectively.

13

Main steps in n-well process:

Fig: main steps in typical n-well process.

Note: refer figure 1.13, 1.14, 1.15 and1.16 from textbook.

7 BiCMOS technology

The load driving capabilities of MOS transistor is less, due to the limited

current sourcing and current sinking abilities of both p and n transistors.

Bipolar transistor provide higher gain, better noise and high frequency

characteristics than MOS transistors.

Bipolar can be combined with the CMOS technology to construct higher

speed devices i.e (BiCMOS devices).

Formation of n-well region

Define nMOS and pMOS active areas

Field and gate oxidations (thin oxide)

Form and pattern polysilicon

P+

diffusion

Deposit and pattern metallization

n+

diffusion

Contact cuts

Over glass with cuts and bonding pads

14

Application of BiCMOS in subsystems like ALU,ROM, barrel shifter etc

is not always a way of improving speed because most gate in such

structures do not have to drive large capacitive loads, so here BiCMOS

arrangements give no speed advantages.

BiCMOS devices speed up VLSI circuits

Example: Pentium, Pentium pro, super SPARC, RF oscillator.

7.1 Comparison between bipolar and CMOS technology

CMOS technology bipolar technology

Low static power dissipation high static power dissipation

High input impedance low input impedance

High packing density low packing density

Bidirectional capability unidirectional capability

Low output driver current high output driver current

Low trans conductance high trans conductance

High delay sensitivity to load low delay sensitivity to load

Scalable threshold voltage