UM EECS 270 Spring 2011 – Taken from Dr.Karem Sakallah Logic Synthesis: From Specs to Circuits...

-

Upload

archibald-wells -

Category

Documents

-

view

214 -

download

1

Transcript of UM EECS 270 Spring 2011 – Taken from Dr.Karem Sakallah Logic Synthesis: From Specs to Circuits...

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

Logic Synthesis:From Specs to Circuits

• Implementation Styles– Random– Regular

• Optimization Criteria– Area (roughly number of transistors)– Delay (roughly number of gates on longest circuit path)– Testability– Power consumption

• 2-Level Synthesis– Classical (Exact)– Heuristic (Non-Exact)

• Multilevel Synthesis

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

Logic Expressions Circuits

f stv stwx styz uv uwx uyz f st u wx yz v

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

2-Level Circuits• Assumptions:

– Inputs are available in both true and complemented forms(reasonable assumption: FF outputs are available in both phases)

– Gates have no fan-in or fan-out restrictions(unreasonable assumption: typically FI < 4, FO < 6)

• Correspond to SOP or POS forms of a switching function:– SOP AND/OR (NAND/NAND)– POS OR/AND (NOR/NOR)

• # of 1st level AND (OR) gates = # of nontrivial product (sum) terms• Fan-in of 2nd level OR (AND) gate = total # of product (sum) terms• Usually implemented using regular structures:

– Read-Only Memories (ROMs)– Programmable Logic Arrays (PLAs)

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

AND/OR NAND/NAND

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

Terminology Review

• Literal: A variable or its complement– Ex:

• Product Term: A single literal or a product of two or more literals– Ex:

• Sum of Products: A sum of product terms• Minterm: A product term where every variable of the

function appears once as a literal (i.e., in complemented or uncomplemented form)

• Canonical Sum: A sum of minterms. Every function has a unique canonical sum

BYX ,,

ZYXWCBAXY ,,

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

Canonical Sum Representations

• Canonical sum uniquely defines a function, but can be long. A minterm list is a list of the row numbers of minterms included in the canonical sum.– Also known as the on-set

• Three canonical ways of representing functions– truth table– canonical sum– minterm list

B C F0 00 11 01 1

0010

0 00 11 01 1

0011

00001111

A

CBA

F,,

)7,6,2(

01234567

Row #

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

Canonical Product Representation• Sum Term: A single literal or

a sum of two or more literals• Product of Sums: A product

of sum terms• Maxterm: A sum term where

every variable in the function appears once as a literal

• Canonical Product: A product of maxterms

• Maxterm List: A list of the truth table row numbers of the maxterms of a function– Also known as the off-set

B C F0 00 11 01 1

0111

0 00 11 01 1

1010

00001111

A01234567

Row #Maxterms

A+B+C

A+B+C

A+B+C

A+B+C

A+B+C

A+B+C

A+B+C

A+B+C

Maxterms

A+B+C

A+B+C

A+B+C

A+B+C

A+B+C

A+B+C

A+B+C

A+B+C

))()(( CBACBACBAF

)7,5,0(,, CBAF

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

B C F0 00 11 01 1

0010

0 00 11 01 1

0011

00001111

A

ABCCABCBAF

Canonical Sum:

Minterms

ABC

ABC

ABC

ABC

ABC

ABC

ABC

ABC

Minterms

ABC

ABC

ABC

ABC

ABC

ABC

ABC

ABC

A

CB

A

CB

A

CB

F

Circuit:

Cost of implementation: 3 3-input ANDs (9 literals) + 1 3-input OR

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

• Canonical sum is not (in general) the least-cost way to implement a function

• How to get smaller circuits?– One way: Switching algebra theorems!

Cost: 2 2-input ANDs (4 literals) + 1 2-input OR!

Applying theorems directly becomes more difficult as canonical sums get bigger…

– Another (perhaps easier) way: Karnaugh maps

ABCCABCBAF

)()( ABCCABCABCBA

ABCB

C

B

F

A

B

ABCDDABCDCABDCABDCBADCBABCDADCBADCBADCBADCBADCBAF

Idempotency

Combining

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

Karnaugh Maps• Karnaugh map (K-map) is a 2D representation of truth table that

present a graphical way to find the minimal SOP (or POS) of a function– Each cell represents a minterm

– Cells with a common edge are logically adjacent (i.e., they will combine)

– K-map is actually a doughnut: outside edges connect

B C F0 00 11 01 1

0111

0 00 11 01 1

0001

00001111

A

1 1 1 0

0 1 0 0

00 01 11 10

0

1

ABC

F

We’ll omit 0s for clarity

1 1 1

1

00 01 11 10

0

1

ABC

F

m0

00 01 11 10

0

1

ABC

F

m1

m2

m3

m6

m7

m4

m5

B C F0 00 11 01 1

m0

m1

m2

m3

0 00 11 01 1

m4

m5

m6

m7

00001111

A11 and 10 are swapped!

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

• Key K-map property: adjacent cells represent minterms that will combine!

Reading product term:

X is 1 in both minterms: X

Y is 0 in both minterms: YZ is 1 in one minterm and 0 in the other: Z

does not appear in product term

ZYX

F,,

)5,4,2,1(

ZYXZYYXF

Minimal SOP:

00 01 11 10

0

1

XYZ

0

1

2

3

4

5

6

71

1 1

1

YZ

XYZ

Combining: XYZ + XYZ = XY

Minterm XYZ

Minterm XYZ

Product term: XY

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

Four Variable K-map

ZYXW

F,,,

)15,14,7,5,4,3,2,1,0(

m0

m1

m3

m2

m4

m5

m7

m6

m8

m9

m11

m10

m12

m13

m15

m14

00 01 11 10WX

YZ

00

01

11

10

F

12

13

15

14

11

10

0

1

3

2

4

5

7

6

8

91 1

1 1

00 01 11 10WX

YZ

1 1

1 1 1

00

01

11

10

F

How do we find the product terms to include in the minimal SOP?

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

• K-map “rules”– Only circle adjacent cells (remember edges are adjacent!)

– Only circle groups that are powers of 2 (1, 2, 4, 8, …)

– Only circle 1-cells

1

1

00 01 11 10

0

1

ABC

1

1

00 01 11 10

0

1

ABC

1 1

1 1

00 01 11 10

0

1

ABC

1

1 1

00 01 11 10

0

1

ABC

1 1

1 1

00 01 11 10

0

1

ABC

1 1

00 01 11 10

0

1

ABC

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

Covering

g

= input combinationsfor which g outputs 1

Space of all 2n inputcombinations (minterms)

f

= input combinationsfor which f outputs 1

f covers gif f=1 whenever g=1

f ≥ g

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

Implicants

g

= input combinationsfor which g outputs 1

h f

= input combinationsfor which f outputs 1

If g is a product term & g≤f,Then g is an implicant of f.

Space of all 2n inputcombinations (minterms)

= input combinationsfor which h outputs 1

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

Prime Implicants• Removing a literal from any product term (any implicant)

makes it cover twice as many minterms.– Removing a literal “grows” the term– ex. 3 variables: ab’c covers 1 minterm

ab’ ac each cover 2

mintermsb’c

f ab’c

ab’

ac

b’cAny way of removing a literalmakes ab’c no longer imply f.

So ab’c is a prime implicant of f.

Any way of removing a literalmakes ab’c no longer imply f.

So ab’c is a prime implicant of f.

ab’c is an implicant of f.

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

Implicant: Any product term that implies a function F (i.e., if, for some input combination, product term P = 1, then F = 1 for the same input combination)

Prime Implicant: An implicant such that if one literal is removed, the resulting product term no longer implies F

Essential Prime Implicant: A prime implicant that covers a minterm that is not covered by any other prime implicants

1 1

00 01 11 10WX

YZ

1 1

1 1 1

00

01

11

10

Theorem: The minimal SOP of a function is a sum of prime implicants

1 1

00 01 11 10WX

YZ

1 1

1 1 1

00

01

11

10

1 1

00 01 11 10WX

YZ

1 1

1 1 1

00

01

11

10

These are only a few of the implicants of this function…

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

K-map minimization procedure:1) Find all prime implicants (PIs)2) Determine which PIs are essential

prime implicants (EPIs) and include those in the minimal SOP. Remove all EPIs and the 1-cells they cover

3) Remove all PIs that are eclipsed (dominated)

– Prime implicant X eclipses prime implicant Y if X covers at least all of the 1-cells that Y covers

4) Find secondary EPIs, include secondary-EPIs in minimal SOP, and remove 1-cells they cover. If there are any 1-cells remaining, goto step 3

1 1 1

1 1

00 01 11 10WX

YZ

1

1 1 1

00

01

11

10

F

• Note: If, at any stage, there are no remaining EPIs, all remaining combinations of PIs must be considered for the minimal SOP

1

00 01 11 10WX

YZ

1 1

00

01

11

10

F

1

00 01 11 10WX

YZ

1 1

00

01

11

10

F

XWYWF

ZXWWYZXWYWF

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

In Class ExerciseFind the minimal SOP for the following function:

),,,(

)15,14,12,7,5,4,1(ZYXW

F

1 1

1 1

00 01 11 10WX

YZ

1

1 1

00

01

11

10

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

In Class ExerciseFind the minimal SOP for the following function:

),,,(

)15,14,12,7,5,4,1(ZYXW

F

The minimal SOP may not always be unique!

1 1

1 1

00 01 11 10WX

YZ

1

1 1

00

01

11

10

1 1

00 01 11 10WX

YZ

1

1 1

00

01

11

10

1 1

00 01 11 10WX

YZ

1

1 1

00

01

11

10

00 01 11 10WX

YZ

1

00

01

11

10

ZYWF XYZZYXZYWF

WXYXYZZYXZYWF

ZWXXYZZYXZYWF or

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

Using K-maps to find minimal POS

1) Find minimal SOP for F

2) Use DeMorgan’s to get minimal POS for F

1 1

1 1

00 01 11 10WX

YZ

1 1 1

1 1

00

01

11

10

F

1 1

1 1

00 01 11 10WX

YZ

1

1 1

00

01

11

10

F

ZYXW

F,,,

)12,11,9,6,4,3,1(

ZWYXZZXF

))()(( ZYWZXZXF

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

Don’t Care Outputs• Sometimes when designing a function, some input combinations may never

occur

• Design Example - Encoder: Converts 3-bit one-hot code to equivalent binary code

d dothers

How to assign unused input combinations?

0 0others

6 literals 6 literals

4 literals 4 literals

Don’t cares allow us to easily assign 1 or 0 to unused input combinations in order to minimize implementation cost!

i1 i0 o1

0 00 11 00 0

0011

0001

i2 o0

0101

1 1

00 01 11 10

0

1

i2i1i0

o1

1

1

00 01 11 10

0

1

i0

o0i2i1

d d d

1 d 1

00 01 11 10

0

1

o1

1 d d d

d 1

00 01 11 10

0

1

o0i2i1

i0i2i1

i0

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

• When finding minimal SOP with don’t cares:– Use d cells to make PIs as large as possible– No prime implicant should include only d’s– Only 1-cells should be considered when finding minimal

covering set of PIs

ZYXW

dF,,,

)14,13,12,8()15,11,7,5,1(

1 1 d

d d

00 01 11 10WX

YZ

d

1 1 1

00

01

11

10

F

WYZZYWXZF WX

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

Minimal SOP vs. Minimal POS w/ Don’t Cares

• FSOP has a smaller literal cost than FPOS

• WXYZ = 1110: • When don’t cares are involved, in general the minimal SOP for a function

is not equal to the minimal POS for the function– But that’s ok! We don’t care about the input combinations where they differ…

ZWYZWXFSOP YXWZYZWF ))()(( YXWZYZWFPOS

1 1 1

d 1

00 01 11 10WX

YZ

d

d d 1 1

00

01

11

10

F

1

d 1 1

00 01 11 10WX

YZ

1 1 d 1

d d

00

01

11

10

F

FSOP(1,1,1,0) = 1, FPOS(1,1,1,0) = 0 → FSOP ≠ FPOS!!!

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

5 Variable K-Maps

• Every cell is adjacent to 5 other cells

00 01 11 10BC

DE

00

01

11

10

F

A = 1

00 01 11 10BC

DE

00

01

11

10

F

A = 0

Keep life simple by splitting on the MSB!

A = 1

A = 0

m0

m1

m3

m2

m4

m5

m7

m6

m8

m9

m11

m10

m12

m13

m15

m14

m16

m17

m19

m18

m20

m21

m23

m22

m28

m29

m31

m30

m24

m25

m27

m26

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

EDCBA

F,,,,

)31,29,19,17,15,3,1(

ABCEBCDEECBF

00 01 11 10BC

DE

00

01

11

10

A = 1

1

1

1

1

00 01 11 10BC

DE

00

01

11

10

F

1

1

1

A = 0

12

13

15

14

11

10

0

1

3

2

4

5

7

6

8

9

28

29

31

30

27

26

16

17

19

18

20

21

23

22

24

25

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

Tabular Generation of Prime Implicants(Quine-McCluskey Procedure)

• Main Theorems:– Adjacency: x’ p + x p = p (create “larger” implicants)– Absorption: p + x p = p (delete subsumed implicants)

• Procedure:– Arrange product terms in groups such that all terms in one group

have the same number of 1s in their binary representation, their Group Index

– Starting from minterms, arrange groups in ascending-index order– Apply adjacency theorem to product terms from adjacent groups

only– Remove subsumed product terms using absorption theorem

• Product term representation: p = pnpn-1 … p2p1

where 0 if ith variable appears complemented

1 if ith variable appears uncomplemented

if ith variable does not appearip

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

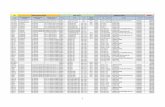

QM Example

EDCBAF

,,,,)31,29,19,17,15,3,1(

index minterm A B C D E

1 1 0 0 0 0 1

2 3 0 0 0 1 1

17 1 0 0 0 1

3 19 1 0 0 1 1

4 15 0 1 1 1 1

29 1 1 1 0 1

5 31 1 1 1 1 1

pterm A B C D E

UM

EE

CS

27

0 S

prin

g 2

01

1 –

Ta

ken

fro

m D

r.K

are

m S

aka

llah

QM Example

EDCBAF

,,,,)31,29,19,17,15,3,1(

index minterm A B C D E

1 1 0 0 0 0 1

2 3 0 0 0 1 1

17 1 0 0 0 1

3 19 1 0 0 1 1

4 15 0 1 1 1 1

29 1 1 1 0 1

5 31 1 1 1 1 1

pterm A B C D E

1,3 0 0 0 - 1

1,17 - 0 0 0 1

3,19 - 0 0 1 1

17,19 1 0 0 - 1

15,31 - 1 1 1 1

29,31 1 1 1 - 1

![Motivation IEEE performance - EECS€¢ Motivation • IEEE 802.11a Specs ... (V GS‐V TH) ... Circuit System, vol2 pp.1172‐1174, 1998 • [4]Kumar Munusamy and Zubaida Yusoff ,”](https://static.fdocuments.net/doc/165x107/5ae954bf7f8b9ad73f8bb78e/motivation-ieee-performance-motivation-ieee-80211a-specs-v-gsv.jpg)