Transistores Efecto de Campo (Fet)

-

Upload

jhonatan-qf -

Category

Documents

-

view

15 -

download

0

description

Transcript of Transistores Efecto de Campo (Fet)

TRANSISTORES EFECTO DE CAMPO (FET)

Referencias: Hayes & Horowitz (pp 142-162 y 244-266),Rizzoni (capítulos 8 y 9)

En un transistor de efecto de campo (FET), la anchura de un canal de conducción en un semiconductor y, por tanto, su capacidad de conducción de corriente, se varía mediante la aplicación de un campo eléctrico (por lo tanto, el nombre de transistor de efecto de campo). Como tal, un FET es un dispositivo "controlado por tensión". Los FET más utilizados son de óxido de metal semiconductor FET (o MOSFET). El MOSFET puede ser fabricado como de tipo de mejora o de tipo agotamiento MOSFET’s. Otro tipo de FET es la unión transistores de efecto campo (JFET), que no se basa en la técnica de fabricación de metal-óxido. FET’s en cada una de estas tres categorías pueden ser fabricados ya sea como un dispositivo de canal n o un dispositivo de canal p. Como los transistores en estos 6 categorías FET se comportan de manera muy similar, nos centraremos a continuación en la operación de MOSFETs de mejora que son los más populares.

n-canal enriquecido-Tipo MOSFET (NMOS)

Se muestra la estructura física de un n-canal Mejora-Tipo MOSFET (NMOS). El dispositivo se fabrica sobre un substrato de tipo p (o de cuerpo). Dos regiones de tipo-n fuertemente dopadas (Fuente y Drenaje) se crean en el sustrato. Una capa delgada (fracción de micra) de SiO2, que es un excelente aislante eléctrico, se deposita entre la fuente y el drenaje. El metal se deposita sobre el aislante para formar la puerta del dispositivo (por lo tanto, semiconductor de óxido metálico). Los contactos metálicos están también hechos en las regiones de la fuente, drenaje, y la del cuerpo.

Para ver el funcionamiento de un NMOS, ponemos a Tierra la fuente y el cuerpo y aplicamos una tensión VGS entre la puerta y la fuente, como se muestra arriba. Esta tensión repele los agujeros en el sustrato de tipo p, cerca de la zona de la puerta, la reducción de la concentración de los huecos. A medida que aumenta VGS, disminuye la concentración de huecos, y en la región cerca de la puerta se comporta cada vez más como el material semiconductor intrínseco (el exceso de concentración de huecos cero) y luego, finalmente, como un material de tipo n como electrones de n + electrodos (fuente y el drenaje) entrar en esta región . Como resultado, cuando VGS se hacen más grandes que un voltaje de umbral, Vt, una capa estrecha entre las regiones de fuente y drenaje se crea que se rellena con los cargos de tipo n (véase la figura). El espesor de este canal es controlado por el VGS aplicada (es realmente controlada por VGS - Vt).

Como se puede ver, este dispositivo funciona como un canal se induce en el semiconductor y este canal contiene cargas de tipo n (por lo tanto, MOSFET de canal N). Además, el aumento vGS aumenta la anchura del canal (mejorando). Por lo tanto, este es un MOSFET del tipo de enriquecimiento.

Ahora por unos valores dados de vGS> Vt (de modo que se forma el canal), vamos a aplicar una pequeña y positiva vDS tensión entre el drenaje y la fuente. Entonces, los electrones de n+ fuente región entran en el canal y alcanzan el drenaje. Si vDS se incrementa, iD corriente que fluye a través del canal. Efectivamente, el dispositivo actúa como una resistencia; su resistencia se establece por la dimensión del canal y su concentración de carga de tipo n. En este régimen, la trama de iD frente vDS es una línea recta (por unos valores dados de VGS > Vt) como se muestra.

La pendiente de la línea iD vs VDS es la conductancia del canal. Cambiar el valor de VGS, cambia la dimensión del canal y su concentración de carga de tipo n y, por tanto, su conductancia. Como resultado, el cambio de VGS, afecta la pendiente de la línea de iD vs VDS como se muestra arriba (la conductancia de corte es cero y la conductancia aumenta con VGS - Vt).

La descripción anterior es correcta para valores pequeños de VDS como en ese caso, VGD = VGS - VDS ≈ VGS y el canal inducido es bastante uniforme (es decir, tiene la misma anchura cerca del drenaje, que está cerca de la fuente). Para un determinado VGS > Vt, si ahora aumentamos VDS, VGD = VGS - VDS se hace menor que VGS. Como tal, el tamaño del canal cerca de drenaje se convierte en comparación con su tamaño cerca de la fuente, como se muestra, más pequeña. A medida que el tamaño del canal se hacen más pequeños, su resistencia aumenta y la curva de iD frente VDS comienza a darse vuelta, como se muestra a continuación.

Para los de valores de VDG = Vt (o VDS = VGS - Vt), la anchura del canal se aproxima a cero cerca del drenaje (canal esta "apretado" apagado). El aumento de VDS más allá de este valor tiene poco efecto (sin efecto en nuestra imagen sencilla) en la forma de canal, y la corriente a través del canal se mantiene constante en el valor alcanzado cuando VDS = VGS - Vt. por eso, cuando el canal se pellizcó, iD sólo depende de VGS (figura de la derecha abajo).

NMOS Curvas características. Dibujo de iD vs VGS en el régimen activo

En suma, un FET puede funcionar en tres regiones:

1) Región de Corte: No existe ningún canal (VGS < Vt para NMOS) y iD = 0 para cualquier VDS.

2) Región óhmico o tríodo: Forma un canal y no apretado (VGS > Vt y VDS ≤ VGS - Vt para NMOS) y el FET se comporta como una resistencia "controlado por tensión".

3) Región activa o de Saturación: Canal apretado (VGS ≥ Vt y VDS > VGS - Vt para NMOS) y el iD no cambia con VDS.

Señalemos varios puntos importantes. En primer lugar, no hay flujos actuales en la puerta, iG = 0 (tenga en cuenta el aislante entre la puerta y el cuerpo). En segundo lugar, el FET actúa como una resistencia "controlada por tensión" en la región óhmica. Además, cuando VDS << VGS, FET actuarían como una resistencia lineal. En tercer lugar, Si iD = 0, esto no significa que FET está en corte. El FET está en corte cuando un canal no existe (VGS < Vt) y iD = 0 para cualquier aplica VDS. Por otro lado, El FET puede estar en la región óhmico, es decir, se forma un canal, pero iD = 0 porque VDS = 0. Por último, el tercer régimen se llama “saturación" porque iD está “saturado" en este régimen y no se incrementa aún más. Algunos libros nuevos llaman a este régimen "activo" (como equivalente al régimen "activo-lineal" de un BJT). Tenga en cuenta que la transición entre la región óhmica y activa está claramente definida por VDS = VGS - Vt el punto donde el canal se estrangulo.

Los iD vs VDS curvas características de un FET son muy similares a iC versus Características VCE curvas de un BJT. De hecho, ya que hay una relación única entre iB y VBE, el IC frente VCE curvas características de un BJT puede ser "etiquetado" con diferentes valores de VBE

lugar de iB haciendo las curvas características de los dos dispositivos aún más similar. En FET VGS comportamiento del dispositivo de control y en BJT VBE

Ambos dispositivos están en corte cuando la tensión de "entrada" está por debajo de un valor umbral: VBE < v para BJT y VGS < Vt para NMOS. Exhiben un régimen de "activo" en la que “salida" actual (iC o iD) es más o menos constante como en la “salida” del voltaje (VCE o VDS). Hay, sin embargo, grandes diferencias. La más importante es que un BJT requiere iB para operar pero en un FET iG = 0 (en realidad muy pequeña). Estas diferencias se hacen más claras a medida que exploramos FET. Como puede verse a partir de NMOS estructura física, el dispositivo es simétrico, es decir la posición de drenaje y la fuente puede ser reemplazada sin ningún cambio en las propiedades del dispositivo. El símbolo de circuito para un NMOS se muestra a la derecha. Para la mayoría de las aplicaciones, sin embargo, el cuerpo está conectado a la fuente, lo que lleva a un elemento 3-terminal. En ese caso, la fuente y de drenaje no son intercambiables. Se utiliza generalmente un símbolo de circuito simplificado para

esta configuración. Por convención, iD corriente fluye en el desagüe de un NMOS (ver figura). Como iG = 0, la misma corriente fluirá fuera de la fuente.

La dirección de la "flechas" que se utilizan para identificar los tipos de semiconductores en un transistor puede parecer confuso. Las flechas no representan la dirección del flujo de corriente en el dispositivo. Por el contrario, indican la dirección de la unión pn subyacente. Para un NMOS, la flecha es colocado en el cuerpo y apuntando hacia el interior, como el cuerpo está hecho de material de tipo p. (La flecha no está en la fuente o en el drenaje, ya que son intercambiables.) en el símbolo simplificado para el caso cuando se conecta el cuerpo y la fuente, la flecha está en el fuente (dispositivo no es simétrica ahora) y está apuntando hacia afuera como la fuente está hecha de materiales de tipo n. (i., e. flecha apuntando hacia el interior de tipo p, flecha apuntando hacia afuera de tipo n).

NMOS iD vs VDS Ecuaciones Características

Como BJT, un NMOS (con fuente conectada al cuerpo) tiene seis parámetros (tres de tensiones y tres de corrientes), dos de los cuales (iS y VGS) que se pueden encontrar en términos de los otros cuatro aplicando LVK y LCK. El NMOS es más simple que BJT porque iG = 0 (y es = iD). Por lo tanto, tres parámetros describen el comportamiento de un NMOS (vGS, iD, y VDS). El NMOS tiene una ecuación característica que relaciona estos tres parámetros. Una vez más, la situación es más simple que existe BJT como características sencillas pero precisas ecuaciones.

Corte: VGS < Vt, iD = 0 para cualquier VDS

Óhmica: VGS> Vt, iD = K [2VDS (VGS - Vt) - V2DS] para VDS < VGS - Vt

Activa: VGS> Vt, iD = K (VGS - Vt)2 para VDS > VGS – Vt

Donde k es una constante que depende de la manufactura de la NMOS. Como se mencionó anteriormente, para valores pequeños de VDS, NMOS se comporta como una resistencia. rDS, y el valor del rDS es controlado por VGS – Vt. Esto se puede ver por la caída v2

DS en iD ecuación del régimen óhmica:

Cómo resolver circuitos NMOS:

La solución del método es muy similar al circuito de BJT (en realidad más simple porque iG = 0). Para resolver, suponemos que NMOS está en un estado en particular, utilice el modelo NMOS para ese estado para resolver el circuito y comprobar la validez de nuestra hipótesis comprobando las desigualdades en el modelo para ese estado. Un procedimiento formal es:

1) Escriba la LVK en el lazo puerta-surtidor GS (lo llaman GS-KVL).2) escriba la LVK en el lazo drenador-surtidor DS (lo llaman DS-KVL).3) A partir de LVK-GS, calcular VGS (sabiendo que iG = 0)

3a) Si VGS < Vt, NMOS está en la región de corte. iD = 0, y encuentre la VDS-LVK. Hemos terminado.3b) Si VGS > Vt, NMOS no está en corte. Vaya al paso 4.

4) Supongamos NMOS está en la región activa. Calcular iD de iD = K (VGS - Vt)2. A continuación, utilice DS-KVL para calcular VDS. Si VDS > VGS - Vt, aquí se ha terminado. De lo contrario, vaya al paso 5.

5) NMOS tiene que estar en la región óhmica. Sustituto de iD de iD = K[2VDS (vGS - Vt) - v2DS]

en DS-KVL. Usted recibirá una ecuación cuadrática en VDS. Encuentra VDS (una de las dos raíces de la ecuación será no fisica). Asegúrese de que VDS < VGS - Vt. VDS sustitutos en DS-KVL encontrando iD.

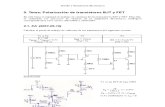

Ejemplo: Considere circuito NMOS abajo con K = 0.25 mA / V2 y Vt = 2 V. Encontrar vo cuando vi = 0, 6 y 12 V para RD = 1 K y VDD = 12 V.

GS KVL: vGS = vi

DS KVL: VDD = RDiD + vDS

A) vi = 0 V. A partir de GS KVL, obtenemos vGS = vi = 0. Como vGS < Vt = 2 V, NMOS está en corte, iD = 0, y vDS se encuentra apartir DS KVL:

DS KVL: vo = vDS = VDD - RDiD = 12 V

B) vi = 6 V. A partir de GS KVL, obtenemos vGS = vi = 6 V. Desde vGS = 6 > Vt = 2, NMOS no está en corte. Supongamos NMOS en región activa. Entonces:

iD = K (vGS - Vt)2 = 0.25 x 10-3 (6 - 2)2 = 4 mA

DS KVL: vDS = VDD - RDiD = 12 - 4 x 103 x 10-3 = 8 V

Desde vDS = 8 > vGS - Vt = 2, NMOS en efecto, en la región activa y iD = 4 mA y

vo = vDS = 8 V.

C) vi = 12 V. A partir de GS KVL, obtenemos vGS = 12 V. Desde vGS > Vt, NMOS no está en corte. Supongamos NMOS en región activa. Entonces:

iD = K (vGS - Vt)2 = 0.25 x 10-3 (12 - 2) 2 = 25 mA

DS KVL: vDS = VDD - RDiD = 12 - 25 x 103 x 10-3 = -13 V

Desde vDS = -13 < vGS - Vt = 12 - 2 = 10, NMOS NO está en la región activa.

- Supongamos NMOS en la región óhmica. Entonces:

iD = K [2vDS (vGS - Vt) - v2DS] = 0.25 x 10-3 [2vDS (12 - 2) - v2DS]

iD = 0.25 x 10-3 [20vDS - v2DS]

- Sustituyendo iD en DS KVL, obtenemos:

DS KVL: VDD = RDiD + vDS 12 = 103 x 0.25x 10-3 [20vDS – v2DS] + vDS

v2DS - 24vDS + 48 = 0

Esta es una ecuación cuadrática en vDS. Las dos raíces son: vDS = 2.2 V y vDS = 21.8 V. La segunda raíz no es física, como el circuito está alimentado por un suministro de 12 V. Por lo tanto, vDS = 2.2 V. Como vDS = 2.2 < vGS - Vt = 10, NMOS esta en efecto, en la región óhmica con vo = vDS = 2.2V y

DS KVL: vDS = VDD - RDiD iD = 12– 2.21000

=9.8mA

Líneas de Carga: El funcionamiento de los circuitos NMOS se puede entender mejor con uso del concepto de línea de carga. Similar a BJT, línea de carga es básicamente la línea que representa DS KVL en iD frente espacio vDS. Línea de carga del circuito de ejemplo se muestra aquí.

Ejercicio: Marque los puntos Q del ejemplo anterior para vi = 0,6 y 12 V en la línea de carga figura a continuación.

Efecto cuerpo

Al derivar NMOS (y otra MOS) iD vs VDS, habíamos asumido que el cuerpo y la fuente están conectados. Esto no es posible en un chip integrado que tiene un cuerpo común y un gran número de dispositivos MOS (conexión de cuerpo a la fuente para todos los dispositivos significa que todas las fuentes están conectadas). La práctica común es unir el cuerpo del chip de la tensión más pequeña disponible de la fuente de alimentación (cero o negativa). En este caso, la unión pn entre el cuerpo y la fuente de todos los dispositivos se invertirá. El impacto de esta a una menor tensión umbral de los dispositivos MOS ligeramente y su llamado efecto cuerpo. Efecto corporal puede degradar el rendimiento del dispositivo. Para el análisis, vamos a suponer que el efecto del cuerpo es insignificante.

Mejoramiento del Canal –p Tipo MOSFET (PMOS)

La estructura física de un PMOS es idéntica a un NMOS excepto que los tipos de semiconductores se intercambian, es decir, el cuerpo y la puerta están hechos de material de tipo n y de fuente y el drenaje están hechos de material de tipo p y se forma un canal de tipo p. Como el signo de los portadores de carga se invierte, todas las tensiones y corrientes en un PMOS se invierten.

Por convención, la corriente de drenaje está fluyendo fuera de la fuga como se muestra en la figura.

Corte: VGS > Vt, iD = 0 para cualquier VDS

Óhmica: VGS < Vt, iD = K[2VDS(VGS - Vt) - V2DS] para VDS > VGS - Vt

Activo: VGS < Vt, iD = K(VGS - Vt)2 para VDS < VGS Vt

Tenga en cuenta que Vt es negativo para un PMOS.

Complementarios MOS (CMOS)

Complementario Mos emplea transistores MOS de ambos polaridades como se muestra a continuación. Los dispositivos CMOS son más difíciles de fabricar que NMOS, pero muchos circuitos más potentes son posibles con la configuración de CMOS. Como tal, la mayoría de los circuitos MOS hoy emplean configuración de CMOS y la tecnología CMOS se está tomando rápidamente sobre muchas aplicaciones que sólo eran posibles con dispositivos bipolares hace unos años.

Agotamiento -Tipo MOSFET

El MOSFET de tipo agotamiento tiene una estructura similar a la del MOSFET del tipo de enriquecimiento con sólo una diferencia importante; MOSFET de tipo decremental tiene un canal implantado físicamente. Así, una de tipo n MOSFET de tipo decremental ya tiene un canal de tipo n entre el drenaje y la fuente. Cuando una tensión VDS se aplica al dispositivo, una corriente id = IDSS fluye incluso para VGS = 0. (Mostrar IDDS = KV2t.). Similar a NMOS, si VGS se incrementa, el canal se convierte en aumentos más amplios y iD. Sin embargo, en una de tipo n MOSFET de tipo decremental, un VGS negativo también se puede aplicar al dispositivo, lo que hace que el canal más pequeño y reduce iD. Como tal, vGS negativas "agota" los canales de portadores de tipo n que conducen a el nombre MOSFET de tipo decremental. Si vGS se reduce aún

más, en un cierto valor umbral Vt (que es negativo), el canal desaparece y Id = 0, como se se ve en la figura. debería ser obvio que un MOSFET de tipo decremental se puede operar ya sea en modo de enriquecimiento o en modo de agotamiento. de tipo p agotamiento MOSFET funcionan de manera similar a la de tipo p mejora MOSFET esperar que Vt> 0 para el tipo de agotamiento y vt <0 para el tipo de mejora. figura siguiente muestra iD frente vGS de cuatro tipos de dispositivos MOSFET en la región activa. símbolos para dispositivos MOSFET de tipo agotamiento también se muestran.

MOSFET de tipo n agotamiento MOSFET de tipo p agotamiento

Inversor y el interruptor NMOS

El circuito básico inversor NMOS que se muestra en la figura; es un circuito muy similar a un convertidor de BJT.

Este circuito se resolvió en la página 65 para VDD = 12 y RD = 1 kW. Hemos encontrado que si vi = 0 (de hecho vi < Vt ) , NMOS estará en corte con ID = 0 y Vo = VDD .

Cuando Vi = 12 V, NMOS debe estar en la región óhmica con Id = 10 mA y VDS = 2,2 V.Por lo tanto, el circuito es una puerta de inversor. También puede ser utilizado como interruptor.

Hay alguna diferencia importante entre NMOS y BJT puertas del inversor.

En primer lugar, BJT necesita una resistencia RB. Esta resistencia "convierte " la tensión de entrada en un IB y mantener VBE ≈ V .NMOS no necesita una resistenciaγ entre la fuente y la tensión de entrada como IG = 0 y Vi = VGS se puede aplicar directamente a la puerta.

En segundo lugar, si la tensión de entrada es " alto", el BJT irá a la saturación con Vo = VCE = Vsat = 0,2 V. En la puerta NMOS, si la tensión de entrada es " alta", NMOS está en la región óhmica. En este caso, VDS puede tener cualquier valor entre 0 y VGS; el valor de Vo = VDS es fijado por el valor de la resistencia RD.

Este efecto se muestra en la función de compuerta de inversión para transferir dos valores diferentes de RD.

Ejercicio: Calcular Vo para el circuito anterior con VDD = 12 y RD = 10 kW cuando Vi =12 V

Inversor CMOS

El inversor CMOS, es un bloque de construcción de puertas lógicas CMOS, que se muestra a continuación. La "baja" y los estados " altos" de este circuito corresponden a 0 y VDD, respectivamente. Puertas CMOS son Incorporado en el mismo chip de tal manera que ambos tienen la misma tensión de umbral Vtn = Vt, Vtp = -Vt y el mismo K (uno tiene diferente longitud y anchura del canal para obtener el mismo K para PMOS y NMOS.

Para el análisis de las compuertas CMOS en 60L, siempre asumimos que éste es el caso.

En este caso, el CMOS tendrá una característica de transferencia " simétricos “, es decir, Vo = 0.5VDD cuando Vi = 0.5VDD como se muestra a continuación.

Vi = 0 Desde Vgs1 = Vi = 0 < Vt, NMOS estará en corte.

Por lo tanto, ID1 = 0. Pero VGS2 = Vi- VDD = -VDD < -Vt, Por lo tanto, PMOS se encenderán. Recordemos que ID frente a la característica VDS curvas de un NMOS (página 63), cada etiquetada con valores de VGS. Como Vgs2 = VDD es una constante, punto de funcionamiento de PMOS estará en una de las curvas. Pero Id1 = ID2 = 0 y el único punto que satisface esta condición es VDS2 = 0. Obsérvese que PMOS NO está en corte, es una región óhmica y actúa como una resistencia. VDS2 = 0 porque ID2 = 0. El voltaje de salida se pueden encontrar ahora por KVL: Vo = VDD - VDS2 = VDD. Así que, cuando Vi = 0, Vo = VDD.

Vi = VDD Desde Vgs1 = Vi = VDD > Vt , NMOS estará en encendida . Pero desde Vgs2 = Vi - VDD =0> -Vt, PMOS estarán en corte y ID2 = 0. Como Id1 = ID2, Id1 = 0. Como NMOS es Id1 = 0, NMOS debe estar en la región óhmica con VDS1 = 0. Entonces Vo = VDS1 = 0. Por lo tanto, cuando Vi = VDD, Vo = 0 Vi = 0.5VDD en este caso, Vgs1 = Vi = 0.5VDD y Vgs2 = Vi - VDD = -0.5VDD.

Dado que, Vgs1 > Vt y VGS2 < -Vt, Ambos transistores se encenderán.

Además, como los transistores tienen mismo voltaje de umbral, mismo K, Id1 = ID2 y Vgs1 = | VGS2 |, tanto transistor estará en el mismo estado (ya sea óhmica o activo) y tendrá VDS idénticos: VDS1 = -VDS2. Desde VDS1 - VDS2 = VDD, entonces VDS1 = 0.5VDD, VDS2 = -0.5VDD, y Vo = 0.5VDD.

La función de transferencia del inversor CMOS para VDD = 12 V y VT = 2 V se muestra a continuación

CMOS es un inversor que tiene muchas ventajas en comparación con el inversor NMOS. Su función de transferencia es mucho más cercano a una función de transferencia ideales inversor. Los estados " bajas " y altas " son claramente definidos (bajo estado de NMOS dependía del valor de RD). No incluye ninguna resistencia y por lo tanto tiene menos área en el chip.

Por último, Id1 = ID2 = 0 para ambos casos la salida es baja o alta. Esto significa que la puerta consume muy poca energía (teóricamente cero) en cualquiera de los estados. Uno o cero ID1 = ID2, sin embargo, fluye en el circuito cuando la puerta está en la transición de un estado a otro como se ve en la figura.

El valor máximo de ID que fluye a través de la puerta durante la transición puede ser fácilmente calculado corriente que fluye cuando Vi = 0.5VDD y VO = 0.5VDD.

Por ejemplo, considere el inversor CMOS con VDD = 12 V, Vt = 2 V, y K = 0,25 mA / V2.ID máxima fluye cuando Vi = Vgs1 = 0.5VDD = 6 V. En este punto, VDS1 = Vo = 0.5VDD =6 V.

Como, VDS1 = 6 > Vgs1 - Vt = 4 V, NMOS está en régimen activo. Entonces:

id1 = K (Vgs1 – Vt)^2 = 0,25 × 10-3( 6 - 2 ) ^2 = 4 mA

Puerta CMOS NAND

Como se mencionó antes puertas lógicas CMOS tienen " Bajo" y "alto" estados de 0 y VDD, respectivamente.Tenemos que considerar todos los casos posibles a demostrar que esta puerta un NAND.Para empezar, tenemos varias observaciones generales:

1) de KCL Id1 = ID2 = ID3 + Id42) por Vo KVL = VDD - VDS3 = VDS1 + VDS2 y VDS3 = VDS4.3) por KVL VGS3 = V1 - VDD, VGS4 = V2 - VDD, y Vgs1 = V1

Nuestro análisis se convertirá en simple si consideramos en primer lugar el caso siguiente:

Cuando V1 = 0, entonces Vgs1 = 0 y M1 estará apagado que conduce a ID1 = ID2 = 0. Por KCL, ID3 + Id4 = 0. Como tanto ID3 ≥ 0 y Id4 ≥ 0, se deben tener ID3 = Id4 = 0. Además, cuando V1 = 0 VGS3 = V1 - VDD = -VDD < Vt. Por lo tanto, M3 estará encendida. Pero desde ID3 = 0, M3 debe estar en el régimen óhmico y VDS3 = 0. Entonces, Vo = VDD - VDS3 = VDD. Así que, cuando V1 = 0, Vo = VDD, todas las corrientes son cero, M1 está apagado, y M3 esta prendida. Estado de los otros dosTransistores dependerá de V2.

1) V1 = 0, V2 = 0 Cuando V1 = 0, Vo = VDD, todas las corrientes son cero, M1 está apagado, y M3 está en encendida. Para saber el estado de M4, observamos VGS4 = V2 - VDD = -VDD < -Vt. Por lo tanto, M4 está en encendida (con VDS4= 0 porque Id4 = 0). Para saber el estado de M2, asumamos M2 está encendida (VGS2 > Vt).

Entonces, VDS2 = 0 porque ID2 = 0. Dado que, Vo = VDS1 + VDS2 = VDD,VDS1 = VDD - VDS2 = VDD.

Entonces, VGS2 = V2 - VDS1 = -VDD < Vt.

Por lo tanto, nuestra hipótesis de M2 que es encendida es incorrecta y M2 es apagado.Así que, cuando V1 = 0, V2 = 0, M1 esta pagado, M2 apagado, M3 está encendida, y M4tambien está encendida, todas las corrientes son cero, y Vo = VDD.

2) V1 = 0, V2 = VDD Cuando V1 = 0, Vo = VDD, todas las corrientes son cero, M1 está apagado, y M3 está prendida. Para saber el estado de M4, observamos VGS4 = V2- VDD = 0> -Vt.

Así, M4 está apagada.

Para encontrar el estado de M2, supongamos M2 está encendida (VGS2 > Vt). Entonces, VDS2 = 0 porque ID2 = 0. Dado que, Vo = VDS1 + VDS2 = VDD, VDS1 = VDD - VDS2 = VDD. Entonces, VGS2 = V2 - VDS1 = -VDD < Vt.Por lo tanto, nuestra hipótesis de M2 EN es incorrecta y M2 está apagada.Así que, cuando V1 = 0, V2 = VDD, M1 está apagada, M2 está apagada, M3 está encendida, y M4 está apagada, todas las corrientes son cero, y Vo = VDD.

3) V1 = VDD, V2 = 0 Vgs1 = V1 = VDD > Vt, Por lo que M1 está en encendida. También, VGS2 = V2 - VDS1 =-VDS1 < Vt como VDS1 ≥ 0. Por lo tanto, M2 está apagada y Id1 = ID2 = 0.

VGS3 = V1 - VDD = 0> -Vt, así M3 está apagada y ID3 = 0. Entonces, de KCL, debemos tener Id4 = 0. Por último, VGS4 =V2 - VDD = -VDD < -Vt, Por lo M4 está encendida. Desde M4 está encendida y Id4 = 0, VDS4 = 0.

Entonces, Vo = VDD - VDS4 = VDD.Así que, cuando V1 = VDD, V2 = 0, M1 está encendida, M2 está apagada, M3 está apagada, y M4 está prendida, todas las corrientes son cero, y Vo = VDD.

4) V1 = VDD, V2 = VDD Vgs1 = V1 = VDD > Vt, Por lo que M1 está encendida. Además, VGS3 = V1 - VDD =0> -Vt, Por lo que M3 está apagado y ID3 = 0. Además. VGS4 = V2 -VDD = 0> -Vt, Por lo M4 está apagado y ID3 = 0.

Entonces, de KCL Id1 = ID2 = 0. Como M1 está prendida y Id1 = 0, vDS1 = 0. Entonces, VGS2 = V2 - VDS1 = VDD > Vt y M2 esta prendida, y VDS2 = 0

Porque ID2 =0. Por lo tanto, V0 = VDS1 + VDS2 = 0.Así que, cuando V1 = VDD, V2 = 0, M1 esta prendida, M2 esta prendida, M3 esta apagada, y M4 está apagada, todas las corrientes son cero, y Vo = 0.

Puerta CMOS NOR

Ejercicio: Demostrar que esto es una puerta NOR.

t