Sprinkler Buddy Presentation #10: “LVS” 4/11/2007 Team M3 Sasidhar Uppuluri Devesh Nema Kalyan...

-

date post

22-Dec-2015 -

Category

Documents

-

view

214 -

download

0

Transcript of Sprinkler Buddy Presentation #10: “LVS” 4/11/2007 Team M3 Sasidhar Uppuluri Devesh Nema Kalyan...

Sprinkler Buddy

Presentation #10:

“LVS”

4/11/2007

Team M3Sasidhar Uppuluri

Devesh Nema Kalyan Kommineni

Kartik Murthy Panchalam Ramanujan

Design Manager: Bowei Gai

“Low Cost Irrigation Management For Everyone !”

Current Status Determine Project Develop Project Specifications Plan Architectural Design

Determination of all components in design Detailed logical flowchart

Design a Floor Plan Create Structural Verilog Make Transistor Level Schematic Layout Testing (Extraction, LVS, and Analog Sim.)

Need to Exhaustively Test

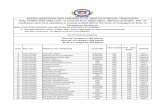

Final Design SizeBlock (# used) Size (um)

40:20 Muxes (4) 20 x 80

60:20 Muxes (2) 20 x 120

Counter (2) 12 x 17

KC ROM (1) 181 x 8

P ROM (1) 70 x 8

Metric Storage SRAMS (2)

181 x 60

Constant Storage ROM (1)

181 x 8

Floating Point Adder (4)

96x151

Floating Point Multiplier (2)

89 x 40

10 Bit Registers (8) 50 x 10

• 362um x 361 um• ~ 1 : 1.0001 aspect ratio• .129 mm^2 area• .23 Density

Overview: FSMsMode Gates Flops Outputs

Daily Update

97 4 18

Hourly

Update

56 3 6

Comp. Mode

30 3 6

Feed Back

30 3 7

Power Gate

67 6 7

Design Challenges and Implementation

DecisionsFor The Past Week

Design Challenge

Translation to HW

Low Power • VDD Gating but had to forgo GND Gating