Last Mod: Jan 2015 Paul R. Godin Shift Registers : Technician Series Registers 1.1.

Registers Shift Registers

-

Upload

lina-al-saleh -

Category

Documents

-

view

248 -

download

0

Transcript of Registers Shift Registers

-

8/13/2019 Registers Shift Registers

1/31

2008 The McGraw-Hill Companies, Inc. All rights reserved.

Registers

By : Eng. Lina

11/14/2013 1

-

8/13/2019 Registers Shift Registers

2/31

p g

11/14/2013 2

Benefits of registers

Flip-flops are limited because they can store only one bit. Most computers work with integers and single-precision floating-

point numbers that are 32 /64-bits long. A registeris an extension of a flip-flop that can store multiple bits. Registers are commonly used as temporary storage in a processor.

They are faster and more convenient than main memory. More registers can help speed up complex calculations.

-

8/13/2019 Registers Shift Registers

3/31

11/14/2013 3

A basic register

Basic registers are easy to build. Registers are made using multiple flip-flops .

We can store multiple bits just by putting a bunch of flip-flops together! A 4-bit register is shown on the right, and its internal

implementation is below.

This register uses D flip-flops

its easy to store data without worrying about flip-flopinput equations. All the flip-flops share a common CLKand CLR (RESET)

signals.

-

8/13/2019 Registers Shift Registers

4/31

Registers

Another way to represent a 4-bit register

You could see the timing diagram in the followingSlide .

D Q

R

Reset

D Q

R

D Q

R

D Q

RCLK

I0

I1

I2

I3

A0

A1

A2

A3

11/14/2013 4

-

8/13/2019 Registers Shift Registers

5/31

Registers

D Q

R

Reset

D Q

R

D Q

R

D Q

RCLK

I0

I1

I2

I3

A0

A1

A2

A3

CLK

I3

I2

I1

I0

A3

A2

A1

A0Note: New data has to go in with

every clock11/14/20135

-

8/13/2019 Registers Shift Registers

6/31

11/14/2013 6

Adding a parallel load operation

The input D3-D0is copied to the output Q3-Q0on everyclock cycle. How can we store the current value for more than one cycle?

Lets add a load input signal LD to the register. If LD = 0, the register keeps its current contents. If LD = 1, the register stores a new value, taken from inputs D3-D0.

LD Q(t+1)

0 Q(t)

1 D3-D0

-

8/13/2019 Registers Shift Registers

7/31

Shift Register

The binary information in a register can be - in addition to storing-canbe moved from stage to stage within the register or into or out of the

register upon application of clock pulses. This type of bit movement or shifting is essential for certain

arithmetic and logic operations used in microprocessors.

Shift Register :a group of FFs arranged so that binary numbers storedin the FFs can be shifted from one FF to the next FF, for every clockpulse.

11/14/2013 7

-

8/13/2019 Registers Shift Registers

8/31

11/14/2013 8

A shift registershifts its output once every clock cycle.

SIis an input that supplies a new bit to shift intothe register. For example, if on some positive clock edge we have:

SI = 1Q0-Q3= 0110

then the next state will be:

Q0-Q3= 1011

The current Q3(0in this example) will be lost on the next cycle.

Shift registers

Q0(t+1) = SIQ1(t+1) = Q0(t)Q2(t+1) = Q1(t)Q3(t+1) = Q2(t)

-

8/13/2019 Registers Shift Registers

9/31

11/14/2013 9

Shift direction

The circuit and example make it look like the register shifts right.

But it really depends on your interpretation of the bits. If you considerQ3 to be the most significant bit instead, then the register is shifting

in the oppositedirection!

Q0(t+1) = SIQ

1(t+1) = Q

0(t)

Q2(t+1) = Q1(t)Q3(t+1) = Q2(t)

Present Q0-Q3 SI Next Q0-Q3

ABCD X XABC

Present Q3-Q0 SI Next Q3-Q0

DCBA X CBAX

-

8/13/2019 Registers Shift Registers

10/31

Shift Registers Classification

Shift registers can be classified into: Shift right registers.

Shift left registers. Serial in/Serial out shift registers. Serial in/Parallel out shift registers. Parallel in/Serial out shift registers. Parallel in/Parallel out shift registers. Universal shift registers.

11/14/2013 10

-

8/13/2019 Registers Shift Registers

11/312008 The McGraw-Hill Companies, Inc. All rights reserved.

Serial/Parallel Data Conversion

11/14/2013 11

1 0 1 0 1 1 1 1Serial in Serial out

Shift registers can be used to convert from serial-to-parallel or the reverse from parallel-to-serial.

1 0 1 0 1 1 1 1Serial in

Parallel out

1 0 1 0 1 1 1 1 Serial out

Parallel in

1 0 1 0 1 1 1 1

Parallel in

Parallel out

-

8/13/2019 Registers Shift Registers

12/312008 The McGraw-Hill Companies, Inc. All rights reserved.

QUIZ

Q#1- This represents a ___ register.

a. Parallel-in, parallel-out

b. Serial-in, parallel-out

ANS: serial-in parallel-out

Q#2- This represents a ___ register.a. Parallel-in, parallel-out

b. Serial-in, serial-out

ANS: serial-in serial-out

Q#3- This represents a ___ register.a. Parallel-in, serial out

b. Serial-in, parallel-out

ANS: parallel-in serial-out

Q#4- This represents a ___ register.a. Parallel-in, serial out

b. Parallel-in, parallel-out

ANS: parallel-in parallel-out

11/14/2013 12

-

8/13/2019 Registers Shift Registers

13/312008 The McGraw-Hill Companies, Inc. All rights reserved.

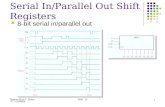

Serial-in / Parallel-output Shift Register

11/14/2013 13

Note the use of D FFs.Clock (CLK) inputs wired in parallel.

Clear (CLR) inputs can be activated with LOWor disabled with HIGH.

Preset (PS) inputs deactivated.

Parallel outputs here.Order= A B C D

Inputs here:(1) Data(2) Clock(3) Clear

Clear input:Active = 0

Deactivated = 1

Clock input:

Positive-edgetriggering

Clock Pulse 1

Clear = 0

Data = 1

0 0 0 01 0 0 0

Clock Pulse 2

Clear = 1

Data = 1

1 1 0 00 1 1 0

Clock Pulse 3

Clear = 1

Data = 1

Clock Pulse 4

Clear = 1

Data = 0

0 0 1 1

Clock Pulse 5

Clear = 1

Data = 0

0 0 0 1

Clock Pulse 6

Clear = 1

Data = 0

Clock Pulse 7

Clear = 1

Data = 1

1 0 0 00 1 0 0

Clock Pulse 8

Clear = 1

Data = 04-bit

serial-in

parallel outshift right

shift register

-

8/13/2019 Registers Shift Registers

14/312008 The McGraw-Hill Companies, Inc. All rights reserved.

Clock Pulse 1

Clear = 0

Data = 1

Clock Pulse 2

Clear = 1

Data = 1

Clock Pulse 3

Clear = 1

Data = 0

Clock Pulse 4

Clear = 1

Data = 0

Clock Pulse 5

Clear = 1

Data = 1

QUESTION #1This is a ___ type shift register.

A. Serial-in, parallel outB. Parallel-in, serial-out

A: Serial-in, parallel-out

QUESTION #2What is the 4-bit output (bit A on left, D on right) after pulse 1?

A: 0000

QUESTION #3What is the 4-bit output (bit A on left, D on right) after pulse 2?

A: 1000

QUESTION #4What is the 4-bit output (bit A on left, D on right) after pulse 3?

A: 0100

QUESTION #5What is the 4-bit output (bit A on left, D on right) after pulse 4?

A: 0010

QUESTION #6What is the 4-bit output (bit A on left, D on right) after pulse 5?

A: 1001

QUESTION #7What is the 4-bit output (bit A on left, D on right) after pulse 6?

A: 1100

Clock Pulse 6

Clear = 1

Data = 1

QUIZ

11/14/2013 14

-

8/13/2019 Registers Shift Registers

15/31

Serial input / Serial output Shift Registers

4-Bit Shift Register

Serial

InputSerial

Output

D Q D Q D Q D Q

CLK

SI SO

Serial

InputSerial

Output

11/14/2013 15

-

8/13/2019 Registers Shift Registers

16/31

Serial input / Serial output Shift Registers

16

D Q D Q D Q D Q

CLK

SI SO

Q3

SI

Q2

Q1

Q0

CLK

Q3 Q2 Q1 Q0

11/14/2013

-

8/13/2019 Registers Shift Registers

17/31

How SISO Shift register work

In order to get the data out of the register, they must be shiftedout serially.

This can be done destructively or non-destructively. For destructive readout, the original data is lost and at the end of

the read cycle, all flip-flops are reset to zero.

-

8/13/2019 Registers Shift Registers

18/31

How SISO Shift register work

To avoid the loss of data, an arrangement for a non-destructivereading can be done by adding two AND gates, an OR gate and an

inverter to the system. The construction of this circuit is shown below.

The data is loaded to the register when the control lineis HIGH =1 (i.e WRITE).

The data can be shifted out of the register when thecontrol line is LOW(ie READ).

Read =0Write= 1

-

8/13/2019 Registers Shift Registers

19/31

11/14/2013 19

Serial data transfer

One application of shift registers is converting between serial dataand parallel data.

Computers typically work with multiple-bit quantities. ASCII text characters are 8 bits long. Integers, single-precision floating-point numbers, and screen pixels

are up to 32 bits long.

But sometimes its necessary to send or receive data serially, or one bit

at a time. Some examples include: Input devices such as keyboards and mice. Output devices like printers. Any serial port, USB or Firewire device transfers data serially.

-

8/13/2019 Registers Shift Registers

20/31

11/14/2013 20

Receiving serial data

To receiveserial data using a shift register: The serial device is connected to the registers SI input.

The shift register outputs Q3-Q0 are connected to the computer. The serial device transmits one bit of data per clock cycle.

These bits go into the SI input of the shift register. After four clock cycles, the shift register will hold a four-bit word.

The computer then reads all four bits at once from the Q3-Q0 outputs.

serial device

computer

-

8/13/2019 Registers Shift Registers

21/31

11/14/2013 21

Sending data serially

To senddata serially with a shift register, you do the opposite: The CPU is connected to the registers D inputs.

The shift output (Q3 in this case) is connected to the serial device. The computer first stores a four-bit word in the register, in one cycle. The serial device can then read the shift output.

One bit appears on Q3 on each clock cycle. After four cycles, the entire four-bit word will have been sent.

serial device

computer

-

8/13/2019 Registers Shift Registers

22/31

COUNTERS

11/14/2013 22

-

8/13/2019 Registers Shift Registers

23/31

11/14/2013

Counters

A Counter : is a register that goesthrough a prescribed series ofstates

It stores (and sometimes displays)the number of times a particularevent or process has occurred, oftenin relationship to a clock signal.

the flip-flop s values themselves,serves as the output in a counter.

The output value increases by one oneach clock cycle.

After the largest value, the outputwraps around back to 0.

Using two bits, wed get somethinglike this:

Present State Next State

A B A B

0 0 0 1

0 1 1 0

1 0 1 1

1 1 0 0

00 01

1011

1

11

1

-

8/13/2019 Registers Shift Registers

24/31

11/14/2013

Benefits of counters

Counters can act as simple clocks to keep track of time. You may need to record how many times something has happened.

How many bits have been sent or received? How many steps have been performed in some computation?

All processors contain a program counter, or PC. Common tasks of counter

Count up or down

Increment or decrement count Divide frequency As temporary memory

Applications: Watches Clocks Alarms Web browser refresh

24

COUNTERS

SYNCHRONOUS ASYNCHRONOUS

-

8/13/2019 Registers Shift Registers

25/31

Classifications of Counters

Asynchronous Counters

Only the first flip-flop is clocked by an external clock. Allsubsequent flip-flops are clocked by the output of the precedingflip-flop.

Asynchronous counters are slower than synchronous countersbecause of the delay in the transmission of the pulses from flip-

flop to flip-flop. Asynchronous counters are also called ripple-countersbecause of

the way the clock pulse ripples it way through the flip-flops.

Synchronous Counters

All flip-flops are simultaneously clocked by an external clock. Synchronous counters are faster than asynchronous countersbecause of the simultaneous clocking.

Synchronous counters are an example of a state machines design.

-

8/13/2019 Registers Shift Registers

26/31

Characteristics of Counters

Binary counterCounter that follows a binary sequence

N bit binary counter counts in binary from n to 2n-1

Number of bits (4-bit, 8-bit, etc.) Maximum count

4 bit = 24 = 0000 to 1111 in binary

8 bit = 28 = 0000 0000 to 1111 1111 in binary

Modulus of counter-number of states

Decade counter

4-bit

8-bit

Up or down counter

-

8/13/2019 Registers Shift Registers

27/31

QUIZ

1. A 4-bit counter will count from binary 0000

to __________.

2. Counters can be designed to count up or

downward or devised to be self-stopping.(True or False)

1111

True

-

8/13/2019 Registers Shift Registers

28/31

Ripple Counter

In Ripple Counters :

All the states of the FF do not change at the same

time.

When the output state of the preceding FF changes

it will trigger the next state to change.

due to the way the FFs respond one after another it

is a kind of rippling effect.

-

8/13/2019 Registers Shift Registers

29/31

Ripple Counter

0 0 0 00 0 0 1

Binary Output

0 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 0

Pulse 1

Clock Input

All J-K flip-flopsin theTOGGLE MODE

PS and CLR inputsareINACTIVE

Pulse 2Pulse 3Pulse 4Pulse 5Pulse 6Pulse 7Pulse 8

On the next clock pulse (8) all FFswill toggle because each will receiveaH-to-Lpulse- one after another.

Watch the count ripple thru the counter.

This 4-bit counter has 16 states andwill count from binary 0000 through 1111and then reset back to 0000.

The counter has amodulus of 16.

-

8/13/2019 Registers Shift Registers

30/31

Ripple Counter With Waveforms

0 0 0 00 0 0 1

Binary Output

0 0 1 00 0 1 10 1 0 00 1 0 1

Pulse 1

Clock Input

Pulse 2Pulse 3Pulse 4Pulse 5

Clock input

1s output

2s output

4s output

FFs triggered on

H-to-L pulse.CLK toggles 1s FF.1s FF toggles 2s FF.2s FF toggles 4s FF.

-

8/13/2019 Registers Shift Registers

31/31

QUIZ

0 0 0 0

Q#1- After pulse 1 the output of the ripple

counter will be binary ___.

Pulse 1

0 0 0 10 0 1 0

Q#2- After pulse 2 the output of the ripple

counter will be binary ___.

1 0 0 0

Q#3- After pulse 8 the output of the ripple

counter will be binary ___.

1 1 1 1

Q#4- After pulse 15 the output of the ripple

counter will be binary ___.

Input PulsesPulse 2Pulse 8Pulse 15