Open Loop Gain. We test the Open Loop Gain of a CMOS amplifier of Example 3-1. The gain is 30....

-

Upload

julius-robertson -

Category

Documents

-

view

232 -

download

0

Transcript of Open Loop Gain. We test the Open Loop Gain of a CMOS amplifier of Example 3-1. The gain is 30....

Open Loop Gain

• We test the Open Loop Gain of a CMOS amplifier of Example 3-1.

• The gain is 30.

Experiment 11-11

M4 M1

M2M3

Vbias=0.7VVin=0.7V

Vs

out

VDD=3.3V

L=0.35uW3=10u

L=0.35uW2=10u

L=0.35uW1=10u

L=0.35uW4=10u

.protect

.lib 'c:\mm0355v.l' TT

.unprotect

.op

.options nomod post

VDD 1 0 3.3v

.param W1=10u W2=10u W3=10u W4=10uM1 2 3 0 0+nch L=0.35u W='W1' m=1 AD='0.95u*W1' +PD='2*(0.95u+W1)' AS='0.95u*W1' PS='2*(0.95u+W1)'M2 2 4 1 1+pch L=0.35u +W='W2' m=1 AD='0.95u*W2' PD='2*(0.95u+W2)' +AS='0.95u*W2' PS='2*(0.95u+W2)'M3 4 4 1 1+pch L=0.35u +W='W3' m=1 AD='0.95u*W3' PD='2*(0.95u+W3)' +AS='0.95u*W3' PS='2*(0.95u+W3)'M4 4 5 0 0+nch L=0.35u +W='W4' m=1 AD='0.95u*W4' PD='2*(0.95u+W4)' +AS='0.95u*W4' PS='2*(0.95u+W4)'

VGS1 3 6 0.7vVGS4 5 0 0.7vVin 6 0 sin(0v 0.01v 10Meg)

.tran 0.1ns 600ns

.end

1

2

3

4

5

6Vin

VGS1=0.7V

VGS4=0.7V

Experiment 11-12

• We test the Open Loop Gain of a CMOS amplifier of Example 4-1.

M3 M4

M1 M2

Vss -1.5V

M5

VDD 1.5V

ISS 60u

7u/2u7u/2u

10u/2u 10u/2u

100u/2u

M3 M4

M1 M2

Vss -1.5V

M5

VDD 1.5V

ISS 60u

7u/2u7u/2u

10u/2u 10u/2u

100u/2u

Vin+ Vin-

• Example 4.1 DIFFERENTIAL AMPLIFIER• .PROTECT• .LIB "C:\mm0355v.l" TT• .UNPROTECT

• VDD VDD! 0 1.5V• VSS VSS! 0 -1.5V• MQ1 2 Vi+ 3 VSS! NCH W=10U L=2U• MQ2 Vo+ Vi- 3 VSS! NCH W=10U L=2U• MQ3 2 2 VDD! VDD! PCH W=7U L=2U• MQ4 Vo+ 2 VDD! VDD! PCH W=7U L=2U• MQ5 3 3 VSS! VSS! NCH W=100U L=2U

• .OP

• Vin1 Vi+ 0 AC 1• .AC DEC 100 1 10000000k• Vin2 Vi- 0 0v• .PLOT AC VDB(Vo+)• .END

Experiment 11-13

• We test the Open Loop Gain of a CMOS amplifier of Example 5-6.

• The gain is 3000.

• Classic Two-Stage OP AMP• *********************************• .PROTECT• .OPTION POST• .LIB 'c:\mm0355v.l' TT• .UNPROTECT

• VDD VDD! 0 DC 1.5V• VSS VSS! 0 DC -1.5V• .GLOBAL VDD! VSS!• *******************************************************

• M1 1 V- 3 VSS! NCH W=10U L=2U• M2 2 V+ 3 VSS! NCH W=10U L=2U• M3 VDD! 1 1 VDD! PCH W=3U L=2U• M4 VDD! 1 2 VDD! PCH W=3U L=2U• M5 3 VB VSS! VSS! NCH W=30U L=2U

• M6 6 2 VO VDD! PCH W=4U L=3U• M7 VO VB2 VSS! VSS! NCH W=14U L=2U

• VBIAS5 VB 0 -0.7• VBIAS7 VB2 0 -0.705• *******************************************************

• Rm6 VDD! 6 0• *VDS6 VDD! VO 0V

• .OP• *** Transient Simulation ***

• Vin1 V- 0 AC 1• .AC DEC 100 1 10000000k• Vin2 V+ 0 0v• .PLOT AC VDB(Vo)• .END

1

2

3V-

V+

1

2

3V-

V+

VSS

1

2

3V-

V+

VDD

vo

M6

M7

13.5/2

4/3

M4

M2M1

M5

M3

3/2 3/2

10/210/2

30/2

VBIAS

vin

V I V II V I V

Experiment 11-14

• We test the Open Loop Gain of a CMOS amplifier of Example 6-20.

• The gain was found to be 3000.

Vout

VDD=5V

M4

M3

M2

M1

10u/1u

20u/0.5u

30u/0.5u

30u/1u

0.817V

1.8V

3V

4V

• Ex 6-20• .protect• .lib 'c:\mm0355v.l' TT• .unprotect• .op• .options nomod post

• VDD 1 0 5V• Rm2 vout vout_1 0• Rm1 1 1_1 0

• .param W1=10u W2=20u W3=30u W4=30u

• M4 3 2 1_1 1• +pch L=1u W='W4' m=1• +AD='0.95u*W4' PD='2*(0.95u+W4)' • +AS='0.95u*W4' PS='2*(0.95u+W4)'

• M3 vout 4 3 1• +pch L=0.5u W='W3' m=1• +AD='0.95u*W3' PD='2*(0.95u+W3)' • +AS='0.95u*W3' PS='2*(0.95u+W3)'

• M2 vout_1 6 7 0• +nch L=0.5u W='W2' m=1• +AD='0.95u*W2' PD='2*(0.95u+W2)' • +AS='0.95u*W2' PS='2*(0.95u+W2)'

• M1 7 8 0 0• +nch L=1u W='W1' m=1• +AD='0.95u*W1' PD='2*(0.95u+W1)' • +AS='0.95u*W1' PS='2*(0.95u+W1)'

• Vin 9 0 AC 1• .AC DEC 100 1 1000000k• VG1 8 9 0.817V• VG2 6 0 1.8V• VG3 4 0 3V• VG4 2 0 4V• *.tf v(vout) vin• *.tran 0.1us 600us• .plot VDB(vout_1)• .end

Experiment 11-15

• We test the Open Loop Gain of a CMOS amplifier of Example 6-1.

• The gain was found to be 22.

A typical and simple common gate amplifier isshown below:

• Example 6-1• .protect• .lib 'c:\mm0355v.l' TT• .unprotect• .op• .options nomod post

• VDD 1 0 3.3V• RL 1 11 100k

• .param W1=5u• M1 11 2 3 0• +nch L=0.35u W='W1' m=1• +AD='0.95u*W1' PD='2*(0.95u+W1)' • +AS='0.95u*W1' PS='2*(0.95u+W1)'

• VG 2 0 0.65v• Vin1 3 0 AC 1• .AC DEC 100 1 10000000k

• .PLOT AC VDB(11)• .END

Experiment 11-16

• We test the Open Loop Gain of a CMOS amplifier of Example 6-27.

VDD=3.3V

M7100/2

M8100/2

M5100/2

M6100/2

M350/2

M450/2

M1 50/2

M250/2

M1150/2

VSS=0V

M9100/2

VSS=0V

VBIAS11 = 1.75V

Vout

M10150/2

VBIAS6 = 1.9V

VBIAS9 =0.6V

VBIAS5 = 1.9V

V- V+

VDD=3.3V

1

23

4

5 6

7

Vo

The gain is about 817k.

• Ex 6-20• .protect• .lib 'c:\mm0355v.l' TT• .unprotect• .op• .options nomod post

• VDD 1 0 5V• Rm2 vout vout_1 0• Rm1 1 1_1 0

• .param W1=10u W2=20u W3=30u W4=30u

• M4 3 2 1_1 1• +pch L=1u W='W4' m=1• +AD='0.95u*W4' PD='2*(0.95u+W4)' • +AS='0.95u*W4' PS='2*(0.95u+W4)'

• M3 vout 4 3 1• +pch L=0.5u W='W3' m=1• +AD='0.95u*W3' PD='2*(0.95u+W3)' • +AS='0.95u*W3' PS='2*(0.95u+W3)'

• M2 vout_1 6 7 0• +nch L=0.5u W='W2' m=1• +AD='0.95u*W2' PD='2*(0.95u+W2)' • +AS='0.95u*W2' PS='2*(0.95u+W2)'

• M1 7 8 0 0• +nch L=1u W='W1' m=1• +AD='0.95u*W1' PD='2*(0.95u+W1)' • +AS='0.95u*W1' PS='2*(0.95u+W1)'

• Vin 9 0 AC 1• .AC DEC 100 1 1000000k• VG1 8 9 0.817V• VG2 6 0 1.8V• VG3 4 0 3V• VG4 2 0 4V• *.tf v(vout) vin• *.tran 0.1us 600us• .plot VDB(vout_1)• .end

Experiment 11-17

• We test the Open Loop Gain of a CMOS amplifier of Example 8-1.

• The gain is found to be 42000.

A High Gain Differential AmplifierVDD!VDD!

VBIAS3=0.75

VBIAS67=0V

VBIAS45=-0.737V

V+ V-

Vout

VSS!

M3

M1 M2

M4M5

M6 M7

M8 M9

M10 M11

M1=(10u/2u)*3M2=(10u/2u)*3M3 =(100u/2u)*7M4 =(10u/2u)*M5 =(10u/2u)*M6 =(10u/2u)*M7 =(10u/2u)*M8 =(10u/2u)*3M9 =(10u/2u)*3M10 =(10u/2u)*3M11 =(10u/2u)*3

• Test 1• *********************************• .PROTECT• .OPTION POST• .LIB 'c:\mm0355v.l' TT• .UNPROTECT• .op

• VDD VDD! 0 1.5V• VSS VSS! 0 -1.5V• .GLOBAL VDD! VSS!• *******************************************************

• M1 5 Vi+ 6 6 PCH W=10U L=2U m=3• M2 4 Vi- 6 6 PCH W=10U L=2U m=3• M3 6 VB3 VDD! VDD! PCH W=100U L=2U m=7• M4 5 VB45 VSS! VSS! NCH W=10U L=2U• M5 4 VB45 VSS! VSS! NCH W=10U L=2U• M6 3 VB67 5 VSS! NCH W=10U L=2U• M7 Vo+ VB67 4 VSS! NCH W=10U L=2U• M8 3 3 1 1 PCH W=10U L=2U m=3• M9 Vo+ 3 2 2 PCH W=10U L=2U m=3• M10 1 1 VDD! VDD! PCH W=10U L=2U m=3• M11 2 1 VDD! VDD! PCH W=10U L=2U m=3

• VBIAS3 VB3 0 0.75v• VBIAS45 VB45 0 -0.737v• VBIAS67 VB67 0 0v

• Vin1 Vi- 0 AC 1• .AC DEC 100 1 10000000k• Vin2 Vi+ 0 0v• .PLOT AC VDB(Vo+)• .END

Experiment 11-18

• We test the Open Loop Gain of a Inverting Integrator of Example 8-8.

-

+

Vout

Vin

R1=10k

Virtual ground

0.7nF

• OP AMP• *********************************• .PROTECT• .OPTION POST• .LIB 'c:\mm0355v.l' TT• .UNPROTECT• .op

• vdd vdd! 0 1.5v• vss vss! 0 -1.5v• .global vdd! vss!• *******************************************************• • m1 5 v+ 6 6 pch w=10u l=2u m=3• m2 4 v- 6 6 pch w=10u l=2u m=3• m3 6 vb3 vdd! vdd! pch w=100u l=2u m=7• m4 5 vb45 vss! vss! nch w=10u l=2u• m5 4 vb45 vss! vss! nch w=10u l=2u• m6 3 vb67 5 vss! nch w=10u l=2u• m7 vo vb67 4 vss! nch w=10u l=2u• m8 3 3 1 1 pch w=10u l=2u m=3• m9 vo 3 2 2 pch w=10u l=2u m=3• m10 1 1 vdd! vdd! pch w=10u l=2u m=3• m11 2 1 vdd! vdd! pch w=10u l=2u m=3• • vbias3 vb3 0 0.75v• vbias45 vb45 0 -0.737v• vbias67 vb67 0 0v• *******************************************************• • *cload vo 0 10p

• c2 vo v- 0.7n• R1 vin v- 10k • *** transient simulation ***

• Vin1 vin 0 AC 1• .AC DEC 100 1 10000000k• Vin2 Vi+ 0 0v• .PLOT AC VDB(Vo)• .END

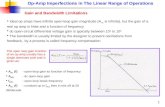

Negative Feedback on Bandwidth

Vin

Ri

Rf

Vout-

+

Experiment 11-19

•Ri=3.3kΩ, Rf=220kΩ

• We use the high gain amplifier whose gain is 817k. The ckt of this amplifier is as follows:

VDD=3.3V

M7100/2

M8100/2

M5100/2

M6100/2

M350/2

M450/2

M1 50/2

M250/2

M1150/2

VSS=0V

M9100/2

VSS=0V

VBIAS11 = 1.75V

Vout

M10150/2

VBIAS6 = 1.9V

VBIAS9 =0.6V

VBIAS5 = 1.9V

V- V+

VDD=3.3V

1

23

4

5 6

7

Vo

Open loop• open loop test• .PROTECT• .OPTION POST• .LIB "C:\mm0355v.l" TT• .UNPROTECT• .op

• VDD VDD! 0 3.3V• VSS VSS! 0 0.025V

• M1 1 1 VDD! VDD! PCH W=50U L=2U• M2 2 1 VDD! VDD! PCH W=50U L=2U• M3 3 3 1 VDD! PCH W=50U L=2U• M4 4 3 2 VDD! PCH W=50U L=2U• M5 3 VB5 5 VSS! NCH W=100U L=2U• M6 4 VB6 6 VSS! NCH W=100U L=2U• M7 5 Vi- 7 VSS! NCH W=100U L=2U• M8 6 Vi+ 7 VSS! NCH W=100U L=2U• M9 7 VB9 VSS! VSS! NCH W=100U L=2U• M10 Vo 4 VDD! VDD! PCH W=150U L=2U• M11 Vo VB11 VSS! VSS! NCH W=50U L=2U

• VBIAS5 VB5 0 1.9V• VBIAS6 VB6 0 1.9V• VBIAS9 VB9 0 0.6V• VBIAS1 VB11 0 1.75V • VB Vi- 0 1.65v• Vin1 11 0 AC 1• .AC DEC 100 1 100000k• Vin2 Vi+ 11 1.65v

• *Ri 12 0 3.3k• *Rf 12 Vo 220k

• .PLOT AC VDB(Vo)• .END

• fc(ol)=1.3kHz and open loop gain is 100dB.

• fc(cl)=100kHz

Close loop• close loop test• .PROTECT• .OPTION POST• .LIB "C:\mm0355v.l" TT• .UNPROTECT• .op

• VDD VDD! 0 3.3V• VSS VSS! 0 0.025V

• M1 1 1 VDD! VDD! PCH W=50U L=2U• M2 2 1 VDD! VDD! PCH W=50U L=2U• M3 3 3 1 VDD! PCH W=50U L=2U• M4 4 3 2 VDD! PCH W=50U L=2U• M5 3 VB5 5 VSS! NCH W=100U L=2U• M6 4 VB6 6 VSS! NCH W=100U L=2U• M7 5 Vi- 7 VSS! NCH W=100U L=2U• M8 6 Vi+ 7 VSS! NCH W=100U L=2U• M9 7 VB9 VSS! VSS! NCH W=100U L=2U• M10 Vo 4 VDD! VDD! PCH W=150U L=2U• M11 Vo VB11 VSS! VSS! NCH W=50U L=2U

• VBIAS5 VB5 0 1.9V• VBIAS6 VB6 0 1.9V• VBIAS9 VB9 0 0.6V• VBIAS1 VB11 0 1.75V • VB Vi- 12 1.65v• Vin1 11 0 AC 1• .AC DEC 100 1 100000k• Vin2 Vi+ 11 1.65v

• Ri 12 0 3.3k• Rf 12 Vo 220k

• .PLOT AC VDB(Vo)• .END

Vin

Ri

Rf

Vout-

+

Experiment 11-20

•Ri=3.3kΩ, Rf=220kΩ

We use the high gain amplifier whose gain is 42k. The ckt of this amplifier is as follows:

VDD!VDD!

VBIAS3=0.75

VBIAS67=0V

VBIAS45=-0.737V

V+ V-

Vout

VSS!

M3

M1 M2

M4M5

M6 M7

M8 M9

M10 M11

M1=(10u/2u)*3M2=(10u/2u)*3M3 =(100u/2u)*7M4 =(10u/2u)*M5 =(10u/2u)*M6 =(10u/2u)*M7 =(10u/2u)*M8 =(10u/2u)*3M9 =(10u/2u)*3M10 =(10u/2u)*3M11 =(10u/2u)*3

• fc(ol)=25kHz.

Open loop• open loop• *********************************• .PROTECT• .OPTION POST• .LIB 'c:\mm0355v.l' TT

• .UNPROTECT• .op

• VDD VDD! 0 1.5V• VSS VSS! 0 -1.5V• .GLOBAL VDD! VSS!• *******************************************************

• M1 5 Vi+ 6 6 PCH W=10U L=2U m=3• M2 4 Vi- 6 6 PCH W=10U L=2U m=3• M3 6 VB3 VDD! VDD! PCH W=100U L=2U m=7• M4 5 VB45 VSS! VSS! NCH W=10U L=2U• M5 4 VB45 VSS! VSS! NCH W=10U L=2U• M6 3 VB67 5 VSS! NCH W=10U L=2U• M7 VO VB67 4 VSS! NCH W=10U L=2U• M8 3 3 1 1 PCH W=10U L=2U m=3• M9 VO 3 2 2 PCH W=10U L=2U m=3• M10 1 1 VDD! VDD! PCH W=10U L=2U m=3• M11 2 1 VDD! VDD! PCH W=10U L=2U m=3

• VBIAS3 VB3 0 0.75v• VBIAS45 VB45 0 -0.737v• VBIAS67 VB67 0 0v

• Vin1 Vi+ 0 AC 1• .AC DEC 100 1 500000k• Vin2 Vi- 0 0v

• *Ri Vi- 0 3.3k• *Rf Vi- Vo 220k

• .PLOT AC VDB(Vo)• .END

• fc(cl)=30MHz.

Close loop• close loop• *********************************• .PROTECT• .OPTION POST• .LIB 'c:\mm0355v.l' TT

• .UNPROTECT• .op

• VDD VDD! 0 1.5V• VSS VSS! 0 -1.5V• .GLOBAL VDD! VSS!• *******************************************************

• M1 5 Vi+ 6 6 PCH W=10U L=2U m=3• M2 4 Vi- 6 6 PCH W=10U L=2U m=3• M3 6 VB3 VDD! VDD! PCH W=100U L=2U m=7• M4 5 VB45 VSS! VSS! NCH W=10U L=2U• M5 4 VB45 VSS! VSS! NCH W=10U L=2U• M6 3 VB67 5 VSS! NCH W=10U L=2U• M7 VO VB67 4 VSS! NCH W=10U L=2U• M8 3 3 1 1 PCH W=10U L=2U m=3• M9 VO 3 2 2 PCH W=10U L=2U m=3• M10 1 1 VDD! VDD! PCH W=10U L=2U m=3• M11 2 1 VDD! VDD! PCH W=10U L=2U m=3

• VBIAS3 VB3 0 0.75v• VBIAS45 VB45 0 -0.737v• VBIAS67 VB67 0 0v

• Vin1 Vi+ 0 AC 1• .AC DEC 100 1 500000k

• Ri Vi- 0 3.3k• Rf Vi- Vo 220k

• .PLOT AC VDB(Vo)• .END

Vin

Ri

Rf

Vout-

+

Experiment 11-21

Ri=1k Ω, Rf=47kΩ

We use the high gain amplifier whose gain is 42k. The ckt of this amplifier is as follows:

VDD!VDD!

VBIAS3=0.75

VBIAS67=0V

VBIAS45=-0.737V

V+ V-

Vout

VSS!

M3

M1 M2

M4M5

M6 M7

M8 M9

M10 M11

M1=(10u/2u)*3M2=(10u/2u)*3M3 =(100u/2u)*7M4 =(10u/2u)*M5 =(10u/2u)*M6 =(10u/2u)*M7 =(10u/2u)*M8 =(10u/2u)*3M9 =(10u/2u)*3M10 =(10u/2u)*3M11 =(10u/2u)*3

• fc(ol)=25kHz.

Open loop• open loop• *********************************• .PROTECT• .OPTION POST• .LIB 'c:\mm0355v.l' TT

• .UNPROTECT• .op

• VDD VDD! 0 1.5V• VSS VSS! 0 -1.5V• .GLOBAL VDD! VSS!• *******************************************************

• M1 5 Vi+ 6 6 PCH W=10U L=2U m=3• M2 4 Vi- 6 6 PCH W=10U L=2U m=3• M3 6 VB3 VDD! VDD! PCH W=100U L=2U m=7• M4 5 VB45 VSS! VSS! NCH W=10U L=2U• M5 4 VB45 VSS! VSS! NCH W=10U L=2U• M6 3 VB67 5 VSS! NCH W=10U L=2U• M7 VO VB67 4 VSS! NCH W=10U L=2U• M8 3 3 1 1 PCH W=10U L=2U m=3• M9 VO 3 2 2 PCH W=10U L=2U m=3• M10 1 1 VDD! VDD! PCH W=10U L=2U m=3• M11 2 1 VDD! VDD! PCH W=10U L=2U m=3

• VBIAS3 VB3 0 0.75v• VBIAS45 VB45 0 -0.737v• VBIAS67 VB67 0 0v

• Vin1 Vi- 0 AC 1• .AC DEC 100 1 500000k• Vin2 Vi+ 0 0v

• *Ri Vi- 11 1k• *Rf Vi- Vo 47k

• .PLOT AC VDB(Vo)• .END

• fc(cl)=25MHz.

Close loop• close loop• *********************************• .PROTECT• .OPTION POST• .LIB 'c:\mm0355v.l' TT

• .UNPROTECT• .op

• VDD VDD! 0 1.5V• VSS VSS! 0 -1.5V• .GLOBAL VDD! VSS!• *******************************************************

• M1 5 Vi+ 6 6 PCH W=10U L=2U m=3• M2 4 Vi- 6 6 PCH W=10U L=2U m=3• M3 6 VB3 VDD! VDD! PCH W=100U L=2U m=7• M4 5 VB45 VSS! VSS! NCH W=10U L=2U• M5 4 VB45 VSS! VSS! NCH W=10U L=2U• M6 3 VB67 5 VSS! NCH W=10U L=2U• M7 VO VB67 4 VSS! NCH W=10U L=2U• M8 3 3 1 1 PCH W=10U L=2U m=3• M9 VO 3 2 2 PCH W=10U L=2U m=3• M10 1 1 VDD! VDD! PCH W=10U L=2U m=3• M11 2 1 VDD! VDD! PCH W=10U L=2U m=3

• VBIAS3 VB3 0 0.75v• VBIAS45 VB45 0 -0.737v• VBIAS67 VB67 0 0v

• Vin1 11 0 AC 1• .AC DEC 100 1 500000k• Vin2 Vi+ 0 0v

• Ri Vi- 11 1k• Rf Vi- Vo 47k

• .PLOT AC VDB(Vo)• .END

Vin

Ri

Rf

Vout-

+

Experiment 11-22

•Ri=3.3kΩ, Rf=220kΩ

M3 M4

M1 M2

Vss -1.5V

M5

VDD 1.5V

ISS 60u

7u/2u7u/2u

10u/2u 10u/2u

100u/2u

M3 M4

M1 M2

Vss -1.5V

M5

VDD 1.5V

ISS 60u

7u/2u7u/2u

10u/2u 10u/2u

100u/2u

Vin+ Vin-

•The ckt of this amplifier is as follows:

• fc(ol)=10MHz.

Open loop• Example 4.1 DIFFERENTIAL AMPLIFIER• .PROTECT• .LIB "C:\mm0355v.l" TT• .UNPROTECT

• VDD VDD! 0 1.5V• VSS VSS! 0 -1.5V• MQ1 2 Vi+ 3 VSS! NCH W=10U L=2U• MQ2 Vo+ Vi- 3 VSS! NCH W=10U L=2U• MQ3 2 2 VDD! VDD! PCH W=7U L=2U• MQ4 Vo+ 2 VDD! VDD! PCH W=7U L=2U• MQ5 3 3 VSS! VSS! NCH W=100U L=2U

• .OP

• Vin1 Vi+ 0 AC 1• .AC DEC 100 1 10000000k• Vin2 Vi- 0 0v• *Ri Vi- 0 3.3k• *Rf Vi- Vo+ 220k

• .PLOT AC VDB(Vo+)• .END

• fc(cl)=55MHz.

Close loop• Example 4.1 DIFFERENTIAL AMPLIFIER• .PROTECT• .LIB "C:\mm0355v.l" TT• .UNPROTECT

• VDD VDD! 0 1.5V• VSS VSS! 0 -1.5V• MQ1 2 Vi+ 3 VSS! NCH W=10U L=2U• MQ2 Vo+ Vi- 3 VSS! NCH W=10U L=2U• MQ3 2 2 VDD! VDD! PCH W=7U L=2U• MQ4 Vo+ 2 VDD! VDD! PCH W=7U L=2U• MQ5 3 3 VSS! VSS! NCH W=100U L=2U

• .OP

• Vin1 Vi+ 0 AC 1• .AC DEC 100 1 10000000k• *Vin2 Vi- 10 0v• Ri Vi- 0 3.3k• Rf Vi- Vo+ 220k

• .PLOT AC VDB(Vo+)• .END

Vin

Ri

Rf

Vout-

+

Experiment 11-23

Ri=1k Ω, Rf=47kΩ

• We use the high gain amplifier whose gain is 817k. The ckt of this amplifier is as follows:

VDD=3.3V

M7100/2

M8100/2

M5100/2

M6100/2

M350/2

M450/2

M1 50/2

M250/2

M1150/2

VSS=0V

M9100/2

VSS=0V

VBIAS11 = 1.75V

Vout

M10150/2

VBIAS6 = 1.9V

VBIAS9 =0.6V

VBIAS5 = 1.9V

V- V+

VDD=3.3V

1

23

4

5 6

7

Vo

• fc(ol)=500Hz.

Open loop• open loop• .PROTECT• .OPTION POST• .LIB "C:\mm0355v.l" TT• .UNPROTECT• .op

• VDD VDD! 0 3.3V• VSS VSS! 0 0.07V

• M1 1 1 VDD! VDD! PCH W=50U L=2U• M2 2 1 VDD! VDD! PCH W=50U L=2U• M3 3 3 1 VDD! PCH W=50U L=2U• M4 4 3 2 VDD! PCH W=50U L=2U• M5 3 VB5 5 VSS! NCH W=100U L=2U• M6 4 VB6 6 VSS! NCH W=100U L=2U• M7 5 Vi- 7 VSS! NCH W=100U L=2U• M8 6 Vi+ 7 VSS! NCH W=100U L=2U• M9 7 VB9 VSS! VSS! NCH W=100U L=2U• M10 Vo 4 VDD! VDD! PCH W=150U L=2U• M11 Vo VB11 VSS! VSS! NCH W=50U L=2U

• VBIAS5 VB5 0 1.9V• VBIAS6 VB6 0 1.9V• VBIAS9 VB9 0 0.6V• VBIAS1 VB11 0 1.75V • VB Vi- 11 1.65v• Vin1 11 0 AC 1• .AC DEC 100 1 10000k• Vin2 Vi+ 0 1.65v

• *Ri 11 12 1k• *Rf 11 Vo 47k

• .PLOT AC VDB(Vo)• .END

• fc(cl)=70kHz.

Close loop• close loop• .PROTECT• .OPTION POST• .LIB "C:\mm0355v.l" TT• .UNPROTECT• .op

• VDD VDD! 0 3.3V• VSS VSS! 0 0.07V

• M1 1 1 VDD! VDD! PCH W=50U L=2U• M2 2 1 VDD! VDD! PCH W=50U L=2U• M3 3 3 1 VDD! PCH W=50U L=2U• M4 4 3 2 VDD! PCH W=50U L=2U• M5 3 VB5 5 VSS! NCH W=100U L=2U• M6 4 VB6 6 VSS! NCH W=100U L=2U• M7 5 Vi- 7 VSS! NCH W=100U L=2U• M8 6 Vi+ 7 VSS! NCH W=100U L=2U• M9 7 VB9 VSS! VSS! NCH W=100U L=2U• M10 Vo 4 VDD! VDD! PCH W=150U L=2U• M11 Vo VB11 VSS! VSS! NCH W=50U L=2U

• VBIAS5 VB5 0 1.9V• VBIAS6 VB6 0 1.9V• VBIAS9 VB9 0 0.6V• VBIAS1 VB11 0 1.75V • VB Vi- 11 1.65v• Vin1 12 0 AC 1• .AC DEC 100 1 10000k• Vin2 Vi+ 0 1.65v

• Ri 11 12 1k• Rf 11 Vo 47k

• .PLOT AC VDB(Vo)• .END