INF1400 – Kap 10 CMOS Teknologi

-

Upload

ivy-michael -

Category

Documents

-

view

53 -

download

0

description

Transcript of INF1400 – Kap 10 CMOS Teknologi

INF1400 – Kap INF1400 – Kap 1010

CMOS CMOS TeknologiTeknologi

Hovedpunkter

MOS transistoren

• Komplementær MOS (CMOS)

• CMOS teknologiutvikling

• CMOS eksempler

- Inverter- NAND / NOR

- Fulladder

NMOS transistoren

NMOS (Negative doped Metal Oxide Silicon)

– En 3 (4) terminals komponent

Symbol:

Source

Drain

Gate

Source

Drain

Gate

– Spenningen på gate bestemmer om transistoren leder strøm mellom drain og source terminalene

NMOS transistoren

n+ n+

p-

poly

p- : Svakt positivt dopet silisiumn+ : Sterkt negativt dopet silisium (ledende)poly : Polykrystalinskt silisium (ledende)

n+ n+poly

p-Source

Silisiumskive

IsolasjonGate

Silisiumskive

Sett fra siden

Drain

Ledning Ledning

Sett ovenifra

NMOS transistoren

n+ n+

p-

polySource

IsolasjonGate

Silisium skive

Drain

Strøm (elektroner) kan ikke gå i fra p- til n+ materiale

Strøm kan derfor i utgangspunktet ikke gå i fra source til drain

n+ og poly leder strøm, p- leder også strøm til en viss grad

NMOS transistoren

n+ n+

p-

Source

IsolasjonGate

Silisium skive

Drain

Hvis man setter en positiv spenning på gate terminalen (5V)* i forhold til silisiumskiven, dannes det et n+ lag under gate terminalen0V

5V

Nå kan det gå strøm i mellom source og drain

* Forutsetter en 5V prosess i alle påfølgende forklaringer

NMOS transistorenNMOS brukt som styrt bryter (digital anvendelse)

n+ n+

p-

Gate

0V

0V

Metall- ledning

Metall- lednin

g Bryter ekvivalent

n+ n+

p-

Gate

0V

5V

Metall- ledning

Metall- lednin

gBryter

ekvivalent

PMOS transistoren

PMOS (Positive doped Metal Oxide Silicon)

– En 3 (4) terminals-komponent

Symbol:

Drain

Source

Gate

Drain

Source

Gate

– Spenningen på gate bestemmer om transistoren leder strøm i mellom drain og source terminalene

PMOS transistoren

p+ p+

p-

poly

n- : Svakt negativt dopet silisiump+ : Sterkt positivt dopet silisium (ledende)poly : Polykrystalinskt silisium (ledende)

p+ p+poly

p-

Source

Silisiumskive

IsolasjonGate

Silisiumskive

Sett fra sidenSett ovenifra

Drain

n- N-brønn

N-brønn

n-

PMOS transistoren

p+ p+

p-

polySource

Gate

Silisium skive

Drain

Strøm (elektroner) kan ikke gå i fra p+ til n- materiale

Strøm kan derfor i utgangspunktet ikke gå i fra drain til source

p+ og poly leder strøm, n- leder også strøm til en viss grad

n- N-brønn

PMOS transistoren

p+ p+

p-

Source

Gate

Silisium skive

Drain

Hvis man setter en negativ spenning på gate- terminalen (-5V) i forhold til brønnen, dannes det et p+ lag under gate- terminalen

5V

0V

Nå kan det gå strøm mellom drain og source

n- N-brønn

PMOS transistorenPMOS brukt som styrt bryter (digital anvendelse)

p+ p+

Gate

5V

5V

Metall- ledning

Metall- lednin

g Bryter ekvivalent

n-

Bryter ekvivalent

p+ p+

Gate

5V

0V

Metall- ledning

Metall- lednin

g

n-

CMOS kretserCMOS (Complementary MOS) inverter

x x´

gnd

p+5Vn-

p+n+ n+

p- 0V

n-

p-

x

x´

VddGnd

Sett fra siden

Sett ovenifraKontakt fra metall til n+

Metall Poly

Vdd

CMOS inverterTilstand 1 - 0V inn, 5V ut

0V 5V

p+5Vn-

p+n+ n+

p- 0V

n-

p-

0V

5V

VddGnd

Sett fra siden

Sett ovenifra

0V0V5V

VddGnd

e-

Vdd

Gnd

CMOS inverterTilstand 2 - 5V inn 0V ut

5V 0V

0V

p+5Vn-

p+n+ n+

p- 0V

n-

p-

5V

0V

VddGnd

Sett fra siden

Sett ovenifra

5V5V 0V

VddGnd

e-

Vdd

Gnd

CMOS NAND-krets

Både A og B må være 5V for å koble utgangen ned til 0V

A B

A

B

(AB)´

Vdd

Gnd

Vdd

CMOS NAND-krets

B A

A

B

(AB)´

Skjema

n-

p-

Vdd

B A

(AB)´

Utlegg

Gnd

0V

5V

CMOS NOR-krets

Det holder at enten A eller B er 5V for å koble utgangen ned til 0V

A

B

AB

(A+B)´

CMOS NOR-krets

Skjema

A

B

BA

(A+B)´

n-Vdd

Gnd

A B

(A+B)´

Utlegg

0V

5V

CMOS-kretser

A

B

AB

(C(A+B))´

C

C

En enkel CMOS port kan implementere generelle funksjoner Eksempel: F = (C(A+B))´

n-

Gnd

B C

(C(A+B))´

A

Vdd p-

CMOS-kretserEksempel: Fulladder

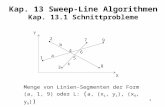

CMOS - teknologiutvikling

Skalering – reduksjon i geometriske størrelser

n+ n+

p-

poly Isolasjon: Silisiumoksyd

Silisiumskive

Transistorlengde

• Gate isolasjon: Vanlig tykkelse 1.2nm – 7nm State of the art: <3 atomlagGevinst ved reduksjon i tykkelse: Raskere transistor

• Transistor lengde: Vanlig lengde: 0.06mm-0.35mmState of the art: <32nm Gevinst ved reduksjon i lengde: Raskere transistor

CMOS - teknologiutvikling

• Flere metall lag – Mer 3 dimensjonal ledningsstrukturVanlig antall metall lag: 5 - 12

Eksempel: Xilinx – Virtex V FPGA

65nm transistorlengde, 12 metall lag, Vddkjerne = 1V

Sideeffekt ved skalering: Forsyningsspenningen må reduseres

CMOS - teknologiutvikling

32nm

Transistor

Eksempel på mikrochip overflate

Metall ledninger

CMOS - teknologiutvikling

Intel 90nm prosess

CMOS - teknologiutvikling

Intel 90nm prosess

Tverrsnitt av metall ledinger i 7 lag

CMOS - teknologiutvikling

Kurs i CMOS design ved IFI

• INF3420/4420 - Prosjektoppgave i mikroelektronikk (vår)

• INF3400/4400 - VLSI Design (vår)

Oppsummering

MOS transistoren

• Komplementær MOS (CMOS)

• CMOS eksempler

• CMOS teknologi 2009

• Designeksempler (Cadence)

- Inverter- NAND / NOR

- Fulladder