Enel3de a Syncronous Sequential Design

-

Upload

papiki-radebe -

Category

Documents

-

view

221 -

download

0

Transcript of Enel3de a Syncronous Sequential Design

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 1/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

ASYNCHRONOUS SEQUENTIAL

CIRCUITS-DESIGN

DR T WALINGO

LECTURE 7

1

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 2/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

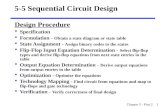

DESIGN PROCEDURESTEPS

• Obtain a primitive flow table from the given specification.

•

Reduce the flow table by merging rows in the primitive flowtable. (STATE REDUCTION)

• Assign binary states variables to each row of the reduced flowtable to obtain the transition table. (STATE ASSIGNMENT)

• Assign output values to the dashes associated with the unstable

states to obtain the output maps.• Simplify the Boolean functions of the excitation and output

variables and draw the logic diagram.

SUMMARY OF STEPS

A. From the specification obtain the primitive table.B. From the primitive table obtain the transition and output

table.

C. Implement your circuit.

2

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 3/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

EXAMPLE 1 : GATED LATC DESIGNQUESTION

• Design a gated latch circuit with two inputs, G (gate) and D (data), and one output Q.The gated latch is a memory element that accepts the value of D when G = 1 and retainsthis value after G goes to 0. Once G = 0, a change in D does not change the value of the

output Q.

UNDERSTANDING QUESTION

Principle of operation - Input D, Gate G

D goes through when G is High

In memory when G is low

Step 1: Primitive Flow Table

A primitive flow table is a flow table with only one stable total state in each row.

The total state consists of the internal state combined with the input.

To derive the primitive flow table, first a table with all possible total states in the systemis needed.

Identify and circle the stable states and add the information (other states) to retainmemory.

Note that the one input changes at a time DG= 01 to 10 & 11 to 00 not allowed There are other ways but will be discussed with other examples

3

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 4/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

EXAMPLE 1 - STEP 1: PRIMITIVE FLOW TABLE INFORMATION

• All combinations are required

• All input combinations are 01, 11, 00, 10. For thisthe output Q can be 0 or 1.

• Note that a double input change is not allowed-Fundamental mode.

• Primitive table has one row for a stable state.

• Step A: Create a table with all possiblecombinations.

• Step B: Mark the possible stable states – diagonals – DG can be 00 and Q=0

– DG can be 00 and Q=1

• Step C: Mark the impossible states- in blue.

– DG cannot be 11 and the output is zero

– DG cannot be 01 and the output is 1

– Remove the impossible states.

• Step D: Label, circle and insert outputs to the stablestates.

4

DG Q

00 01 11 10

_ 0

_ 0

_ 0

_ 0

_ 1

_ 1

_ 1

_ 1

DG Q

00 01 11 10

a,0 0

b,0 0

c,0 0

d,1 1

e,1 1

f,1 1

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 5/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

EXAMPLE 1 - STEP 1 PRIMITIVE FLOW TABLE INFORMATION

• Step E: Determine the un allowed states of arow and mark with don't cares ‘-,-’ or x,x.

– States where two inputs changes from

stable state. – Marked in yellow.

• Step F: Determine the unstable states and fillthem in the table.

– Reasonable unstable states should bechosen following the principles of operation

of the design.

• Preferably in the same column.

• The output may be considered in thechoice in case of multiple states in thecolumn.

•

When x changes from 00 to 01 areasonable change is from a to b.

– Mark the outputs of the unstable states asdon't cares.

– Marked in white.

• Note: Red represents circled stable state.

DG Q

00 01 11 10

a,0 b,x x,x c,x 0

a,x b,0 e,0 x,x 0

a,x x,x e,x c,0 0

d,1 b,x x,x f,x 1

x,x b,x e,1 f,x 1

d,x x,x e,x f,1 1

DG

00 01 11 10

a a,0 b,x x,x c,x

b a,x b,0 e,x x,x

c a,x x,x e,x c,0

d d,1 b,x x,x f,x

e x,x b,x e,1 f,x

f d,x x,x e,x f,1

00 01 11 10

a a,0 b,x x,x c,x

b a,x b,0 e,x x,x

c a,x x,x e,x c,0

d d,1 b,x x,x f,x

e x,x b,x e,1 f,x

f d,x x,x e,x f,1

5

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 6/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

EXAMPLE 1 - STEP 2: REDUCTION OF THE PRIMITIVE FLOW TABLE

• Rules for merging two or more rows intoone:

– Use the methods of row reduction or

implication table on equivalent states(done before).

• Presence of non conflicting statesand outputs in each of the columns.(two parts showing candidates formerging - no conflicting entries ineach of the four columns)

– Whenever, one state symbol and don’t care entries are encountered in the samecolumn, the state is listed in the mergedrow.

– If the state is circled in one of the rows,it is also circled in the merged row.

– The output state is included with eachstable state in the merged row.

• Note: Red represents circled stable state.

DG

00 01 11 10

a a,0 b,x x,x c,x

b a,x b,0 e,x x,x

c a,x x,x e,x c,0

d d,1 b,x x,x f,x

e x,x b,x e,1 f,x

f d,x x,x e,x f,1

00 01 11 10

abc a,0 b,0 e,x c,0

def d,1 b,x e,1 f,1

00 01 11 10

a a,0 a,0 b,x a,0

b b,1 a,x b,1 b,1

6

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 7/32UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

EXAMPLE 1 - STEP 3: TRANSITION TABLE AND LOGIC DIAGRAM

• State Assignment

– Assign a binary value to eachstate. This converts the flow tableto a transition table.

– In assigning binary states, caremust be taken to ensure that thecircuit will be free of criticalraces.

– Set a=0, b=1

• Excitation and output tables

– Simplify these tables and expressas Boolean function

– Value of Y and output Q is asgiven.

– Use don't cares for furthersimplification – give them a value

that simplifies your circuitfurther.

• Use combinational logic diagram withfeedback

Don’t cares used to make output Q = Y

7

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 8/32UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

EXAMPLE 1 – STEP 3 - IMPLEMENTING WITH SR LATCH

• The procedure is as before fromthe transition table.

• Given a transition table derive a

pair of maps for Si and Ri. – In filling the table determine

from the excitation table theS and R values that will givethe state transition for thecombinations indicated in

the transition table.• Derive the simplified Boolean

functions for each Si and Ri.From the map

• Draw the logic diagram

– for NAND latches, use the

complemented values of those Si and Ri.

– Note the figure has used aNAND latch for a change.

8

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 9/32UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

SUMMARY OF DESIGN PROCEDURE• Problem definition: state the design specifications.

• Interpretation: Obtain a primitive flow table from the given designspecifications (most difficult).

• State reduction: reduce flow table by merging rows in primitive flowtable (implication table, merger diagram – as done before).

– Reduce equivalent states and compatible states.

– Done in earlier chapter.

•State assignment: assign binary state variables to each row of thereduced flow table to obtain the transition table

– Eliminates any possible critical races.

• Output assignment: assign suitable output values to the don't caresassociated with the unstable states to obtain the output maps.

• Simplification: Simplify the Boolean functions of the excitation andoutput variables and draw the logic diagram.

– Can be implemented using normal gates.

– can be implemented using SR latches.

9

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 10/32UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

IMPLICATION TABLES – FULLY SPECIFIED STATES - REVISED

10

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 11/32UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

IMPLICATION TABLES – INCOMPLETELY SPECIFIED STATES - REVISED

11

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 12/32UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

IMPLICATION TABLES – INCOMPLETELY SPECIFIED STATES - REVISED

12

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 13/32UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

IMPLICATION TABLES – INCOMPLETELY SPECIFIED STATES - REVISED

13

no implied states

in one group

RACE FREE STATE ASSIGNMENT

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 14/32UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

RACE FREE STATE ASSIGNMENT

14

• Race-free: avoiding critical races

– Only one variable changes at any given time.

– may allow noncritical race.

• Adjacent assignment

– Condition: binary values of states between which transitions occur only

differ in one variable.

• tedious process: test and verify each possible transition between two

stable states. – m variables required for a flow table with n rows: 2m ≥ n

• No critical race for assigning a single variable to a flow table with two

rows.

• Transition diagram: pictorial representation of all required transitions between

rows

– Try to find only one binary variable changes during each state transition.

– If critical races exist, add extra rows to obtain race-free assignment.

RACE FREE ASSIGNMENT 3 ROW EXAMPLE

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 15/32UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

RACE FREE ASSIGNMENT – 3 ROW EXAMPLE

15

RACE FREE ASSIGNMENT 3 ROW EXAMPLE

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 16/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

RACE FREE ASSIGNMENT -3 ROW EXAMPLE

16

RACE FREE ASSIGNMENT 4 ROW EXAMPLE

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 17/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

RACE FREE ASSIGNMENT – 4 ROW EXAMPLE

17

RACE FREE ASSIGNMENT 4 ROW EXAMPLE

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 18/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

RACE FREE ASSIGNMENT – 4 ROW EXAMPLE

18

HAZARDS

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 19/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

HAZARDS

• In the design of asynchronous sequential circuit, the circuit

– must be operated in fundamental mode with only one input

changing at any time, and – must be free of critical races.

• Hazards: unwanted switching transients at the output

– because different paths exhibit different propagation delays.

– May cause the circuit to malfunction.

• in combinational circuits: may cause temporary false-

output value.

• in asynchronous sequential circuits: may result in a

transition to a wrong stable state.

– Need to check for possible hazards and determine whether

causing improper operations.

19

HAZARDS

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 20/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

HAZARDS

20

HAZARD TYPES

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 21/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

HAZARD TYPES

21

HAZARDS

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 22/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

HAZARDS

22

HAZARDS

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 23/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

HAZARDS

23

Hazard exists whenever 2 adjacent 1sin a K-map are not covered by a

single product.

To remove all static hazards, find a

cover that includes each pair of

adjacent 1s.

Draw final circuit

HAZARDS ELIMINATION

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 24/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

HAZARDS - ELIMINATION

24

ESSENTIAL HAZARDS

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 25/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

ESSENTIAL HAZARDS

• An essential hazard is the result of the effects of a

single input variable change reaching one

feedback path before another feedback path.

• Essential hazards cannot be corrected by adding

redundant gates as in static hazards.

• They can always be eliminated in a realization by

the insertion of sufficient delays in the feedback

paths.

• Facility in doing this comes only with experience.

25

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 26/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

...

26

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 27/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

…

27

CLASS EXERCISE

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 28/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

CLASS EXERCISE

1. Design a latch circuit with one input T and one

output Q. The latch is a memory element that

toggles the value of Q when T = 1 and retains

this value after T goes to 0.

2. Design a negative edge triggered T FF.

28

CLASS EXERCISE 1: DERIVE AND CONSTRUCT A `T' FLIP-FLOP

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 29/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

CLASS EXERCISE 1: DERIVE AND CONSTRUCT A T FLIP-FLOP

• Step 1: Obtaining the state table

Principle of operation. Toggles when the input is 1 else keeps its state

T Q

0 1

_ 0

_ 0

_ 1

_ 1

T Q

0 1

a,0 0

b,0 0

c,1 1

d,1 1

T Q

0 1

a,0 d,1 0

a,0 b,0 0

c,1 b,0 1

c,1 d,1 1

Obtaining the primitive flow table.

Determine all the possible states. For every input combination how manyoutputs would you have. Table 1

Name the primitive stable states. Table 2.

Fill in the next temporary states observing the rules. Table 3

E.g. From (a,0) when input changes by 1, The circuit will toggle to an output

of zero and hence the best next state is (d,0).

Note that the operation is in the fundamental mode.

T

0 1

a a,0 d,x

b a,x b,0

c c,1 b,x

d c,x d,1

29

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 30/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

… • Step2: State Reduction – No further state reduction

• Step 3: State assignment

a b

d c

00 01

11 10

No cross transitions hence straightforward race free assignment

T

0 1

00 00,0 10,x

00 00,x 01,0

11 11,1 01x

10 11,x 10,1

Step C: Implementation

1 0

0 0

0 1

1 1

y1 y2

00

01

11

10

0 1

1 1

0 1

0 0

1 0

y1 y2

00

01

11

10

0 1

1 x

x 0

0 x

x 1

y1 y2

00

01

11

10

0 1

211yT yT Y

212Ty yT Y

1 y Z

T

0 1

a a,0 d,x

b a,x b,0

c c,1 b,x

d c,x d,1

30

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 31/32

UNIVERSITY OF KWAZULU-NATAL DIGITAL ELECTRONICS SERIES

…

• Checking carefully we identify a hazards in the

first and second term and adjust it. Our final

equations are

21211y y yT yT Y 21212

y yTy yT Y

1

y Z

Note: Student to implement the circuit using theNAND gates

31

CLASS EXERCISE 2 -SOLUTION

8/3/2019 Enel3de a Syncronous Sequential Design

http://slidepdf.com/reader/full/enel3de-a-syncronous-sequential-design 32/32

CLASS EXERCISE 2 -SOLUTION

• Students to finish the design.