AC1 –Micro-Arquitectura: DataPath do MIPS1 Organização ou MicroArquitectura DataPath MIPS32.

Datapath I

-

Upload

aman-dhamija -

Category

Documents

-

view

224 -

download

0

Transcript of Datapath I

-

8/18/2019 Datapath I

1/22

Outline Processor Design

–

• A simple

implementation:

Single

Cycle

–

• Performance

considerations• u cyc e es gn

– Data path and control

• croprogramme

con ro

• Exception handling

2

-

8/18/2019 Datapath I

2/22

•

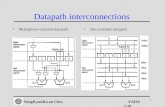

• Design overview

• Division into ata pat an contro

• Building blocks

combinational

and

sequential

• Clock and timings

•

-

8/18/2019 Datapath I

3/22

• Arithmetic lo ic instructions

–add,

sub,

and,

or,

slt•

–lw,

sw• on ro ow ns ruc ons

–beq, jIncremental

changes

in

the

design

to

include

other instructions will be discussed later

-

8/18/2019 Datapath I

4/22

• Use the ro ram counter PC to su l

instruction

address

• Get the instruction from memor

• Read registers

do

-

8/18/2019 Datapath I

5/22

InstructionData

PC Address

Instruction

Register

Address

Reg#

Data

Memory

ALU

Reg#

Data

6

-

8/18/2019 Datapath I

6/22

DATA PATH

control status

CONTROLLER

-

8/18/2019 Datapath I

7/22

• Elements that

operate

on

data

values

combinational

– Output is function of current input

– No memor

• Elements that contain state (sequential)

– Out ut is function of current and revious in uts

– State = memory

-

8/18/2019 Datapath I

8/22

, , , , ,

• Multiplexer

• Decoder• Adder, subtractor, comparator

• Array multipliers

-

8/18/2019 Datapath I

9/22

•

• Registers• Register files

• Memories

-

8/18/2019 Datapath I

10/22

•

– State changes

only

with

clock

edge

– State

changes

can

occur

with

changes

in

other

falling edge

cycle time

rising edge

-

8/18/2019 Datapath I

11/22

Q R Q

C

_

Q S

_

Q

C

Q

-

8/18/2019 Datapath I

12/22

_Q

_Q

D

latchC

D

latchC

C

D

C

-

8/18/2019 Datapath I

13/22

Clock

and

timin sD

Set-up time Hold time

C

Element

2

Element

1

Combinational

Logic

oc yc e

-

8/18/2019 Datapath I

14/22

•

• Adder

• Multiplexer

• eg s er e

• Program memory

• Data memory

• Bit manipulation components

-

8/18/2019 Datapath I

15/22

PC

32 32

clock

-

8/18/2019 Datapath I

16/22

PC+4PC

32

+

32

+

32offset

32

4

3232

-

8/18/2019 Datapath I

17/22

operation

a=b

a overflow

result

b

32

-

8/18/2019 Datapath I

18/22

+

mux

1 32

select

-

8/18/2019 Datapath I

19/22

5Register

Read

Data 1

Read Reg 1

5

Number

Data

Read Reg 2

Registers

Read

Data 2

r e eg

32

Write dataData

32

-

8/18/2019 Datapath I

20/22

MIPS Com onents:

Pro ram

memor

Instruction

Instruction

Instruction

Memory

-

8/18/2019 Datapath I

21/22

Mem

Write

Data

A ress

Read

data

Memory

Write

data

Mem

ea

-

8/18/2019 Datapath I

22/22

MIPS Components

Bit manipu ation

circuits

MSB

sign

xtend

MSB

shift0 LSB