Victor Zhirnov July 10, 2011 San Francisco, CA ERD Memory Discussion.

-

Upload

griselda-stevenson -

Category

Documents

-

view

216 -

download

7

Transcript of Victor Zhirnov July 10, 2011 San Francisco, CA ERD Memory Discussion.

Victor Zhirnov

July 10, 2011

San Francisco, CA

ERD Memory Discussion

Outline

ERD Memory Tables/Text Updates Memory Select Device Section Storage Class Memory Section

2

ERD Memory Tables

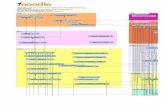

2011 Memory Transition Table

4

IN/OUT (Table ERD5) Reason for IN/OUT Comment

Emerging Ferroelectric Memory IN

Replaces former FeFET category and the

ferroelectric polarization/electronc

effects memory categories

Redox memory IN

Replaces former

nanothermal and Ionic memory categories

Mott Memory INSeparated from the

electronic effects memory

FeFET Memory OUT

Merged with FeFET and the ferroelectric

polarization/electronc effects memory

Electronic effects memory OUT Replaced by EFM and Mott

Nanothermal memory OUTMerged with Ionic Memory to

form Redox Memory Category

Nanoionic memory OUTMerged with Nanothermal

Memory to form Redox Memory Category

Spin Torque Transfer MRAM OUTBecame a prototypical

technology

Spin Torque Tranfer MRAM is already included in PIDS chapter since 2009 (Tables PIDS5 and PIDS 5A)

2011 ERD Memory Table

5

Emerging

Ferroelectric memory

Nanomechanical Memory

Redox Memory

Mott Memory

Macromolecular Memory

Molecular Memories

Storage MechanismRemnant polarization on

a ferroelectric gate dielectric

Electrostatically-controlled mechanical

switch

Ion transport and

Multiple mechanisms

Multiple mechanismsMultiple

mechanisms

redox reaction

Cell Elements 1T or 1T1R 1T1R or 1D1R 1T1R or 1D1R1T1R or 1D1R

1T1R or 1D1R 1T1R or 1D1R

Device Types

FET with FE gate insulator

FTJ

1) nanobridge1) cation migration

M-I-M (nc)-I-MBi-stable

switch2) telescoping CNT2) anion migration

Mott transition

3) Nanoparticle

Emerging Ferroelectric Memory

Combines two subcategories: Ferroelectric FET Ferroelectric tunnel junction

Should not be confused with conventional ferroelectric memory or FeRAM Based on FE capacitor Is currently in PIDS

Temporary working name: Emerging Ferroelectric Memory Suggestions are welcome

6

Emerging Ferroelectric Memory

Text update: completed

Table ERD5 update: Work in progress

References update: Work in progress

7

Nanomechanical Memory

Text update: completed De-emphasized CNT-based nanomechanical memory

(earlier Nantero concept)

Table ERD5 update: Work in progress

References update: Work in progress

8

RedOx Memory

Replaces former nanothermal and Ionic memory categories

New text based on the materials from Barsa Workshop (white papers and presentations)

Numbers in Table ERD5 updated

References update: Work in progress

9

Macromolecular Memory

Text update: Work in progress

Table ERD5 update: Work in progress

References update: Work in progress

10

Molecular Memory

Text update: Work in progress

Table ERD5 update: Work in progress

References update: Work in progress

11

Input Received

12

Table ERD5/Mott Memory

Alex Bratkovski (HP)

Curt Richter (NIST)

Eric Pop (U Illinois)

An Chen (GLOBALFOUNDRIES)

Rainer Waser (U Aachen)

Hiro Akinaga (AIST)

Table ERD5/Redox Memory

Table ERD5/Redox Memory

Text / References

Table ERD4/PCM

Text / References

Memory Select Device

Wei Lu (U Michigan)An Chen (GLOBALFND)Dirk Wouters (IMEC)Kwok Ng (SRC)Victor Zhirnov (SRC)

Memory Select Device TWG:

14

Rainer Waser (U Aachen) Thomas Vogelsang (RAMBUS) Zoran Krivokapic(GLOBALFND) Al Fazio (Intel)Kyu Min (Intel)U-In Chung (Samsung)Matthew Marinella (Sandia Labs)

Wei Lu (U Michigan)An Chen (GLOBALFND)Dirk Wouters (IMEC)Kwok Ng (SRC)Victor Zhirnov (SRC)

The fundamental study team

Memory Select Device: Intro

15

•A memory cell in array can be viewed as being composed of two fundamental components: the ‘Storage node’, and the ‘Select device’ to minimize sneak current through unselected cells.

•Both components impact scaling limits for memory.

•Several advanced concepts of resistance-based memories offer storage node scaling down below 10 nm, and the memory density will be limited by the select device.

•The select device thus represents a serious bottleneck for memory scaling to 10 nm and beyond.

Suggested select device categories

Planar FET select device

17

(8-9)F2

L. Li, K. Lu, B. Rajendran, T. D. Happ, H-L. Lung, C. Lam, and M. Chan, “Driving Device Comparison for Phase-Change Memory”, IEEE Trans. Electron. Dev. 58 (2011) 664-671

Vertical Select Devices

18

Vertical diode

Vertical FET

L. Li, K. Lu, B. Rajendran, T. D. Happ, H-L. Lung, C. Lam, and M. Chan, “Driving Device Comparison for Phase-Change Memory”, IEEE Trans. Electron. Dev. 58 (2011) 664-671

Vertical Select Devices

19

4F2

5.3F2

Vertical diode

Vertical FET

Vertical Transistor Select Devices

20

Technology

Memory Type Array size

Cell size Transistor

Ion Von Ion/Ioff

Infineon (2004)1 170 nm DRAM 1 Mb 8F2 DG FET 50A 1.8V 1010

Samsung (2010)2 80 nm DRAM 50 Mb 4F2 GAA FET

30A 1.2V 1011

Hynix&Innovative Silicon (2010)3

54 nm Z-RAM - - DG FET - 0.5V -

Numonix (2009)4 45 nm PCM 1Gb 5.5F2 BJT 300A

2V -

NTHY&ITRI(2010)4

180 nm ReRAM - 4F2* BJT 100A

1.2V -

A*STAR (2008)5 ** 25 nm(NW dia)

- - - NWGAA FET

25A 1.2V 107

* projected cell size**has potential as a select device (not demonstrated)

Experimental demonstrations of vertical transistors in memory arrays.

Two-terminal selector devices

External 2-terminal structure with non-linear characteristics e.g. switching diode-type behavior for unipolar memory cells for bipolar cells, selectors with two-way switching behavior are

needed, e.g. Zener diode, avalanche diode etc.

Storage element with inherent rectifying/isolation properties

21

I

VOFF

ION

ION1

ON1

ON2

OFF

unipolar bipolar

Benchmark Select Device Parameters

22

Parameter Value Driver

ON Voltage, Vr ~1 V Compatibility with logic; low-power operation

ON current, Ir ~10-6 A Sensing of memory state (fast read)

ON/OFF ratio* >106 Sufficiently low ‘sneak’ currents **

Operating

temperature

85°C

50°C

The top end spec for servers.

NAND spec (the very embodiment of non- volatile

memory for the current state-of-the-art),

*ON/OFF current ratio at ~(1V) supply**Proposed alternative schemes of array biasing could result in relaxed requirements on the select device ON/OFF ratio [5]

Diode-type Select Devices

pn-diode, Schottky diode Heterojunction diode

BARITT diode Zener diode Reverse breakdown Schottky diode

23

Unipolar cell

Bipolar cell

24

Selector type Material System

Von1 Ion1 Von2 Ion2 ON/OFF F REF

Unipolar cellpn-diode Poly-Si (E) 1 20 A

2×104 A/cm2

- - 105 0.3 m van Duuren 2007

Schottky diode

n-ZnO (E) 1 45 A500 A/cm2

- - 105 3 m Huby 2008

Ge NW (E) 1 1 A500 A/cm2

- - 102 0.5 m Wong 2008

a-Si (I) 1 100 nA1000 A/cm2

- - 106 100 nm Lu 2010

p-Si (E) 1 10 A1000 A/cm2

- - 103 1 m Lee 2010

Pt/TiO2 1 6 mA10 A/cm2

- - 109 245 m Hwang 2010

Heterojunction diode

n-ZnO/p-Si 3 25 mA250 A/cm2

- - 103 100m Choi 2010

CuO/InZnO 1 2.5 A1000 A/cm2

- - 103 0.5 m Park 2009

Bipolar cellZener diode (E) Toda 2009

Reverse breakdown

Schottky diode

Cu/n-Si 1 10 A -3 10 A 103 2 m Kozicky 2010

Diode-type Select Devices

Switch-type select devices

Innovative device concepts that exhibit resistive switching behavior. In some of these concepts the device structure/physics of operation

is similar to the structure of the storage node. A modified memory element could act as select device!

a ‘nonvolatile’ switch is required for the storage node, while for select device depending on the approaches non-volatility may not be necessary and can sometimes be detrimental.

Knowledge gained from studying new memory phenomena can be used for select device!

25

Resistive-Switch-type select devices I

Mott-transition switch is based on the Mott Metal-Insulator transition a volatile resistive switch, A VO2-based Mott-transition device has been demonstrated as a selection

device for NiOx RRAM element [Ref: M.J. Lee, “Two Series Oxide Resistors Applicable to High

Speed and High Density Nonvolatile Memory,” Adv. Mater. 19, 3919 (2007).]. The feasibility of the Mott-transition switch as selection devices still needs

further research.

Threshold switch is based the threshold switching in MIM structures caused by electronic

charge injection/trapping Significant resistance reduction can occur at a threshold voltage and this

low-resistance state quickly recovers to the original high-resistance state when the applied voltage falls below a holding voltage.

26

Resistive-Switch-type select devices II

MIEC switch observed in materials that conduct both ions and electronic charges – so

called mixed ionic electronic conduction materials (MIEC). The resistive switching mechanism is similar to the ionic memories.

Complementary resistive switch the memory cell is composed of two identical non-volatile ReRAM

switches connected back-to-back. Example: Pt/GeSe/Cu/GeSe/Pt structure During idle conditions one of the ReRAM switch is off so sneak current is

reduced. Read involves turning on both ReRAM devices and is destructive.

27

Mott-Switch as Select Device

- demonstrated very fast writing and erasing process, 1.5V; 10ns. - read operation at 0.6V also doesn’t seem to be degraded by switch element- on/off ratio ~ 103, Ion ~ 400 A/cm2

Resistive Switching

Threshold Switching

Combined device switching

Lee 2007

Threshold switch as Select DeviceC

urre

nt

Voltage

Schematic I-V characteristics of threshold switch

Schematic I-V characteristics of combined unipolar RRAM devices with threshold switch as the select device

Voltage

Cur

rent

Vread

VSet

VReset

-Similar to Mott switch, but not restricted by the transition temperature- Organic Threshold Switch as select device integrated with PCM (Kau 2009)- 9ns switching speed and 106 endurance demonstrated- Array data not available. Arrays based on MOS select devices presented

- MIEC switching due to redistribution of Cu ions and associated hole diff. current

- Current scales with BEC area. Needs very thin (~ 13nm) dielectric for high current

- Combined MIEC/PCM device demonstrated with endurance of > 3x104 cycles.

Switch device characteristics

MIEC-Switch as Select Device

Gopalakrishnan 2010

Complementary ReRAM cell

Waser 2010 (1,0)

(1,1)

(0,1)(0,1)

(1,1)

(1,0)C-ReRAM 0 = (0,1)C-ReRAM 1 = (1,0)

Vread

Two identical RRAM devices connected back-to-back

(1,0) -> (1,1), -> high read current(0,1) -> (0,1), -> low read current

Vc,reset

Vc,set

VT,set<Vread<2VT,reset

Complementary ReRAM cell

Lee 2010

CRRAM cell

Read endurance is limited to 105

C-ReRAM based on back-to-back Pt/ZrOx/HfOx/BE devices

33

Select Device Material System Von1 Ion1

(Jon1)ON/OFF F REF

Mott transition switch

Pt/VO2/Pt 0.4/0.6V

(400 A/cm2) 103 Lee 2007

Threshold switch

Chalcogenide alloy (undisclosed)

106 Kau 2009

MIEC switch ~1 40 nm Gopalakrishnan2010

Complementary resistive switch

Pt/GeSe/Cu/GeSe/Pt 1 600 A 2400 A/cm2

5 m Waser 2010

Resistive-Switch-type select devicesSource: Philip Wong / Stanford

Criteria for the evaluation of selection devicesParameters Explanations

Blocking state resistance

• Measure the resistance from the selection devices in the blocking state; it is generally a voltage-dependent value

• The higher the blocking state resistance the better

Conductive state resistance

• Measure the resistance from the selection devices in the conductive state; it is generally a voltage-dependent value

• The smaller the conductive state resistance the better

Turn-on voltage • The voltage where the selection devices become sufficiently conductive

Turn-on speed • How fast the selection devices turn on, which affect switching dynamics

Turn-off voltage • The voltage where the selection devices become nonconductive (high resistance)

Turn-off speed • How fast the selection devices turn off, which affect switching dynamics

Operation polarity • Blocking/conductive states exist in both polarities (suitable for bipolar switching devices) or each in different polarity (suitable for unipolar switching devices)

Scalability • How scalable is the selection devices

Linearity • Linear or nonlinear I-V characteristics in blocking and conductive states

Processing temperature • Low processing temperature is preferred

Materials • What materials are required? How available are they? Are they compatible with the processing of the resistive switching devices?

Structures • Two terminal or three terminal

Fundamental Issues

For scaled diode-type select devices two fundamental challenges are: Contact resistance Lateral depletion effects Very high concentration of dopants are needed to minimize

both effects. high dopant concentrations result in increase reverse currents

in classical diode structures and therefore in reduced ON/OFF ratio.

For switch-type select devices the main challenges are: identifying the right material and the switching mechanism to achieve the required drive

current density, ON/OFF ratio and reliability.

35

Selection Devices Summary

Experimental two-terminal select devices have yet to meet the benchmark specifications Hence, outstanding research issues persist 2011 MSD tables and text reflects both target parameters

and experimental status

More detailed benchmarking and further analysis is currently underway

Currently no data from functional arrays based on two-terminal select devices are available

36

Solid-State Storage Class Memory

SCM Team:

38

Barry Schechtman (INSIC)Rod Bowman (Seagate)Geoff Burr (IBM)Bob Fontana (IBM)Michele Franceschini (IBM)Rich Freitas (IBM)Kevin Gomez (Seagate)Mark Kryder (CMU)Antoine Khroueir (Seagate)Kroum Stoev (Western Digital)Winfried Wilcke (IBM)

Thomas Vogelsang (RAMBUS)Matthew Marinella (Sandia Labs)Jim Hutchby (SRC)Victor Zhirnov (SRC)

Storage-class memory (SCM)

Research and development efforts are underway worldwide on several nonvolatile memory technologies that not only complement the existing memory but also reduce the distinction between memory and storage1

Memory: fast, evanescent, random-access, expensive Storage: slow, permanent, sequential-access, inexpensive

Storage-class memory (SCM): Emerging solid-state technologies with (some) attributes of both memory and storage devices May eventually replace discs and (perhaps) DRAM1

1 “Storage-class memory: The next storage system technology”, by R. F. Freitas and W. W. Wilcke, IBM J. Res. & Dev. 52 (2008) 439

Draft Section on SCM is Completed

Storage-class memory (SCM) describes a device category that combines the benefits of solid-state memory, such as high performance and robustness, with the archival capabilities and low cost of conventional hard-disk magnetic storage. Such a device requires a nonvolatile memory technology that could

be manufactured at a very low cost per bit.

As the scalability of flash is approaching its limit, emerging technologies for non-volatile memories need to be investigated for a potential “take over” of the scaling roadmap for flash.

In principle, such new SCM technology could engender two entirely new and distinct levels within the memory and storage hierarchy, located below off-chip DRAM and above mechanical storage, and differentiated from each other by access time.

40

Hard-disk Drive

Conventionally, magnetic hard-disk drives are used for nonvolatile data storage.

The cost of HDD storage (in $/GB) is extremely low and continues to decrease.

Issues: poor random access time relatively high energy consumption, large form factor, limited reliability.

41

Flash memory: Device Challenges

NAND flash has recently become an alternative storage technology faster access times, smaller size and potentially lower energy consumption, as compared to

HDD.

The NAND-based solid state drive (SSD) market has flourished recently. There are several serious limitations of NAND flash for storage

applications poor endurance (104 – 105 erase cycles), modest retention (typically 10 years on the new device, but only 1 year at

the end of rated endurance lifetime), long erase time (~ms), and high operation voltage (~15V).

42

Flash SSD: Architectural Challenges

Page/block-based architecture, doesn’t allow for a direct overwrite of data, requiring sophisticated garbage collection bulk erase procedures,

Computation-intensive data management Takes extra memory space, Limits performance Accelerates the wearing out of memory cells. Lower power potential compromised in current SSD

implementations

43

Flash Scaling Challenges

Flash memory scaling doesn’t improve (and sometimes degrades) the basic performance characteristics read, write and erase latencies have been nearly constant for

over a decade Extreme scaling results in the degradation of retention time

and endurance, critical for storage applications!

There are opportunities for prototypical and emerging memory technologies to enter the non-volatile solid state memory space.

44

Prototypical and emerging memory technologies for SCM applications As the scalability of flash is approaching its limit,

emerging technologies for non-volatile memories need to be investigated for a potential “take over” of the scaling roadmap for flash.

It appears that storage applications could be the primary driver for the new memory technologies, may help to overcome the fundamental shortcomings of flash

technology. In principle, such new SCM technology could engender

two entirely new and distinct levels within the memory and storage hierarchy, located below off-chip DRAM and above mechanical storage, which are differentiated from each other by access time.

45

I. S-type storage-class memory

The first new level, identified as S-type storage-class memory (S-SCM), would serve as a high-performance solid-state drive accessed by the system I/O controller much like an HDD. S-SCM would need to provide at least the same data retention as

flash, offering new direct overwrite and random access capabilities

(which can lead to improved performance and simpler systems) However, it would be absolutely critical that the device cost for S-

SCM be no more than 1.5-2x(1-1.5x? IN THE MATURE STATE)) higher than NAND flash

If the cost per bit could be driven low enough through ultrahigh memory density, ultimately such an S-SCM device could potentially replace magnetic hard-disk drives in enterprise storage server systems.

46

II. M-type storage-class memory

M-SCM: should offer a read/write latency of less than 1 s.

would allow it to remain synchronous with a memory system, allowing direct connection from a memory controller and bypassing the inefficiencies of access through the I/O controller.

Would be to augment a small amount of DRAM to provide the same overall system performance as a DRAM-only system, while providing Moderate retention, Lower power-per-GB and lower cost-per-GB than DRAM. Endurance is particularly critical

the time available for wear-leveling, error-correction, and other similar techniques is limited

> 109 cycles

47

Target device and system specifications for SCM

48

Parameter Benchmark TargetHDD* NAND flash** DRAM Memory-type

SCMStorage-type

SCM

Read/Write latency

3-5 ms ~100s(block erase ~1

ms)

<10 ns <0.3s 1-10s

Endurance (cycles)

unlimited 105 unlimited >109 108

Retention >10 years ~10 years 64 ms >5 days ~10 yearsON power (W/GB)

~0.04 ~0.01-0.04 0.4 Lower (per GB) than DRAM

Lower (per GB) than HDD

Standby power ~20% ON power

<10% ON power

~25% ON power

<1% ON power

<1% ON power

Areal density ~ 1011 bit/cm2 ~ 1010 bit/cm2 ~ 109 bit/cm2 >109 bit/cm2 >109 bit/cm2

Cost ($/GB) 0.1 2 10 Lower than DRAM

Within (1.5-2x?) of NAND

Flash* enterprise class**single-level cell (SLC)

Prototypical and emerging memory technologies for SCM applications Necessary attributes of a memory device for the storage-

class memory applications are: Scalability Multilevel Cell - MLC (MLC vs extreme scaling dilemma) 3D integration (stacking) Fabrications costs Endurance (for M-SCM) Retention (for S-SCM)

The driving issue is to minimize the cost per bit

49

Potential of the current prototypical research memory candidates for SCM applications

50

A likely introduction of these new memory devices to the market is by the hybrid solid-state discs, where the new memory technology complements the traditional flash memory to boost the SSD performance.

Experimental implementations of FeRAM/flash and PCRAM/flash have recently been explored. It was shown that the PCRAM/Flash hybrid improves SSD operations by decreasing the energy consumption and increasing the lifetime of flash memory.

Parameter FeRAM STT-MRAM PCRAM

Scalability low medium good

MLC no difficult yes

3D integration

Fabrication cost

Endurance good excellent average

Potential of the current emerging research memory candidates for SCM applications

51

Parameter Ferroelectric memory

Nanomechanical memory

Redox memory

Mott Memory

Macromolecular memory

Molecular Memory

Scalability

MLC

3D integration

Fabrication cost

Endurance

“Traffic Light” indicators

52

Green: this entry has good progress; there are no or few issues. Yellow: this entry’s potential is not clear; there is a number of issues. Red: this entry’s potential is questionable; there is a list of issues.

Message might be softer, a bit more proactively positive (or at least hopeful).

Proposal from Toshiba

Table 1 (current version)

54

Parameter Benchmark TargetHDD* NAND flash** DRAM Memory-type

SCMStorage-type

SCM

Read/Write latency

3-5 ms ~100s(block erase ~1

ms)

<10 ns <0.3s 1-10s

Endurance (cycles)

unlimited 105 unlimited >109 108

Retention >10 years ~10 years 64 ms >5 days ~10 yearsON power (W/GB)

~0.04 ~0.01-0.04 0.4 Lower (per GB) than DRAM

Lower (per GB) than HDD

Standby power ~20% ON power

<10% ON power

~25% ON power

<1% ON power

<1% ON power

Areal density ~ 1011 bit/cm2 ~ 1010 bit/cm2 ~ 109 bit/cm2 >109 bit/cm2 >1010 bit/cm2

Cost ($/GB) 0.1 2 10 Lower than DRAM

Within (1.5-2x?) of NAND

Flash* enterprise class**single-level cell (SLC)

Target Benchmark(DRAM)

STT-MRAM

Target Benchmark

(HDD*)

Benchmark(NANDFlash)

30ns ~100s(block erase

~1 ms)Endurance

(cycles)>109 unlimited 1015 108 unlimited 104-105

Retention >5 days 64 ms 20 years ~10 years >10 years ~10 yearsON power(W/GB)

Lower (perGB) thanDRAM

0.4 0.01 Lower (perGB) than

HDD

~0.04 ~0.01-0.04

Standbypower

<1% ONpower

~25% ONpower

<1% ONpower

<1% ONpower

~20% ONpower

<10% ONpower

Arealdensity

~ 109 bit/cm2 ~ 108 bit/cm2 >109 bit/cm2 ~ 1011

bit/cm2

~ 1010

bit/cm2

Cost ($/GB) Lower thanDRAM

10 50,000 Within 2-3xof NAND

Flash

0.1 2

Parameter Memory-type SCM

Read/Writelatency

<0.3s 1-10s 3-5 ms

Storage-type SCM

<10 ns

Table 1 (proposed)

<10 ns

~109 bit/cm2

>106

Other proposals

How about to mention about emerging NVM technologies? Such as FusionIO, NVM express, and so on.

How about to merge Table 2 and 3?

Architectural Implications Advances in SCM could drive the emerging data-centric chip

architectures Nanostores

Nanostores architectures could be an important direction for the future of information processing.

Addressed in the ERA section

57

Computer, Jan. 2011

Input Received

58

Atsuhiro Kinoshita (Toshiba)Dirk Wouters (IMEC)Rainer Waser (U Aachen) Thomas Vogelsang (RAMBUS) Matthew Marinella (Sandia Labs)Geoff Burr (IBM)Bob Fontana (IBM)Kevin Gomez (Seagate)Mark Kryder (CMU)Paul Frank (INSIC)