Verilog l03 Mit

-

Upload

nishant-jain -

Category

Documents

-

view

284 -

download

2

Transcript of Verilog l03 Mit

6.111 Fall 2007 Lecture 3, Slide 1

Fortunately, we can get by with a few basic gates…

How many different gates do we really need?

AB Y

00 0

01 1

10 0

11 0

B>A

AB

y

AB Y

00 0

01 1

10 1

11 0

XORAB

Y

AND, OR, and NOT are sufficient… (cf Boolean Expressions):

AB

yAB=A+B

That is justDeMorgan’sTheorem!

AB=A+B

A+B = AB

AB Y

6.111 Fall 2007 Lecture 3, Slide 2

One will do!

NANDs and NORs are universal:

Ah!, but what if we want more than 2 inputs?

==

=

==

=

6.111 Fall 2007 Lecture 3, Slide 3

I think that I shall never seea circuit lovely as...

A1

A2

A4

A3

AN

N-input TREE has O( ______ ) levels...

Signal propagation takes O( _______ ) gate delays.

Question: Can EVERY N-Input Boolean function beimplemented as a tree of 2-input gates?

log N

log N

21222log2N

6.111 Fall 2007 Lecture 3, Slide 4

Here’s a Design Approach1) Write out our functional spec as

a truth table2) Write down a Boolean expression

for every ‘1’ in the output

3) Wire up the gates, call it a day,and declare success!

This approach will always give usBoolean expressions in aparticular form:

SUM-OF-PRODUCTS

C B A Y

0 0 0 0

0 0 1 1

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 0

1 1 0 1

1 1 1 1

Truth Table

-it’s systematic!-it works!-it’s easy!-are we done yet???

CBAACBBACABCY +++=

6.111 Fall 2007 Lecture 3, Slide 5

Straightforward SynthesisWe can implement

SUM-OF-PRODUCTSwith just three levels oflogic.

INVERTERS/AND/OR

Propagation delay --No more than “3” gate delays

(well, it’s actually O(log N) gate delays)

ABCABCABCABC

Y

6.111 Fall 2007 Lecture 3, Slide 6

AB=A+B

Practical SOP Implementation• NAND-NAND

• NOR-NOR

C

A

BY

C

A

BY

≡C

A

BY

zyxxyz ++=

≡C

A

BY

yxyx =+

C

A

BY

C

A

BY

AB=A+B “Pushing Bubbles”

You might think all these extrainverters would make this structureless a!ractive. However, quite theopposite is true.

6.111 Fall 2007 Lecture 3, Slide 7

Logic SimplificationCan we implement the same function with fewer gates? Before

trying we’ll add a few more tricks in our bag.BOOLEAN ALGEBRA:

OR rules: a + 1 = 1, a + 0 = a, a + a = aAND rules: a1 = a, aO = 0, aa = aCommutative: a + b = b + a, ab = baAssociative: (a + b) + c = a + (b + c), (ab)c = a(bc)Distributive: a(b+c) = ab + ac, a + bc = (a+b)(a+c)Complements:Absorption:

Reduction:DeMorgan’s Law:

0,1 ==+ aaaa

babaaaaba +=+=+ ,

abbaaabaa =+=+ )(,)(

bbababbaab =++=+ ))((,

babaabba +==+ ,

6.111 Fall 2007 Lecture 3, Slide 8

Boolean Minimization:An Algebraic Approach

BACCBAACBABCY +++=

Lets (again!) simplify

Using the identity

!!! =+ AA

BACCBAACBABCY +++=

CBACY +=

BACCBABCY ++=

Can’t he come upwith a new example???

For any expression α and variable A:Hey, I could writeA program to do

That!

6.111 Fall 2007 Lecture 3, Slide 9

Karnaugh Maps: A Geometric Approach

It’s cyclic. The left edge is adjacent to the rightedge. (It’s really just a flattened out cube).

C\AB 00 01 11 10

0 0 0 1 1

1 0 1 1 0

000 001

010 011

100 101

110 111

Here’s the layout of a 3-variable K-map filledin with the values from our truth table:

K-Map: a truth table arranged so that terms which differ byexactly one variable are adjacent to one another so we can see

potential reductions easily.

C A B Y

0 0 0 0

0 0 1 0

0 1 0 1

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 0

1 1 1 1

Truth Table

Why did heshade thatrow Gray?

6.111 Fall 2007 Lecture 3, Slide 10

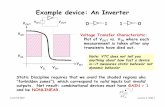

On to Hyperspace4-variable K-map for a multipurpose logic gate:

Again it’s cyclic. The left edge is adjacent to the right edge,and the top is adjacent to the bottom.

\AB

CD\ 00 01 11 10

00 0 0 1 0

01 0 1 1 1

11 0 1 0 1

10 1 0 0 1

=⊕

=

=+

=⋅

=

11

10

01

00

CDifBA

CDifB

CDifBA

CDifBA

Y

6.111 Fall 2007 Lecture 3, Slide 11

Finding SubcubesWe can identify clusters of “irrelevent” variables by circling

adjacent subcubes of 1s. A subcube is just a lowerdimensional cube.

The best strategy is generally a greedy one.- Circle the largest N-dimensional subcube (2N adjacent 1’s)

4x4, 4x2, 4x1, 2x2, 2x1, 1x1- Continue circling the largest remaining subcubes (even if they overlap previous ones)

- Circle smaller and smaller subcubes until no 1s are left.

\AB

CD\ 00 01 11 10

00 0 0 1 0

01 0 1 1 1

11 0 1 0 1

10 1 0 0 1

C\AB 00 01 11 10

0 0 0 1 1

1 0 1 1 0

6.111 Fall 2007 Lecture 3, Slide 12

Write Down EquationsWrite down a product term for the portion of eachcluster/subcube that is invariant. You only need to includeenough terms so that all the 1’s are covered. Result: a minimalsum of products expression for the truth table.

C\AB 00 01 11 10

0 0 0 1 1

1 0 1 1 0

Y = CA + CB

\AB

CD\ 00 01 11 10

00 0 0 1 0

01 0 1 1 1

11 0 1 0 1

10 1 0 0 1

Y = ABC + ABD + ABD + BCD

We’re done!

6.111 Fall 2007 Lecture 3, Slide 13

Recap: K-map Minimization1) Copy truth table into K-Map2) Identify subcubes,

selecting the largest available subcube at each step, even ifit involves some overlap with previous cubes, until all onesare covered. (Try: 4x4, 2x4 and 4x2, 1x4 and 4x1, 2x2, 2x1 and1x2, finally 1x1)

3) Write down the minimal SOP realization

C\BA 00 01 11 10

0 0 1 1 0

1 0 0 1 1

C B A Y

0 0 0 0

0 0 1 1

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 0

1 1 0 1

1 1 1 1

Truth Table

CBACY +=

JARGON: The circled terms are called implicants. Animplicant not completely contained in anotherimplicant is called a prime implicant.

6.111 Fall 2007 Lecture 3, Slide 14

Logic that defies SOP simplification

Ci00001111

A00110011

B01010101

S01101001

Co00010111

S = ABC + ABC + ABC + ABC

Co = ABC + ABC + ABC + ABC

FA

A B

Co Ci

S

Can simplify the carry out easily enough, eg...

Co = BC + AB + AC

But, the sum, S, doesn’t have a simple sum-of-productsimplementation even though it can be implemented using onlytwo 2-input XOR gates.

Full Adder

C/AB 00 01 11 10

0 0 0 1 0

1 0 1 1 1

C/AB 00 01 11 10

0 0 1 0 1

1 1 0 1 0

S

CO

6.111 Fall 2007 Lecture 3, Slide 15

Logic Synthesis Using MUXes

A

BY

C

If C is 1 thencopy B to Y,

otherwise copyA to Y

2-input Multiplexer

BCA

Y

A

B

C

0

1

schematic Gatesymbol

C B A Y

0 0 0 0

0 0 1 1

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 0

1 1 0 1

1 1 1 1

Truth Table

0101S

0101S

0101S

I0I1

I2I3

Y

S0 S1

A 4-input Muximplemented as

a tree

6.111 Fall 2007 Lecture 3, Slide 16

Systematic Implementation ofCombinational Logic

Consider implementation of somearbitrary Boolean function, F(A,B)

... using a MULTIPLEXERas the only circuit element:

A B Cin Cout

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

Full-AdderCarry Out Logic

01234567

A,B,Cin

Cout

00010111

6.111 Fall 2007 Lecture 3, Slide 17

Systematic Implementation ofCombinational Logic

Same function as on previous slide, butthis time let’s use a 4-input mux

A B Cin Cout

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

Full-AdderCarry Out Logic

0123

A,B

Cout

0CC1

6.111 Fall 2007 Lecture 3, Slide 18

General Table Lookup Synthesis

MUXLogic

A B

Fn(A,B)

Generalizing: In theory, we can build any 1-output combinational logic block with multiplexers.

For an N-input function we need a _____ input mux.

BIG Multiplexers? How about 10-input function? 20-input?

AB Fn(A,B)

00 0

01 1

10 1

11 0

2N

Muxes are UNIVERSAL!

In future technologiesmuxes might be the

“natural gate”.

0101S

10

A

Y A Y=

0101S

0B

A

Y

0101S

B1

A

Y

=

=

AB

Y

AB

Y

0101S

BB

A

YWhat doesthat one do?

6.111 Fall 2007 Lecture 3, Slide 19

A Mux’s Guts

Hmmm, by sharing the decoder part of the logic MUXscould be adapted to make lookup tables with any numberof outputs

I00

I01

I10

I11

ABABABAB

Y

Decoder Selector Multiplexerscan be constructedinto two sections:

A DECODER thatidentifies the

desired input,and

a SELECTOR thatenables that inputonto the output.

A decodergeneratesall possibleproduct

terms fora set ofinputs

0

1

2

3

6.111 Fall 2007 Lecture 3, Slide 20

Using Memory as a Programmable Logic Device

Row

Add

ress

Dec

oder

Col.1

Col.2

Col.3

Col.2M

Row 1

Row 2

Row 2N

Column MultiplexerM

N

M+N INPUTS bit lines word lines

memorycell

(one bit)

F(INPUTS)

6.111 Fall 2007 Lecture 3, Slide 21

Xilinx Virtex II FPGA

XC2V6000:• 957 pins, 684 IOBs• CLB array: 88 cols x 96/col = 8448 CLBs• 18Kbit BRAMs = 6 cols x 24/col = 144 BRAMs = 2.5Mbits• 18x18 multipliers = 6 cols x 24/col = 144 multipliers

Figures from Xilinx Virtex II datasheet

6.111 Fall 2007 Lecture 3, Slide 22

Virtex II CLB

Figures from Xilinx Virtex II datasheet

16 bits of RAM which can be configured as a16x1 single- or dual-port RAM, a 16-bit shiftregister, or a 16-location lookup table

6.111 Fall 2007 Lecture 3, Slide 23

Virtex II Slice Schematic

Figures from Xilinx Virtex II datasheet