TSV integration into silicon photonics interposer for next ...

Transcript of TSV integration into silicon photonics interposer for next ...

© MASSTART

MASSTART Consortium

Data Center Interconnects - Towards Mass Manufacturing, 6th October 2020

TSV integration into silicon photonics interposer for next generation transceiver PICs

Bogdan SIRBUFraunhofer IZM, Germany

www.masstart.eu

virtual conference session:Data Center Interconnects – Towards Mass Manufacturing

online / October 6th 2020 / 4 – 7pm

© Fraunhofer

TSV integration into silicon photonics interposer for next generation transceiver PICs

Bogdan Sirbu , Kai Zoschke

Fraunhofer Institute for Reliability and Microintegration (IZM), Berlin

Photonics days Berlin Brandenburg 2020

© Fraunhofer IZM

Bogdan Sirbu, WLSI

2 Photonics Days Berlin Brandenburg, 06.10.2020 www.masstart.eu

Data Age - Global datasphere by 2025

25%Amount of created real-time data in datasphere

1 zettabyte : 1021 bytes

163ZBAmount of datathat will be createdannually

20%Amount of life-critical data in datasphere

4800/dayAmount of one persons interaction with IoT devices

90%Amount of data in datasphere require security

5.2ZBAmount of data that subject to data analysis

1.4ZBAmount of analysed data touched by AI / cognitive systems

Source: IDC, Seagate

© Fraunhofer IZM

Bogdan Sirbu, WLSI

3 Photonics Days Berlin Brandenburg, 06.10.2020 www.masstart.eu

Source: Total consumer power consumption forecast, Dr. Anders S. G. Andrae (Huawei), Nordic Digital Business Summit, October 2017

The Downside

© Fraunhofer IZM

Bogdan Sirbu, WLSI

4 Photonics Days Berlin Brandenburg, 06.10.2020 www.masstart.eu

Motivation – Data center traffic growthForecast 2014:

Within data center 73.1%

Data center to user 18.2%

Data center to data center 8.7%

Source: Cisco Global Cloud Index 2014Forecast 2018:

Within data center 73.4%

Data center to user 14.3%

Data center to data center 12.4%

Source: Cisco Global Cloud Index 2016-2021 (2018)

CAGR: 25%

CAGR: 24.7%

© Fraunhofer IZM

Bogdan Sirbu, WLSI

5 Photonics Days Berlin Brandenburg, 06.10.2020 www.masstart.eu

Silicon Photonics Chip Forecast for DCI

Source: Yole

© Fraunhofer IZM

Bogdan Sirbu, WLSI

6 Photonics Days Berlin Brandenburg, 06.10.2020 www.masstart.eu

Photonics Packaging Key Challenges

High precision placement for fiber alignment for SM

Delicate parts handling

Different die attach technologies for assembly

Testing

Standardization

Reliability

Small and odd shape devices

High cost

© Fraunhofer IZM

Bogdan Sirbu, WLSI

7 Photonics Days Berlin Brandenburg, 06.10.2020 www.masstart.eu

Ethernet speed – Historical Data and Forecast

100G proliferating

400G ramp up after 2021

Next stop, 800G and 1.6T

Road >400G includes COBO and co-packaging

© Fraunhofer IZM

Bogdan Sirbu, WLSI

8 Photonics Days Berlin Brandenburg, 06.10.2020 www.masstart.eu

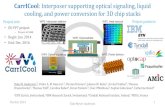

MASSTART surpasses the cost metric threshold by using enhanced and scalable techniques

Glass interface based laser/PIC and fiber/PIC coupling approaches, leveraging glass waveguide technology to obtain spot size and pitch converters in order to dramatically increase optical I/O density, while facilitating automated assembly processes,

3D packaging (TSV) enabling backside connection of the high speed PIC to a Si carrier,

A new generation of flip chip bonders with enhanced placement in a complete assembly line compatible with Industry 4.0 which will guarantee an x6 improvement in throughput

Wafer-level evaluation of assembled circuits with novel tools that will reduce the characterization time by a factor of 10, down to 1 minute per device.

4-channel PSM4 module in QSFP-DD format with 400G aggregate bit rate,

8-channel WDM module in a QSFP-DD format with 800G aggregate bit rate,

16-channel WDM on-board module delivering 1.6Tb/s aggregate line rate,

A tunable single-wavelength coherent transceiver with 600Gb/s capacity following the DP-64QAM modulation format on 64Gbaud/s line rate.

© Fraunhofer IZM

Bogdan Sirbu, WLSI

9 Photonics Days Berlin Brandenburg, 06.10.2020 www.masstart.eu

MASSTART – Consortium as a whole

System providers

Photonic Assembly & Testing

Design House & Technology consultancy

Technology providers

© Fraunhofer IZM

Bogdan Sirbu, WLSI

10 Photonics Days Berlin Brandenburg, 06.10.2020 www.masstart.eu

MASSTART Coherent Transceiver Packaging

Glass interface based laser/PIC and fiber/PIC coupling approaches

obtain spot size and pitch converters

increase optical I/O density, automated assembly processes

3D packaging using TSV enabling backside connection of the high speed PIC to a Si carrier

New flip chip bonders with enhanced placement

improvement in throughput

Wafer-level evaluation of assembled circuits with novel tools

reduce characterization time

© Fraunhofer IZM

Bogdan Sirbu, WLSI

11 Photonics Days Berlin Brandenburg, 06.10.2020 www.masstart.eu

TSV Test-structures GSG

© Fraunhofer IZM

Bogdan Sirbu, WLSI

12 Photonics Days Berlin Brandenburg, 06.10.2020 www.masstart.eu

GSGSG TSV Application ScenarioRequired to connect:

Driver/TIA chips assembled on top of the Interposer

DSP chip assembled on the PCB

PCB

Si Interposer

TIA/DRV

DSP

© Fraunhofer IZM

Bogdan Sirbu, WLSI

13 Photonics Days Berlin Brandenburg, 06.10.2020 www.masstart.eu

TSV Integration Schemes

Back Side Via last

• TSV integration after completewafer processing

• TSV through thick BEOL oxide• Requires keep out zones in FEOL

and BEOL for TSV integration

Via first or middle; Via last;

• TSV integration before FEOL orafter FEOL / before BEOL

• Processes established at IDMs

• Support wafer bonding• Wafer backside thinning• TSV reveal• Backside RDL and bump

formation• Support wafer de-bonding

• TSV integration after completewafer processing

• Requires landing pads in BEOL for prepared TSV connection

• Support wafer bonding• Wafer backside thinning• TSV formation with acess to

landing pads• Metall liner and back side RDL

formation• Support wafer de-bonding (if

required)

© Fraunhofer IZM

Bogdan Sirbu, WLSI

14 Photonics Days Berlin Brandenburg, 06.10.2020 www.masstart.eu

Front and Back Side Processes for TSV, RDL and IO formation

© Fraunhofer IZM

Bogdan Sirbu, WLSI

15 Photonics Days Berlin Brandenburg, 06.10.2020 www.masstart.eu

Layers and Test Structures for TSV Characterization

Frontside:

#61 – top metal on LETI Wafer(line 20µm, pad Ø30µm)

#10 – TSV(Ø20µm)

#11 – FS-RDL metal(line 20µm, pad Ø40µm)

Backside:

#09 – BS TSV-passopen(via Ø10µm)

#21 – BS-RDL metal(line 20µm, pad Ø30µm)

3 test fields for reserved areas at LETI TRX8 waferRF test

structures

4 point probe structures for via isolation and resistance

daisy chains front to back side and between last metallayer and RDL layers

© Fraunhofer IZM

Bogdan Sirbu, WLSI

16 Photonics Days Berlin Brandenburg, 06.10.2020 www.masstart.eu

Wafer after TSV blind hole etching

• Lithography and Alignment established

• BEOL etching established

• SI-DRIE etching established

• CVD / PVD / Cu-Plating to be done

© MASSTART

MASSTART Consortium

Data Center Interconnects - Towards Mass Manufacturing, 6th October 2020

Acknowledgement

Co-funded by the Horizon 2020Framework Programme of the European Union

MASSTART project is co-funded by the Horizon 2020 Framework Programme of the European Union with Grant Agreement Nr. 825109. https://cordis.europa.eu/project/rcn/219912/factsheet/enMASSTART project is an initiative of the Photonics Public Private Partnership www.photonics21.org#Photonics@Photonics21@PhotonicsEU#H2020

www.masstart.eu

#MASSTART

Disclaimer: The information, documentation and figures available in this deliverable are written by the MASSTART Consortium Partners under co-funding by Horizon 2020 Framework Programme of the European Union (Grant agreement ID: 825109) and do not necessarily reflect the view of the European Commission. The information in this document is provided “as is”, and no guarantee or warranty is given that the information is fit for any particular purpose. The reader uses the information at his/her sole risk and liability.

Copyright © 2020 the MASSTART Consortium. All rights reserved. This document may not be copied, reproduced or modified in whole or in part for any purpose without written permission from the MASSTART Consortium. In addition to such written permission to copy, reproduce or modify this document in whole or part, an acknowledgement of the authors of the document and all applicable portions of the copyright notice must be clearly referenced.