Transistor MOSFET y tecnología CMOS€¦ · 7udqvlvwru 026)(7 026)(7v %dvdgr hq ho sulqflslr gh...

Transcript of Transistor MOSFET y tecnología CMOS€¦ · 7udqvlvwru 026)(7 026)(7v %dvdgr hq ho sulqflslr gh...

Elementos ActivosEl Transistor MOSFET

Instituto Tecnológico de Costa Rica

Elementos Activos

Dr.-Ing. Juan José Montero Rodríguez

Semestre II-2019

Escuela de Ingeniería ElectrónicaSemestre II-2019

Tabla de Contenidos

Tema 5. El transistor de efecto de campo MOSFET y la tecnología CMOS

Clase 19: Condensador MOS 3-

Clase 20: Construcción, símbolo, clasificación

Clase 21: Funcionamiento

Clase 22: Curvas características

Clase 23: Polarización I

Clase 24: Polarización II

Clase 25: Modelo analógico

Clase 26: Aplicaciones analógicas

Clase 27: Modelo digital

Clase 28: Aplicaciones digitales

Clase 29: Modelo de alta frecuencia

Clase 30: Fabricación

Clase 31: Escalamiento

Clase 32: Introducción al diseño de CIs

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 2

Objetivos

El transistor de efecto de campo MOSFET y la tecnología CMOS

Construcción, símbolo, clasificación.

Funcionamiento.

Curvas características y polarización.

Modelo del MOSFET para aplicaciones analógicas.

Modelo del MOSFET para aplicaciones digitales.

Capacitancias internas y modelos de alta frecuencia.

Aplicaciones: El FET como interruptor: interruptor serie, paralelo, inversor lógico y compuertas lógicas básicas

Escalamiento de MOSFETs

Objetivo

Conocer el comportamiento y modelado del transistor de efecto de campo MOSFET, así como sus principales aplicaciones.

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 3

Clase 19Construcción, Símbolo, Clasificación

Instituto Tecnológico de Costa Rica

Elementos Activos

Dr.-Ing. Juan José Montero Rodríguez

Semestre II-2019

Escuela de Ingeniería ElectrónicaSemestre II-2019

Transistor MOSFET

MOSFETsBasado en el principio de efecto de campo

Uso de un campo eléctrico para controlar corriente entre dos terminales

Transistor más utilizado (más de 80% del mercado)Base de la industria microelectrónica

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 5

MOSFET

Field Effect

Metal Oxide Semiconductor

Transistor

Transistor

Transfer Resistor

Transistor: dispositivo de al menos tres terminales, en el que una terminal controla el flujo de corriente entre las otras dos

Transistor MOSFET

Principio de efecto de campo presentado en 1925 por Julius Lillienfeld

MOSFET

Patente presentada en 1928 por Lillienfeld

Implementación posible en los 60s

Teoría de escalamiento = miniaturización

60s, Robert Dennard

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 6

1988 / 1.0 m 1991 / 0.8 m1986 / 1.5 m

1993 / 0.6 m 1996 / 0.4 m 1998 / 0.25 m 2000 / 0.18 m

Transistor MOSFET

Dispositivo de 4 terminales: compuerta, fuente, drenador y substrato

Dispositivo UNIPOLAR corriente de conducción involucra prácticamente sólo un tipo de portador de carga

MOSFET consiste en

dos regiones semiconductoras fuertemente dopadas separadas por una región semiconductora de tipo complementario

un aislante y un electrodo sobre dicha región

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 7

Substrato

Polisilicio

Drenador Compuerta Fuente

SiO2

Dióxido de silicio

Polisilicio +

Substrato (Si dopado)

Difusión (Si de dopado complementario al substrato)

Transistor MOSFET

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 8

Z (ancho de canal)

Y (largo de canal)

X (profundidad de canal)

Dióxido de silicio

Polisilicio +

Substrato (Si dopado)

Difusión (Si de dopado complementario al substrato)

Ancho del canal (W)

Largo del canal (L)

Substrato

Drenador Fuente

Compuerta

Espesor del óxido tox

Principio de Funcionamiento del MOSFET

La corriente de arrastre que fluye entre fuente y drenador se controla variando el voltaje en el electrodo de compuerta

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 9

Substrato (B)

Polisilicio

Drenador (D) Compuerta (G) Fuente (S)

SiO2

Controla la resistencia entre fuente y drenador

Compuerta aislada de la superficie del silicio por SiO2

E al semiconductor aplicando voltaje de

compuerta

Polarización y Regiones de Operación

Desde el punto de vista del potencial de superficie/ VGS

Banda plana

Acumulación

Agotamiento

Inversión

Inversión débil

Inversión fuerte

Desde el punto de vista de VDS en comparación con VGS

Región de corte

0

Determinado por VGS

Región lineal

Región de saturación

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 10

0

0

0

Sistema Metal Oxido Semiconductor

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 11

El comportamiento del MOSFET se define con base en el POTENCIAL DE SUPERFICIE S, que mide la deformación de bandas del semiconductor en la interfaz con el óxido

0.95 eV

Metal SiO2 Semiconductor

8..9 eV

EF

EV

EV

EC

Ei

EC

S

Acumulación

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 12

Acumulación: S < 0

- huecos se acumulan en la superficie

Sin canal MOSFET = Dos diodos en serie en direcciones opuestas IDS

EF

EFEV

EC

EiB

S

E V

Substrato

Drenador

n+ n+

Compuerta Fuente

p

+-

++

++ + + +-

S : potencial en la interfaz Si-SiO2, potencial de superficie, medido con respecto a B

B: potencial en el semiconductor en zona lejana a la interfaz Si-SiO2, diferencia entre Ei y EF

Banda Plana

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 13

S : potencial en la interfaz Si-SiO2, potencial de superficie, medido con respecto a B

-VFB voltaje necesario para compensar la diferencia de función de trabajo del metal y el semiconductor

B: potencial en el semiconductor en zona lejana a la interfaz Si-SiO2, diferencia entre Ei y EF

Banda plana:

EF EF

EV

EC

Ei

B

Agotamiento

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 14

Fuente -

Substrato

Drenador

n+ n+

Compuerta

p

+

++

+

++

+

+

-

Agotamiento: 0< S < B

VTH = voltaje de umbral (VGS para activar MOSFET)

EF

EFEV

EC

Ei

-huecos repelidos de la superficie = empobrecimiento de huecos en la superficie-Transistor aún inactivo = región de subumbral

S

E V

Inversión

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 15

Inversión débil: B < S < 2 B Inversión fuerte: S 2 B

-electrones atraídos a la superficie = concentración de electrones en la superficie iguala concentración de huecos en el substrato

superficie de substrato p se comporta como material n

-existe un canal entre drenador y fuente, transistor activo

EF

EFEV

EC

Ei

EF sobre Ei =en la superficie

es de tipo N

S

E V

Zona de agotamientoSubstrato

Drenador

n+

Compuerta Fuente

p

+

n+ -- - - - ---

canal

Transistores NMOS y PMOS

Flujo de corriente: de drenador a fuente

Drenador es región n+ conectada al potencial más alto

Se forma canal tipo N entre drenador y fuente

Flujo de corriente debido a electrones

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 18

Desde el punto de vista de fabricación, la fuente y el drenador son intercambiables. Sólo pueden distinguirse después de polarizarlos

Flujo de corriente: de fuente a drenador

Drenador es región p+ conectada al potencial más bajo

Se forma canal tipo P entre drenador y fuente

Flujo de corriente debido a huecos

Substrato

Polisilicio N+

Drenador

n+ n+

Compuerta Fuente

P

-+

I

Substrato

Polisilicio P+

Drenador

p+ p+

Compuerta Fuente

N

+-

I

Simbología del MOSFET

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 19

Símbolos de tres terminales: substrato conectado a fuente, flecha indica dirección de corriente técnica

Si no se usan flechas, un círculo sin rellenar se añade a la compuerta de los transistores PMOS

MOSFETs de enriquecimiento (normalmente apagado)

MOSFETs de empobrecimiento (normalmente encendido)

NMOS PMOS NMOS PMOS

Simbología del MOSFET

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 20

PMOS:

Substrato N,

canal P

NMOS PMOS

Símbolos de cuatro terminales: flecha en substrato apunta de P a N

MOSFETs de enriquecimiento (normalmente apagado)

MOSFETs de empobrecimiento (normalmente encendido)

NMOS:

Substrato P,

canal N

Empobrecimiento y Enriquecimiento

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 21

IDS

VGSVTH0

0

IDS

VTH VGS

IDS

VGS

0VTH

IDS

VGS

0VTH

Enriquecimiento:normalmente inactivo

NMOS

PMOS

Empobrecimiento:normalmente activo

Clase 20Funcionamiento del Transistor MOSFET

Instituto Tecnológico de Costa Rica

Elementos Activos

Dr.-Ing. Juan José Montero Rodríguez

Semestre II-2019

Escuela de Ingeniería ElectrónicaSemestre II-2019

Voltaje de Umbral

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 23

Voltaje VGS necesario para causar inversión de la superficie

VTH tiene 4 componentes

Compensación de cargas parásitas en SiO2 y la interfaz óxido-semiconductor

Diferencia de función de trabajo entre

compuerta y canal

Voltaje necesario para cambiar el potencial

superficial

Caída de tensión en la zona de carga

espacial

xd: ancho de zona de agotamiento

Ecuaciones Características (región de subumbral)

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 24

Cdep: capacitancia de agotamiento de substrato, Cox: capacitancia de compuerta

O bien, con la pendiente de subumbral S,

Cambio en VGS necesario para una variación de una década en IDS

Valor ideal: 60 mV/dec

W: ancho de transistor

L: longitud de canal

VTH : voltaje de umbral

Vt: voltaje térmico

En la región de corte (subumbral), VGS < VTH. Idealmente, la corriente es cero.

En el caso real, la corriente de subumbral se calcula como

Corriente de Subumbral

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 25

0.5 1 1.5

10-15

10-12

10-9

10-6

10-3

IDS

VGS

S-1

Mayor pendiente IDS vs VGS

S , mejor comportamiento de apagadoy menor corriente de fuga

A T=300K, S=80..85 mV/dec; a T = 100 ºC, S=100mV/dec

Sub-threshold ConductionPendiente de Subumbral

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 26

Ecuaciones Características (región lineal)

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 27

Corriente de drenador en la región lineal: VGS VTH, VGS-VTH > VDS

K: parámetro de transconductancia K`= transconductancia del proceso

: movilidad

OX: permitividad del SiO2 = 3.9 0

tOX: espesor de óxido

Región lineal

B

D G S

p

-+

-- - - - ---n+ n+

Ecuaciones Características (región de saturación)

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 28

Corriente de drenador en la región de saturación: VGS VTH, VGS-VTH VDS

Modulación de largo de canal

Modulación de longitud de canal:

: coeficiente de modulación de canal [V-1]B

D GS

p

-+

- -- --n+ n+

Estrangulamiento del canal a partir de VDS VDS,SAT = VGS VTH

El canal se acorta La corriente en saturación no es constante para un VGS dado, sino depende también de VDS

Curvas Características del MOSFET

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 29

Curva característica de salida

En la región lineal el transistor opera como

una resistencia controlada por voltaje

Modulación de longitud de canal

VDS = VGS-VTH

Curvas Características del MOSFET

22 )(2

)(2

'THGSTHGSD VV

KVV

L

WKI

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 30

Curva de transferencia

VTH

Función de transferencia:

Salida = f(Entrada)

Salida : ID

Entrada : VGS

Regiones de Operación

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 31

Saturación

Lineal

Subumbral

VGSVTH

VGS VTH, VGS-VTH > VDSVGS < VTH

VGS VTH, VGS-VTH VDSVDS

CorteVDS = VGS-VTH

Polarización del Substrato

Diodos parásitos difusión-substrato deben estar polarizados en inversa

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 32

Substrato

Drenador Compuerta Fuente

P

n+ n+

Substrato

Drenador Compuerta Fuente

N

p+ p+

NMOS: Substrato debe conectarse al voltaje más bajo del sistema, por ejemplo a tierra (GND).PMOS: Substrato debe conectarse al voltaje más alto del sistema, por ejemplo, a VDD.También como protección ante el efecto de enganche (latch-up)

Polarización del Substrato

Polarización VBS afecta la tensión de umbral VTH = efecto de substrato (body effect)

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 33

Substrato

Drenador Compuerta Fuente

P

n+ n+

Substrato

Drenador Compuerta Fuente

N

p+ p+

El efecto se conoce también como sensibilidad de substratoEn general, se presenta de manera que aumenta el voltaje de umbralPuede utilizarse para disminuir la corriente de subumbral, por ejemplo, en memorias DRAM

Voltaje de Umbral con Efecto de Substrato

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 36

VB VS cambia el voltaje de umbral

Se analiza aquí el caso de un NMOS

Voltaje de umbral con VBS=0

Coeficiente de efecto de substrato

Por el cambio en la carga en la zona de carga espacial debido a VBS 0

Efecto de Substrato

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 37

VBS2 < VBS1< 0

VBS=0 VBS1 VBS2

VGS

ID

0

Un voltaje de substrato negativo con respecto al surtidor o bien un voltaje de surtidor positivo con respecto al substrato causan unaumento del voltaje de umbral en un transistor N

VDS VGS-VTH

Clase 21Polarización MOSFET

Instituto Tecnológico de Costa Rica

Elementos Activos

Dr.-Ing. Juan José Montero Rodríguez

Semestre II-2019

Escuela de Ingeniería ElectrónicaSemestre II-2019

Ejemplo

1. Un inversor utiliza un transistor MOS con los siguientes parámetros:

K = 0.5 mA/V² y Vth = 2.5 V. El transistor MOS está encendido.

a) Determine el tipo de transistor MOS (Explique su respuesta)

b) Determine la región de operación del transistor T:

para RD = 1.5 k

para RD = 0.5 k

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 39

Ejemplo

2. Para el circuito MOSFET mostrado en la figura se tienen las constantes:

ID = 0.1 mA, VTN = 0.5 V, VDD = 3.3 V, R1 = 500 k , R2 = 750 k , R3=R4=10 k ,omita el efecto de substrato y la modulación de largo de canal.

a) Determine la región de operación del MOSFET

b) Calcule KN.

c) R3 se debe reemplazar por un transistor PMOS de enriquecimiento con|Vthp|= |Vthn| de manera que VDS del transistor NMOS no cambie. Dibuje elcircuito y determine KP.

Para resolver este ejercicio considere:

Movilidad de electrones: µn = 250 cm2/Vs

Movilidad de huecos: µp = 100 cm2/Vs

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 40

VDD

R1 R3

R2 R4

Ejemplo

3. Considere un transistor NMOS con tox = 20 nm, µn = 650 cm2/Vs, VTH = 0.8 Vy W/L = 10. Encuentre la corriente de drenador en los siguientes casos:

a) VGS = 5 V y VDS = 1 V

b) VGS = 2 V y VDS = 1.2 V

4. El transistor NMOS de la figura 1 tiene un parámetro de transconductanciade 2 mA/V2 y la magnitud de la tensión de umbral es de 1 V. Determine elpunto de operación del transistor para las siguientes situaciones:

a) RD = 4 k , RS = 3 k

b) RD = 7 k , RS = 3 k

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 41

Figura 1

Ejemplo

5. Para el circuito de la figura 2, el parámetro de transconductancia es 2 mA/V2

y la magnitud de la tensión de umbral es de 2 V. Determine el punto deoperación del transistor.

6. Encuentre el punto de operación para el circuito de la figura 3. El parámetrode transconductancia del transistor es de 0.2 mA/V2. La tensión de umbral esde 2 V.

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 42

Figura 2Figura 3

Ejemplo

7. Considere el circuito y las curvas características del MOSFET mostrados. Elvoltaje de umbral del transistor es 1.5 V. La resistencia R1 es de 100 k .Dimensione las resistencias RD, RS y R2 para que el transistor opere ensaturación con VDS polarizado en 1 V a partir del extremo de la región linealcon VD = 3 V. Para esto, ignore el efecto de substrato. Muestre en curvacaracterística el punto de operación del transistor para cumplir con esteobjetivo con mínima potencia.

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 43

Ejemplo

8. Para este circuito, R1 = 10 k , R2 = 5.15 k , RS = 2.1 k . Si el transistor sepone en corto, la potencia disipada en Rs sería de 170 µW. ¿Cuáles son losvalores VGS1, VGS2 y VGS3 a los que fueron medidas las curvas respectivas enlas características de salida? Utilizando el método gráfico, determine: el valorde VGS e IDS al que opera el circuito; el valor de VDS cuando el transistor operacon el valor de VGS e IDS encontrados; el valor de RD cuando el transistor operacon el valor de VGS, VDS e IDS encontrados.

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 44

5V

R1

R2 RS

RD

VGS (V) VDS (V)

Clase 22Modelo Analógico del MOSFET

Instituto Tecnológico de Costa Rica

Elementos Activos

Dr.-Ing. Juan José Montero Rodríguez

Semestre II-2019

Escuela de Ingeniería ElectrónicaSemestre II-2019

Objetivos

4. El transistor de efecto de campo MOSFET y la tecnología CMOS (8.5 semanas)

4.1 Construcción, símbolo, clasificación

4.2 Funcionamiento

4.3 Curvas características y polarización

4.4 Modelo del MOSFET para aplicaciones analógicas

4.5 Modelo del MOSFET para aplicaciones digitales

4.6 Aplicaciones digitales del MOSFET

4.7 Aplicaciones analógicas del MOSFET

4.8 Fabricación y escalamiento de MOSFETs

Objetivo

Conocer el comportamiento y modelado del transistor de efecto de campo MOSFET, así como sus principales aplicaciones.

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 46

Modelos del MOSFET

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 47

MOSFET

Simuladores/Cálculo Cálculo

Para aplicaciones analógicas

Para aplicaciones digitales

Pequeña señalGran señal

Baja frecuencia

Alta frecuencia

Modelo Analógico del MOSFET

Modelo analógico según región de operación

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 48

Comportamiento resistivo

Comportamiento de fuente de corriente

Comportamiento de fuente de corrienteen paralelo con una

resistencia

Modelo Analógico en Región Lineal

MOSFET se comporta como resistencia Rch (resistencia de canal)

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 49

lo cual para VDS << VDSAT puede aproximarse a

Por lo tanto, la resistencia de canal se calcula como

Modelo Analógico en Región de Saturación

MOSFET se comporta como fuente de corriente en paralelo con resistencia

ITCR - Elementos Activos

Constante, independiente de VDS

= fuente de corriente ideal IDSAT

resistencia

IDSATID-IDSAT

VDS-VDSAT

VDSAT

rO

ID

IDSAT VDS

+

-

Modelo de Pequeña Señal del MOSFET

En baja frecuencia, el modelo de pequeña señal del MOSFET es:

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 51

rogmvgs gmbvbs

+

-

vgs

G

S

B

D

+

-

vbs

Nótese que cuando VB < VS, el signo de Vbs es negativo y lacorriente de la fuente gmbVbs cambia de dirección, indicando una reducciónde la corriente entre drenador y surtidor, lo cual equivale a un aumentodel voltaje de umbral

Transconductancia

La transconductancia de un MOSFET se define como:

es decir, gm es la pendiente de la curva característica de transferencia iD-vGS, evaluada en el punto de operación

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 52

VTH

Aplicando la definición

ITCR - Elementos Activos ITCR - Elementos Activos

Resistencia de Salida

Modulación de largo de canal causa resistencia de salida

-VA = -1/

En saturación,

VA : voltaje de Early

Donde ID es la corriente IDS en saturación sin tomar en cuenta la modulación de largo de canal

Transconductancia de Substrato

La transconductancia de substrato de un MOSFET se define como:

ITCR - Elementos Activos

que también puede calcularse como

Donde

Modelo de Pequeña Señal en Alta Frecuencia

En alta frecuencia, el modelo de pequeña señal del MOSFET es:

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 55

rogmvgs gmbvbs

+

-

vgs

G

S

B

D

+

-

vbsCgs

Cgd Cgb

Cbs

Obtención del Modelo de Pequeña Señal

Los pasos a seguir para obtener el equivalente de pequeña señal son:

Determinar el punto de operación

análisis de circuitos

ecuaciones características

Calcular los parámetros de corriente alterna con los puntos de operación obtenidos

Reemplazar las fuentes de voltaje de corriente directa (CD) por cortos circuitos y las fuentes de corriente de CD por circuitos abiertos.

Reemplazar los elementos activos del circuito por sus equivalentes de pequeña señal de acuerdo con los parámetros de CA calculados

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 56

Ejemplo

Para el circuito mostrado en la figura, determine el valor de todas las tensiones y corrientes de los transistores en DC (modelo de gran señal) y en AC (modelo de pequeña señal). Además, compruebe la región de operación de todos los transistores, y calcule la resistencia del canal de los transistores que se encuentren en la región lineal.

Las constantes para cada transistor están descritas en la Tabla 6.2

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 57

Solución: Punto de operación DC

Para el análisis de gran señal, se debe apagar la fuente de 1 mV poniéndola en corto circuito. De esta manera, para ambos transistores VG1=VG2=2.5 V

Ambos tienen VS1=VS2 de manera que tienen el mismo VGS, por lo que por ambos fluye la misma corriente. Es decir, la corriente por M1 es la misma que por M2.

Transistores M1 y M2

Para M1 y M2, asumiendo que están en saturación (se verificará luego) se tiene:

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 58

Transistor M3

Para M3 se tiene el drain conectado con el source. Es decir, el transistor M3 está conectado como un diodo. Esto significa que opera en la región de saturación, porque siempre se cumple que:

Esto debido a que y por lo tanto la parte de la derecha siempre es menor que la parte de la izquierda.

En este punto se puede calcular la tensión utilizando la ecuación de saturación del transistor MOSFET, despejando

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 59

Punto de operación: rama de la izquierda

Ahora podemos calcular la tensión en todos los nodos de la rama de la izquierda:

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 60

Transistor Soluciones en DC hasta el momentoM1M2M3M4

Transistor M4

Para M4 se tiene que la tensión de manera que es muy difícil que el transistor opere en saturación. La condición de saturación es la siguiente:

Es decir, la tensión en el source del transistor M4 debe ser menor a 0.9 V para saturación.

Sin embargo, esto no puede cumplirse, porque la tensión en el source del transistor M2 se había calculado anteriormente como .

Por este motivo el transistor M4 está en la región lineal (triodo) de manera que podemos utilizar la ecuación de corriente lineal para determinar

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 61

Reacomodando en la forma canónica

De donde

Resolviendo la ecuación cuadrática para se obtiene

o

La solución correcta es por el siguiente análisis:

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 62

La resistencia del canal para el transistor M4 se calcula como:

De donde obtenemos de nuevo la tensión

Punto de operación: rama de la derecha

A partir del resultado anterior podemos calcular el punto de operación de la rama de la derecha.

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 63

Transistor Soluciones en DCM1M2M3M4

Solución: Análisis de AC

Para este análisis se puede calcular directamente la transconductancia de cada transistor de acuerdo con el punto de operación y los parámetros de fabricación. De esta manera:

El transistor M4 está operando como una resistencia, por lo que se modela como tal, no es necesario calcular una transconductancia. Además, el transistor M3 está operando como un diodo, por lo que podría ser reemplazado por una resistencia con valor

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 64

Transistor Soluciones en ACM1M2M3M4

Clase 23Aplicaciones Analógicas del MOSFET

Instituto Tecnológico de Costa Rica

Elementos Activos

Dr.-Ing. Juan José Montero Rodríguez

Semestre II-2019

Escuela de Ingeniería ElectrónicaSemestre II-2019

MOSFET conectado como diodo

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 66

Amplificadores MOSFET

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 67

Espejos de corriente MOSFET

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 68

Clase 24Modelo Digital del MOSFET

Instituto Tecnológico de Costa Rica

Elementos Activos

Dr.-Ing. Juan José Montero Rodríguez

Semestre II-2019

Escuela de Ingeniería ElectrónicaSemestre II-2019

Modelos del MOSFET

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 70

MOSFET

Simuladores/Cálculo Cálculo

Para aplicaciones analógicas

Para aplicaciones digitales

Pequeña señalGran señal

Baja frecuencia

Alta frecuencia

Modelo del MOSFET Para Aplicaciones Digitales

MOSFET como interruptorResistencia de conmutación

Asumir paso de corte a saturación en tiempo t 0

ITCR - Elementos Activos

Vc(0)=VDD

Modelo del MOSFET Para Aplicaciones Digitales

Resistencia de conmutación

Para calcular la resistencia de conmutación se toman los valores finales e iniciales de voltaje y corriente, como se muestra en el gráfico

ITCR - Elementos Activos

VDD

Pendiente = 1/R

t=0+ VGS=VDD, VDS=VDD

DDDSGS VVVDSI

t 5 VDS=0, IDS=0(el capacitor está descargado)

Capacitancias del MOSFET

Capacitancias del MOSFET

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 73

B

D G S

CGB

CSBCDB

CGD CGS

Intrínsecas-Independiente de voltaje

-Debido a fabricación: ej.: traslapes (Cov)

Extrínsecas-Dependiente de voltaje

-Influenciadas por presencia del canal

Capacitancias del MOSFET limitan su respuesta de frecuencia

Capacitancias del MOSFET

Region de operación CGB CGD CGS

Corte COX COV COV

Lineal COVB 1/2 COX 1/2 COX

Saturación COVB COV 2/3 COX

ITCR - Elementos Activos

B

D G S

p

-+

-- - - - ---n+ n+

B

D GS

p

-+

- -- --n+ n+

Compuerta y substrato aislados por canal

Canal conecta compuerta con drenador y fuente

Compuerta y substrato aislados por canal

Canal conecta compuerta con fuente

Capacitancias de traslape

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 75

B

D G S

p

-+

n+ n+

Cov Cov En la región de corte, CGD = CGS =COV = capacitancia por el traslape entre regiones de difusión y la compuerta

En las zonas lineal y de saturación, CGB = =COVB = capacitancia por el traslape entre la extensión de la compuerta y el substrato

D S

B

G

Para t < 0 Para t > 0

+ +-

VDD

-

VDD

Modelo del MOSFET Para Aplicaciones Digitales

Para comprender los efectos capacitivos, considere primero lo siguiente:

ITCR - Elementos Activos

El circuito puede dividirse en un circuito de entrada y un circuito de salida con el doble de la capacitancia

V=2VDD

Q= C*2VDD

V=VDD

Q= 2C*VDD

Modelo del MOSFET Para Aplicaciones Digitales

Efectos capacitivos

ITCR - Elementos Activos

Asuma que la capacitancia entre compuerta y drenador, así como la capacitancia entre compuerta y surtidor es 0.5Cox (operación en la zona lineal).

Esta es una sobreestimación del valor de la capacitancia, para calcular el peor de los casos.

La capacitancia entre compuerta y drenador conecta la entrada con la salida.

Separando la capacitancia entre compuerta y drenador en una capacitancia equivalente entre la entrada y tierra, y la salida y tierra se tiene el circuito de la derecha

Modelo del MOSFET Para Aplicaciones Digitales

El modelo equivalente incluyendo efectos capacitivos es, entonces

ITCR - Elementos Activos

oxdsoutn CCC

Clase 25Aplicaciones Digitales del MOSFET

Instituto Tecnológico de Costa Rica

Elementos Activos

Dr.-Ing. Juan José Montero Rodríguez

Semestre II-2019

Escuela de Ingeniería ElectrónicaSemestre II-2019

Objetivos

El transistor de efecto de campo MOSFET y la tecnología CMOS (8.5 semanas)

Construcción, símbolo, clasificación.

Funcionamiento.

Curvas características y polarización.

Modelo del MOSFET para aplicaciones analógicas.

Modelo del MOSFET para aplicaciones digitales.

Capacitancias internas y modelos de alta frecuencia.

Aplicaciones: El FET como interruptor: interruptor serie, paralelo, inversor lógico y compuertas lógicas básicas

Escalamiento de MOSFETs

Objetivo

Conocer el comportamiento y modelado del transistor de efecto de campo MOSFET, así como sus principales aplicaciones.

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 80

Ecuaciones I-V del MOSFET

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 81

Región NMOS PMOSCorte (Sub-umbral)

Región Lineal (triodo)

MOSFET como Interruptor Serie: NMOS

En el primer caso, el transistor se ve afectado por el efecto de substrato

substratodeefectonoVVVK

I THTHDDD 02

0 ,)(2

ITCR - Elementos Activos

PMOS como Interruptor Serie

En el segundo caso, el transistor se ve afectado por el efecto de substrato

ITCR - Elementos Activos

Inversor CMOS

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 84

Vin > VTHN , Vin = VDD NMOS activado, PMOS inactivo

Vout = 0V: NMOS en región lineal, PMOS en región de corte

CMOS: Complementary Metal Oxide Semiconductor (1963)Circuitos con transistores PMOS y NMOS

Curva de Transferencia de Tensión

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 85

N

Compuertas Lógicas: Compuerta NAND

Entrada lógica Voltaje de entrada Salida lógica Voltaje de salida

A=0, B=0 VA=0, VB=0 1 VDD

A=0, B=1 VA=0, VB=VDD 1 VDD

A=1, B=0 VA=VDD, VB=0 1 VDD

A=1, B=1 VA=VDD, VB=VDD 0 0

ITCR - Elementos Activos

Compuertas Lógicas: Compuerta NOR

Entrada lógica Voltaje de entrada Salida lógica Voltaje de salida

A=0, B=0 VA=0, VB=0 1 VDD

A=0, B=1 VA=0, VB=VDD 0 0

A=1, B=0 VA=VDD, VB=0 0 0

A=1, B=1 VA=VDD, VB=VDD 0 0

ITCR - Elementos Activos

Arreglos de Transistores

ITCR - Elementos Activos

¿Cuál es la función lógica de este circuito?

ITCR - Elementos Activos

Vout

Tierra

Consumo de Potencia

Consumo

de potencia

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 90

Potencia Estática

Potencia Dinámica

Corriente de fuga de compuerta

Corriente de subumbral

Corriente de reversa de juntas PN

Corriente de corto circuito

Carga capacitiva

Disipación por carga capacitiva >> Potencia corto circuito >> Potencia estática

En general, en los circuitos integrados,

Potencia Estática

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 91

Corriente de fuga de compuerta

Corriente de subumbral (VGS < 0)

Corriente de reversa de juntas PN

Substrato

Drenador Compuerta Fuente

Substrato

Drenador Compuerta Fuente

I

Substrato

Drenador Compuerta Fuente

Potencia Dinámica

Potencia dinámica debido a corriente de corto circuito

ITCR - Elementos Activos

Para VIN=VOUT ambos transistores operan en saturación

ambos transistores conducen, permitiendo un flujo de corriente de VDD a tierra

Corriente de corto circuito

Potencia disipada:

tr : tiempo de subida (se asume tr = tf) T: período de VIN

Potencia Dinámica

Potencia dinámica debido a cargas capacitivas

ITCR - Elementos Activos

CL

Capacitancia de carga debido a:

-COX de compuertas siguientes-COX propia-CW, capacitancia parásita de interconexión

Representadas por CL

Potencia disipada:

f : frecuencia de conmutación, CL: capacitancia de carga, A: factor de actividad

A: factor de actividad = probabilidad de conmutación

Clasificación de Memorias

Basadas en transistores MOSFET para lograr alta densidad

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 94

Memorias semiconductoras

No volátiles Volátiles

Programadas por máscara (ROM)ROM Programable (PROM)

ROM Borrable (EPROM)ROM Eléctricamente borrable

(EEPROM)

De Acceso Aleatorio (RAM)RAM estática (SRAM)

RAM dinámica (DRAM)

Organización de Memorias

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 95

Datos

Dec

odifi

cad

or d

e f

ila

Dirección de fila

Línea de columna(bitline)

Línea de fila(wordline)

En cada intersección hay una celda de

memoria

Decodificador de ColumnaCircuitos de E/S

Arreglo de Celdas

Dirección de columna

Organización de una Memoria (2)

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 96

wordline

bitlines

Arreglo de Celdas

Dirección de columna

Dirección de fila

Dec

odifi

cad

or d

e f

ila

Decodificador de ColumnaCircuitos de E/S

palabra

Celda de Memoria SRAM

Las memorias RAM son volátiles = pierden los datos al remover la alimentación

SRAM: Static Random Access Memory

Cada celda almacena un bit, se requieren 6 transistores por bit

Celda SRAM: cerrojoDos inversores mutuamente acopladosDos transistores de acceso al cerrojo

Transistores de línea de palabra conectan el cerrojo con los circuitos de lectura y escritura

ITCR - Elementos Activos

¿Cómo se implementa una celda SRAM?

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 98

Lectura de una celda SRAM

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 99

Procedimiento de lectura

Precargar las líneas de bit a VDD

Igualar niveles de tensión de ambas líneasDesactivar precarga y ecualizaciónActivar línea de palabraEsperar hasta que haya una diferencia de 100mV entre ambas líneas de bitDesactivar línea de palabraActivar amplificador de sensadoAmplificarTransmitir el dato a la salida

Celdas de Memoria DRAM

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 100

DRAM: Dynamic Random Access Memory

El transistor de línea de palabra connecta el capacitor de almacenamiento con el circuito de lectura/escritura

Corriente de fuga descarga capacitor dato debe reescribirse periódicamente= refrescamiento de datos

Capacitancia de columna

(Bitline capacitance)

Celda de memoria DRAM

Capacitancia de almacenamiento

Memorias no Volátiles

No volátil = Mantienen los datos aún sin tensión de alimentación

Se clasifican por sus métodos de programación y borrado

Programables o no por el usuario

Borrables eléctrica u ópticamente

Principio de almacenamiento de datos:

Durante el proceso de fabricación

Por conexiones programables (ej: fusibles)

Por cambio de voltaje de umbral

EEPROM y EPROM

Métodos eléctricos de escritura y borrado son destructivos

Número de ciclos de escritura-borrado es restringido (mínimo 100 mil)

Tiempo de retención de datos es restringido (mínimo 10 años)

FLASH es un tipo de EEPROM

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 101

Clasificación de Memorias No Volátiles

Tipo Costo Programabilidad

Tiempo de programación

Tiempo de

borrado

ROM bajo Por máscara Semanas No borrable

PROM bajo Una vez, eléctricamente Segundos No borrable

EPROM Medio Hasta 100 mil veces, eléctricamente

Segundos 20 minutos (luz UV)

Flash Alto Hasta 100 mil veces, eléctricamente

100 s Por bloques, eléctricamente

EEPROM Alto Hasta 100 mil veces, eléctricamente

100 s 10 ms por byte,

eléctricamente

ITCR - Elementos Activos

Memoria no Volátil de Compuerta Flotante

Poly 2 opera como compuerta del transistor

Poly 1 opera como compuerta flotante para almacenamiento de portadores de carga

Compuerta flotante: no hay contacto eléctrico directo

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 103

EEPROM

Almacenamiento de información se representa con cambios en el voltaje de umbral

El cambio en el voltaje de umbral se logra inyectando portadores de carga en la compuerta flotante y extrayéndolos de ella

Degradación de óxido limita número de ciclos de escritura-borrado y el tiempo de retención de datos

Dos métodos principales de inyección y extracción:

Inyección de portadores de carga calientesFowler-Nordheim Tunneling

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 104

Vcg Vcg

Jerarquía de Memoria

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 105

more expensive Clase 26Escalamiento de MOSFETs

Instituto Tecnológico de Costa Rica

Elementos Activos

Dr.-Ing. Juan José Montero Rodríguez

Semestre II-2019

Escuela de Ingeniería ElectrónicaSemestre II-2019

La Revolución de la Microelectrónica

When you see the numbers or hear yourname on the evening news

you are once again reminded that this is no longer an industry, but an economic and cultural phenomenon, a crucial force at the heart of themodern world

(G. Moore)

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 107

50nm 30nm 20nm 15nm

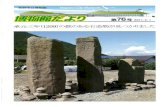

El Primer Transistor

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 108

1947Bardeen, Brattain, Schockley

1956: Premio Nobel

Patente del efecto de campo: 1925 LillienfeldPatente del MOSFET: 1928 Lillienfeld

Problema de fabricación del MOSFET: calidad del aislante

El primer Circuito Integrado

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 109

Tecnología de circuitos integrados:inventada por Jack Kilby, de Texas Instruments en 1958

Primer Circuito Integrado Planar

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 110

19612 pulgadas de diámetro4 transistores y algunasresistencias

Evolución del Poder Computacional

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 111

Cál

culo

s p

or s

egu

ndo

por

$1

000

Ley de Moore

(G. Moore)

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 112

ú

Gordon Moore 1965

Ley de Moore en Memorias DRAM

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 113

Escalamiento del MOSFET

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 114

El avance del MOSFET de una generación tecnológica a la siguiente se rige por la teoría de escalamiento

Escalamiento

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 115

Predicción de Escalamiento

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 116

High Volume Manufacturing

2004 2006 2008 2010 2012 2014 2016 2018

Feature Size 90nm 65nm 45nm 32nm 22nm 16nm 11nm 8nm

Integration Capacity (Billions of Transistors)

2 4 8 16 32 64 128 256

Transistor for 90nm Process

Source: Intel

Influenza VirusSource: CDC

Teoría de Escalamiento

Las dimensiones del transistor pueden escalarse en un factor S > 1, si el campo eléctrico se mantiene constante

Factor de escalamiento 1.4 por generación tecnológica

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 117

Dos tipos de escalamiento: de campo constante y de voltaje constante

B

D G S

B

D SG

S

Escalamiento de Campo Constante

Magnitud Dimensión original Escalamiento

Largo de canal L L/S

Ancho de canal W W/S

Espesor de óxido tOX tOX / S

Profundidad de difusión de fuente y drenador

xj xj /S

Voltaje V V/S

Concentración de dopado de substrato

NA, ND NA*S, ND*S

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 118

Objetivo: mantener constante el campo eléctrico en el transistor y con ello, el comportamiento de un transistor de canal largo

La concentración de dopado de substrato se aumenta para escalar el ancho de la zona de agotamiento

Escalamiento de Campo Constante

Magnitud Valor original Escalamiento

Corriente de drenador IDS IDS /S

Área del transistor A A/S2

Capacitancia de óxido COX COX / S

Retardo de compuerta /S

Consumo de Potencia Ps Ps / S2

Densidad de potencia PD PD

Producto potencia-retardo PDP PDP/S3

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 119

Efectos del escalamiento de campo constante

Compuertas más rápidas Mayor densidad de integraciónDensidad de potencia constante

Escalamiento de Voltaje Constante

Magnitud Dimensión original Escalamiento

Largo de canal L L/S

Ancho de canal W W/S

Espesor de óxido tOX tOX / S

Profundidad de difusión de fuente y drenador

xj xj /S

Voltaje V V

Concentración de dopado de substrato

NA, ND NA*S2, ND*S2

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 120

Objetivo: mantener constante voltaje en el transistor e intentar minimizar incrementos en el campo eléctrico

Se pretende mantener compatibilidad de voltajes entre generaciones tecnológicas

Escalamiento de Voltaje Constante

Magnitud Valor original Escalamiento

Corriente de drenador IDS IDS*S

Área del transistor A A/S2

Capacitancia de óxido COX COX/S

Retardo de compuerta /S2

Consumo de potencia P P*S

Densidad de potencia PD PD* S3

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 121

Efectos del escalamiento de voltaje constante

Compuertas más rápidas Mayor densidad de integraciónDensidad de potencia aumenta problemas de disipación de calor

Consumo de Potencia de Procesadores

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 122

Calentamiento en circuitos integrados

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 123

Efectos del Escalamiento

Voltaje de umbral escala

Pendiente de subumbral constante

Aumento de corriente de subumbral VTH debe ajustarse para mantenerla aproximadamente constante

Reducción de voltaje de alimentación

Ajuste de VTH disminuye el voltaje efectivo VGS-VTH

Debe elegirse entre alto desempeño y mayor corriente de subumbral o entre menor desempeño y menor corriente de subumbral

Compuertas más rápidas, mayor densidad de integración

Densidad de potencia aumenta problemas de disipación de calor

Efectos de canal corto

Aumento en corrientes de fuga de compuerta (VTH, tox)

Degradación por inyección de portadores de carga calientes

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 124

Consecuencias del Escalamiento

El escalamiento del MOSFET causa efectos que desvían su comportamiento del MOSFET de canal largo, entre los que están

Efecto de canal corto (short channel effect)

Perforación de canal (Punch-through)

Fuga de compuerta (gate leakage)

Electromigración

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 125

Fuga de Compuerta

Óxido se escala para mantener el control de la compuerta sobre el canal

Escalamiento de óxido aumenta la corriente de fuga de compuerta

Efecto de tunneling cuántico (quantum mechanical tunneling)

Aumenta potencia de stand-by

Óxido no puede escalarse a tox < 1 nm: solución = HfO2

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 126

Electromigración

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 127

Resultado de la transferencia de momentum de los electrones a los iones metálicos que forman

la red cristalina del material de interconexión

Desplazamiento gradual de los átomos metálicos de un conductor como resultado de la corriente fluyendo en dicho conductor

Escalamiento en Tecnología Intel

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 128

El Transistor MOSFET Moderno

Three gate: Mejor control del canal

Dieléctrico: HfO2

Gate: Metal (TiN para NMOS, aleación TiNAl para PMOs), con capa de baja resistencia para contacto

Canal: SiGe (strain engineering), para aumentar movilidad

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 129

Tensión (NMOS) Compresión (PMOS)

¿Qué nos espera?

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 130

ITRS

International Technology Roadmap of Semiconductors

Patrocinado por las cinco regiones líderes en manufactura de semiconductores en el mundo

Resume avances de la industria microelectrónica, analiza y predice tendencias en microelectrónica

Diagnostica problemas actuales para mantener el escalamiento

Según ITRS, tecnología MOSFET puede llegar a alcanzar el año 2020

Analiza tecnologías emergentes

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 131

www.itrs2.net

Clase 27El Proceso de Fabricación CMOS

Instituto Tecnológico de Costa Rica

Elementos Activos

Dr.-Ing. Juan José Montero Rodríguez

Semestre II-2019

Escuela de Ingeniería ElectrónicaSemestre II-2019

El Proceso de Fabricación CMOS

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 133

Fabricación de Circuitos Integrados

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 134

Fabricación

PruebasDefectuoso

Pruebas finales

Separación

De dados

Ensamblado y

encapsulado

Preparación

de obleas

Técnicas de Fabricación

Las principales técnicas para fabricación de circuitos integrados son:

Obtención de silicio cristalino

Oxidación térmica

Litografía

Dopado

Deposición

Decapado

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 135

Obtención de Silicio Ultrapuro

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 136

SiO2 impuro (sílica)

SiO2 + C Si + CO2

(a 900ºC, Si de grado metalúrgico, 99% pureza)

Si + 4Cl SiCl4 (Líquido)3SiCl4 + Si + 2H2 3

Destilación: SiCl4 o HSiCl3ultrapuro

SiCl4 + 2H2 4HCl + Si2 HSiCl3 4

(1150ºC)

Si ultrapuro policristalino

Obtención de Lingotes de Si Cristalino

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 137

Método de Czochralski:

Derretir silicio policristalino y mantenerlo a T < 1417 °C

Introducir un cristal semilla

Controlar el crecimiento del lingote por medio de la velocidad de extracción, temperatura de fusión y velocidad de rotación

Cristal semilla

Si policristalino derretido

Aislamiento térmico

Si cristalino

Elemento de calentamiento

Rotación y extracción

2 Métodos: Czochralski y Floating Zone

Obtención de Lingotes de Si Cristalino

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 138

Obtención de Lingotes de Si Cristalino

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 139

Método de Zona Flotante

Lingote de Si policristalino de alta pureza

Inductor calienta una zona del lingote y lo derrite

Impurezas se difunden del sólido al líquido, dejando el sólido purificado

Sólido sigue el patrón del cristal semilla

Obtención de Obleas

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 140

Corte de flat grind

Corte de obleas

Identificación de oblea

Decapado químico

Pulido

Limpieza de la superficie

Preparación de superficie con pulido químico-mecánico (CMP, chemical mechanicalpolishing)

Oxidación Térmica

Creación de capas de óxido

Hornear las obleas en un horno de alta temperatura (900ºC < T < 1200ºC) en presencia de oxígeno o agua

Si + O2 2 (oxidación seca)

O bien

Si + 2H2 2 +H2 (oxidación húmeda)

El tiempo de oxidación y la temperatura determinan el espesor de la capa de óxido

Oxidación seca produce óxido de mejor calidad

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 141

Litografía

Creación de patrones para alterar o moldear la forma existente de una capa de material depositado

Se realiza con ayuda de una máscara o retícula que transmite el patrón a la capa por

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 142

Fotoresistencia:

Material que cambia su solubilidad al contacto con la luz

Decapado

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 143

Alterar o moldear la forma existente de una capa de material depositado

Consiste en remover selectivamente el material depositado según el patrón establecido con ayuda de la litografía

Decapado por bombardeo de iones

Decapado químico = decapado húmedo

Dopado por Difusión

Fuente de dopantes: son óxidos en forma sólida, líquida o gaseosa

El contacto del silicio con el dopante a altas temperaturas (900ºC <T<1200ºC) provoca una reacción en la superficie del silicio, creando una capa de material altamente dopado.

Los dopantes se difunden a partir de esta capa hacia la oblea

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 144

Horno de difusión

Substrato

Reactantes gaseosos

Deposición de fuente de

dopantes

Dopado por Implantación

Implantación iónica: gas dopante se ioniza y se acelera contra la superficie de la oblea, implantando los átomos dopantes.

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 145

La profundidad de penetración depende de la energía de implantación.

Después de la implantación, la oblea se calienta para activar la difusión de los dopantes.

Deposición Química

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 146

Flujo continuo de gas

Capa depositada

Substrato

Difusión de reactantes

Deposición química gaseosa

Gas inerte actúa como portador de reactante

Reactante reacciona con la superficie caliente del sólido, depositando la capa

Deposición Física

Ejemplo: Sputtering

Target (disco de material por ser depositado) bombardeado por iones de gas inerte

Átomos del target se desprenden y depositan en la oblea

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 147

Pruebas

Pueden hacerse a nivel de oblea o a nivel de circuitos encapsulados

Se descartan dados defectuosos y se diagnostican fallas de fabricación

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 148

Sección Transversal de un Procesador AMD

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 149

Metal Layer #6

Metal Layer #5

Metal Layer #4

Metal Layer #3

Metal Layer #2

Metal Layer #1Isolation Trench

PolySi Gate

Passivation

Ejemplo de Niveles de Interconexión

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 150

También llamados niveles de metalización

Sección Transversal de Proceso CMOS de Dos Tinas

1. Tinas

2. Aislamiento

3. Compuerta

4. Regiones de difusión

5. Espaciador laterial

6. Contacto

7. Interconexión local (poli-Si)

8. Aislamiento de capas/contacto Poli-Metal1

9. Metal1

10. Aislamiento Metal1-Metal2

11. Metal2, Via2, Aislamiento Metal2-Metal3

12. Metal 3

13. Pad metálico para contacto con encapsulado

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 151

Passivation layer Bonding pad metal

p+ Silicon substrate

LI oxide

STI

n-well p-well

ILD-1

ILD-2

ILD-3

ILD-4

ILD-5

M-1

M-2

M-3

M-4

Poly gate

p- Epitaxial layer

p+

ILD-6

L1 Poly-Si

Via

p+ p+ n+n+n+ 2

3

1

4

5

46

7

8

9

10

11

12

13

Proceso de Fabricación CMOS (2 tinas)

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 152

Substrato P

SiO2

Si3N4

Fotoresistencia

Decapado de nitruro de silicio para definir las áreas activas:

El nitruro se mantiene donde se va a integrar un transistor

Proceso de Fabricación CMOS

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 153

Substrato P

Implantación iónica de tina P para transistor NMOS

Definición de zonas activas, separadas por zonas de

aislamiento

(Shallow trench isolation)

Óxido de campo: óxido de aislamiento entre transistores

Boro

P

Proceso de Fabricación CMOS

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 154

Implantación iónica de tina N para transistor PMOS

Difusión de dopantes se activa con temperatura para alcanzar

profundidad de tina requerida

Fósforo

PN

Tina N Tina P

Proceso de Fabricación CMOS

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 155

Implantación iónica para ajuste de VTH de transistor NMOS

Boro

Tina N Tina P

Tina N Tina P

Implantación iónica para ajuste de VTH de transistor PMOS

Arsénico

Proceso de Fabricación CMOS

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 156

Creación de óxido de compuerta

(oxidación térmica)

Tina N Tina P

Tina N Tina P

Deposición del silicio policristalino de compuerta

Proceso de Fabricación CMOS

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 157

Decapado para moldeado de compuerta

Tina N Tina P

Implante de regiones de difusión N para drenador y surtidor

de transistor NMOS

Fósforo

Proceso de Fabricación CMOS

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 158

Tratamiento de áreas de contacto para lograr contactos óhmicos

Creación de óxido de aislamiento entre capas

Implante de regiones de difusión P para drenador y surtidor

de transistor PMOS

Boro

Aislamiento entre capas

Titanio TiSi2

Proceso de Fabricación CMOS

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 159

Deposición de vías

Decapado de contactos

Proceso de Fabricación CMOS

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 160

Deposición y moldeado de los siguientes niveles de

aislamiento y metalización

Deposición de metal y moldeado de metal

Difusión vs Implantación

Difusión Implantación

Proceso de alta temperatura Temperatura ambiente

Fuente de dopantes: sólido, líquido o gaseoso

Fuente de dopantes: iones

Temperatura repara defectos en silicio durante el proceso

Causa daños al silicio, requiere tratamiento posterior de alta temperatura para reparar

los daños

Permite dopados de alta concentración, materiales resultantes de baja resistividad

Dopados con concentraciones menores, 10 veces mayor resistividad

Menos precisión

(concentración y profundidad)

Proceso de alta precisión

(concentración y profundidad)

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 161

Clase 28El Flujo de Diseño Analógico: Back-End

Instituto Tecnológico de Costa Rica

Elementos Activos

Dr.-Ing. Juan José Montero Rodríguez

Semestre II-2019

Escuela de Ingeniería ElectrónicaSemestre II-2019

Objetivos

Principios de fabricación de circuitos integrados (2.5 semanas)

El proceso de fabricación CMOS: materiales, técnicas y flujo de fabricación, prevención de efecto de enganche

Integración de elementos pasivos, capacitores conmutados para integración de resistencias.

Principios de layout e introducción al flujo de back-end

Objetivos

Conocer los principios de fabricación de circuitos integrados CMOS

Aplicar técnicas básicas de layout y principios básicos del flujo back-end

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 163

El Flujo de Diseño Analógico

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 164

Especificacionesde diseño

Entrada de diseño

Simulación de prelayout

Layout

Frecuencia

Potencia

Ancho banda

Area ...

Crear esquemático

Dimensionamiento

Simulación

Rediseño

Planea-miento

Posiciona-miento

Enrutado

Front end Back end

El Flujo de Diseño Analógico

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 165

Verificación ExtracciónExtracción de

elementos parásitos

Simulación postlayout

Verificación de reglas de diseño

Verificación de reglas eléctricas

Extracción

Layout vs esquemático

Extracción de

elementos parásitos

Simulación con

elementos parásitos

Rediseño

Front end Back end

Flujo de Back End

Back-end: diseño físico y verificación del diseño después del diseño físico

Incluye una serie de verificaciones para asegurar fabricación exitosa:

Verificación de reglas de diseño (DRC)

Verificación de layout contra esquemático (LVS)

Extracción de elementos parásitos

Simulación de postlayout

Puede incluir también verificación de reglas eléctricas (ERC) y de errores de antena

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 166

Layout

Layout: representación geométrica de los componentes a integrar y sus interconexiones

Los componentes se representan con diferentes colores y polígonos

Colores representan materiales y propiedades

Polígonos representan la forma en la que se debe moldear una capa durante la fabricación = forma final que debe tener la capa

El layout se utiliza para obtener la información para fabricar las máscaras

Debe cumplir las reglas de diseño del fabricante

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 167

Reglas de Diseño

Define geometría permitida y relaciones geométricas permitidas en el proceso de fabricación

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 168

Reglas definidas por las característicasdel proceso de fabricación

Deben respetarse para asegurar que el chip sea fabricado correctamente

Verificación de reglas de diseño (DRC, design rules check)

Reglas de Diseño

Reglas de diseño incluyen restricciones de 4 tipos:

Ancho: precisión de litografía y de otros pasos de fabricación define el ancho (y largo) mínimo de un polígono

Espaciamiento: fabricación impone restricciones de espaciamiento entre estructuras. Ej: evita corto circuitos y efectos de enganche

Encapsulamiento: distancia mínima de traslape entre una estructura interna y otra que debe rodearla: Ej: contactos deben estar rodeados de metal para asegurar contacto eléctrico entre las capas por conectar

Extensión: algunas estructuras deben extenderse más allá del borde de otras estructuras. Ej: compuerta de polisilicio debe extenderse más allá de las regiones de difusión a su lado

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 169

Extracción

Extracción: los polígonos del layout y sus intersecciones deben interpretarse para verificar que los componentes y conexiones fueron representados correctamentePermite conocer el impacto de elementos parásitos: resistencias y capacitancias parásitas, diodos parásitosInformación requerida para creación de máscaras

Existen herramientas de software para la extracciónRequieren dibujo de capas físicasRequieren dibujo de capas auxiliares para la interpretación de los componentes representados = capas lógicas

Dos tipos de capas:De máscara: utilizadas para crear las máscaras para fabricación Lógicas (de definición): ayuda para la herramienta de extraccióny verificación; no se utilizan en durante la fabricación del chip

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 170

Layout vs Esquemático

Una vez interpretado el layout (extraído), debe verificarse que los componentes y conexiones presentes representan el circuito que se diseñó en el esquemático

Esta verificación se conoce como LVS (layout versus esquemático)

Se revisa cada componente, así como sus interconexiones

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 171

Simulación de Postlayout

Los elementos parásitos presentes y su magnitud sólo pueden saberse después de finalizar el layout

En las primeras simulaciones, no se tomaron en cuenta estos elementos

Simulación de postlayout:

Verificación de características y funcionalidad del circuito tomando en cuenta los elementos parásitos

Elementos parásitos pueden afectar el funcionamiento del circuito puede requerir rediseño completo

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 172

Sección Transversal de un Inversor CMOS

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 173

poly

substratopozo n

p+ n+ n+ n+p+ p+

metal 1

contactos

Layout vs Sección Transversal

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 174

Layout vs Sección Transversal

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 175

Layout vs Sección Transversal

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 176

Layout de Inversor

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 177

Ejemplo de Layout con Proceso Comercial

Nombre del contacto Descripción

VIA_C Contacto entre MET1 y MET2

VIA1_C Contacto entre MET2 y MET3

VIA2_C Contacto entre MET3 y MET4

P1_C Contacto entre MET1 y POLY1

P2_C Contacto entre MET1 y POLY2

ND_C Contacto entre MET1 y N-tub

PD_C Contacto entre MET1 y substrato P

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 178

Errores de Antena

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 179

Integración de Resistencias

Wt

LR

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 180

Espesor de conductor es definida por el proceso

Resistencias integradas presentan una tolerancia de ±20%

(precisión de la litografía, decapado y difusión, además de variaciones en el espesor la interconexión)

L: longitud de interconexión; t: espesor de interconexión

W: ancho de interconexión

L

tW

Métodos: -Interconexión de silicio policristalino dopado

-Regiones de difusión

Integración de Resistencias

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 181

en una estructura compacta

Capacitores Conmutados

Permiten emular resistencias de gran valor ocupando un área de fabricación menor (ej: 1 M )

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 182

Capacitores Conmutados

11 CVQ

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 183

Integración de Capacitores

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 184

Rango de capacitancia posible en fabricación: < 100 pF

Técnicas

Transistor MOS: B,S y D al mismo potencial para formar una placa, G es la otra placa. Polarizado en inversión

Óxido delgado sobre área de difusión fuertemente dopada y silicio policristalino o metal como placa superior

Pila de primer nivel de polisilicio, óxido y segundo nivel de polisilicio

Poly 1

Poly 2

Metal 1

Contacto

Proceso CMOS con Componentes Pasivos

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 185

Definición de capas de dibujo

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 186

poly

substratopozo n

p+ n+ n+ n+p+ p+

metal 1

contactos

Metal 2: moradoMetal 3: AmarilloPoly 2: rosado

Práctica layout

Dibuje:

Contacto entre metal 1 y poly1

Contacto entre metal1 y poly2

Contactos entre las capas de metal: 1-2, 2-3,1-3,

Contacto al substrato p

Contacto al pozo n

Diagrama de dos transistores P adyacentes, 2 N adyacentes

Anillos de potencia con GND en el anillo interno

Capacitor Poly1-Poly2

Layout de una compuerta de transmisión

Layout de una NAND con (W/L)NMOS =1, (W/L)PMOS=3 , L = Lmín

Layout de una NOR con (W/L)NMOS =1, (W/L)PMOS=3 , L = Lmín

Dr.-Ing. Juan José Montero R. ITCR - Elementos Activos 187

![CONVERSÃ O DE ENERGIA [Modo de Compatibilidade] · 2 phvpr gdv olqkdv gh iruod gr fdpsr pdjqpwlfr. 9hwru ,qgxomr 0djqpwlfd $ % & ' % ' % $ % & % % 1 6 2ulhqwdomr gh xpd %~vvrod $](https://static.fdocuments.net/doc/165x107/5fda9a5ea0d663170010208c/conversf-o-de-energia-modo-de-compatibilidade-2-phvpr-gdv-olqkdv-gh-iruod-gr.jpg)

![o · 2020. 6. 23. · d e ] } v o µ o ] À } î ì í õ ~ í ì ì 9 v d Ì } î ì î ì ,pijhqhv vdwholwdohv,ghqwlilfdflyq \ gljlwdol]dflyq gh sdufhodv djutfrodv 7udedmr hq fdpsr](https://static.fdocuments.net/doc/165x107/613f445da7a58608c268d049/o-2020-6-23-d-e-v-o-o-9-v-d-oe-.jpg)

![GH QRYHPEUR GH 'LUHWRU 3UHVLGHQWH 6mR 3DXOR GH IHYHUHLUR GH€¦ · gh vhuylorv rx txh whqkdp lqwhuhvvh hp uhvxowdgr gh surfhvvrv gh olfhqfldphqwr rx uhjxodul]domr dpelhqwdo rx gh](https://static.fdocuments.net/doc/165x107/5ec16007d2b2c9169c0ccde1/gh-qryhpeur-gh-luhwru-3uhvlghqwh-6mr-3dxor-gh-ihyhuhlur-gh-gh-vhuylorv-rx-txh-whqkdp.jpg)

![16.Biogeografia2017 [Modo de compatibilidad]evolucion.fcien.edu.uy/Diapositivas/16.Biogeografia2017.pdf · )lorjhrjuditd /d ilorjhrjuditd hv xq fdpsr gh lqyhvwljdflyq sulqflsdophqwhghglfdgrdohvwxglrghorvsulqflslrv\](https://static.fdocuments.net/doc/165x107/5c0ee35109d3f282728d3688/16biogeografia2017-modo-de-compatibilidad-lorjhrjuditd-d-ilorjhrjuditd.jpg)

![L07 CNA in tehnologie CMOS - · PDF file&1$ vq whkqrorjlh &026 l ,rxw fxujh sulq uh]lvwruxo gh uhdf lh l jhqhuhd] whqvlxqh gh lh luh 'lq sxqfwxo gh yhghuh do xqhl uhsuh]hqw ul vqwuhjl](https://static.fdocuments.net/doc/165x107/5a8426ce7f8b9a882e8b4924/l07-cna-in-tehnologie-cmos-1-vq-whkqrorjlh-026-l-rxw-fxujh-sulq-uhlvwruxo.jpg)

![PADRÃO TISS - ANS · 2019-09-27 · 3dgumr 7,66 &rpsrqhqwh 2ujdql]dflrqdo ± vhwhpeur gh rxwud jxld gh 63 6$'7 h ghyh vh lqirupdu r q~phur gd jxld sulqflsdo gh 63 6$'7 qr fdpsr ³](https://static.fdocuments.net/doc/165x107/5e7d43814b20b71a8b3f1db3/padrfo-tiss-2019-09-27-3dgumr-766-rpsrqhqwh-2ujdqldflrqdo-vhwhpeur.jpg)

![5HVXOWDGRV *HQHUDO SRU 6H[R file5hvxowdgrv *hqhudo sru 6h[r gh rfwxeuh gh ;;;,9 &urvv 6dq 5didho gh od $oedlgd &yugred /lvwdgrv &ux]fdpsr &duuhud 3uxhed 5hlqd 'lvwdqfld p](https://static.fdocuments.net/doc/165x107/5e0a78ef522d00507758b0f6/5hvxowdgrv-hqhudo-sru-6hr-hqhudo-sru-6hr-gh-rfwxeuh-gh-9-urvv-6dq-5didho.jpg)

![2020 cartel en A4 clubes - atletismolasalleteruel.com · 6h dgplwluiq wdpelpq lqvfulsflrqhv hq ho fdpsr gh 3lqlood ho plvpr gtd gh od fduuhud &rrujdql]d &oxe 3rolghsruwlyr /$ 6$//(](https://static.fdocuments.net/doc/165x107/5f8c241c1299f95b7f53dec9/2020-cartel-en-a4-clubes-at-6h-dgplwluiq-wdpelpq-lqvfulsflrqhv-hq-ho-fdpsr-gh.jpg)