The TSV Revolution and Fermilab’s MPW Run Experiences R. Yarema Fermilab TIPP 2011, Chicago June...

-

Upload

colin-cook -

Category

Documents

-

view

216 -

download

0

Transcript of The TSV Revolution and Fermilab’s MPW Run Experiences R. Yarema Fermilab TIPP 2011, Chicago June...

The TSV Revolution and

Fermilab’s MPW Run Experiences

R. YaremaFermilab

TIPP 2011, ChicagoJune 8-13

2TIPP 2011, Chicago

Introduction

• A revolution is taking place in the semiconductor world that is due to acceptance of through silicon vias (TSVs) as an option to improve circuit performance and as a complementary approach to transistor scaling. With TSVs, an IC can now be considered a device where connections can be made to either the top or bottom side. The ability to have TSVs leads to several different applications such as WLP (Wafer Level Packaging), SiIP (Silicon Interposers), and 3D integrated circuits.

TIPP 2011, Chicago 3

3D Integration Platforms with TSVs• 3D wafer level packaging

– Relatively large vias on a coarse pitch added at wafer level

– Usually for peripheral connections

– Backside contact allows stacking of chips or adding a sensor on top

– Low cost– Small package

• 3D Silicon Interposers (2.5D)– Built on blank silicon wafers– Provides pitch bridge

between IC and substrate– Can integrate passives

• 3D Integrated circuits– Small vias added at wafer

level permit internal chip connections between tiers

– Opens door to multilevel high density vertical integration

– Reduces interconnect paths between circuit elements

Vertex 2010 3

3D Wafer level package

3D Silicon interposer

MIT LL 3D integrated APD Pixel Circuit 8

22um

TIPP 2011, Chicago 4

Through Silicon Via History• Not a new concept. In 1975, a

GaAs IC used a TSV for backside grounding.

• More than 10 years ago backside illuminated CCDs were fabricated by thinning the CCD and opening a long trench behind the normal bond pads to allow wire bonding from the back side of the die.

• In 2005 the technology was applied in HEP to a MAPS device wherein separate openings were made behind each bond pad to allow for wire bonding from the backside and thus allow backside illumination (BSI). 7

• The above examples are similar to WLP.

• Will now examine more recent effort in HEP to use TSVs to develop true 3D integrated circuits.

Add

Remove

5TIPP 2011, Chicago

MIT LL 3D MPW Run Experience

Step 1: Fabricate individual SOI tiers (FEOL + BEOL)

Note: Wafer 1 can be SOI or bulk

Step 2: invert, align, and bond wafer 2 to wafer 1using an oxide bond

Step 3: remove handle silicon from wafer 2, etch vias, deposit and CMP tungsten. (The BOX acts as an etch stop when removing the handlesilicon.)

Note: additional tiers can be stacked by using a face to back configuration on top of wafer 2

• Fermilab made two submissions to MIT LL of a 3 tier device for an ILC pixel detector.

• The first in 2006 had processing and some design issues resulting in poor yield and took 13 months to fabricate.

• The second iteration in 2008 used a conservative design approach which yielded much better results but still took 20 months to fabricate

• MIT LL uses a via last process on their SOI wafers

• Space must be left on all metal layers for via insertion

• An oxide bond is used to mate wafers as shown here.

Oxidebond

3D via

TIPP 2011, Chicago 6

Tezzaron 3D MPW Run Experience

Vertex 2010 6

Assume identical wafers

Flip 2nd wafer ontop of second wafer

Bond 2nd wafer to 1st

wafer using Cu-Cuthermocompression bond

Thin 2nd wafer to about 12um to expose super via

Add metallizationto back of 2nd waferfor bump or wirebond

After FEOLfabricate6 um supercontact (via)

CompleteBEOL processing 12 um

Additional waferscan be stacked face to back on top of 2nd wafer

TSV

6um

Cu-Cubond

• In late 2008, consortium of 15 institutions formed to fabricated 3D integrated circuits using the Tezzaron/Chartered process.– Chartered uses a via middle

process to add vias to 130nm CMOS process

– Tezzaron performs 3D stacking using Cu-Cu thermo compression bonding

TIPP 2011, Chicago 7

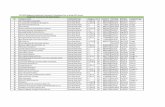

Tezzaron MPW Run Frame• Design approach

– Two tiers with a single mask set– Top tiers on left side and bottom

tiers on right side of frame

• More than 25 two tier designs (circuits and test devices)– ATLAS pixels– CMS strip ROIC for track trigger– X-ray imaging– B-factory and Linear Collider

pixels– Test circuits

Vertex 2010 7

Frame shows symmetry about center line

H H*

I I*J J*

Fermilab designs:H: VICTR – pixel readout chip mating to twosensors for track trigger in CMSI: VIP2b – ILC pixel chip with time stamping and sparcificationJ: VIPIC – fast frame readout chip for X-ray Photon Correlation Spectroscopy at a light sourceTX and TY – test chips

TX TX*TY TY*

MPW run frame showing top tiers on the left and bottom tiers onthe right

Waf er Map

TX1 TX2TY1 TY2

A1 B1 B2 A2

C1 D1 D2 C2

E1 F1 F2 F2

G1 H1 H2 G2

J 1 K1 K2 J 2

Frame layout

TX 1 T X 2T Y1 T Y 2

A1 B1 B2 A2

C1 D1 D2 C2

E1 F 1 F 2 F 2

G1 H 1 H 2 G2

J 1 K 1 K 2 J 2

Max f rame layout area includinginternal saw streets: x=25.760 mmy=30.260 mm.

Note symmetrical placement of frameson wafer

TIPP 2011, Chicago 8

Design and Submission Problems• Some Design Problems

– All designers did not use the same design kit leading to several problems such as layer map in consistencies.

– Some TSV design rules were interpreted incorrectly.

– Manual fill on designs had to be redone with fill program.

– Bugs found in MicroMagic software used to assemble the fame for 3D submission created errors.

• Some Submission problems– Chartered requested extra

frame space after the frame was completed requiring multiple frame revisions.

– Design labels outside the design area had to be moved into design area or be removed.

– Masks for frame sections were incorrectly mirrored at mask house.

– Most error waivers were unacceptable by Chartered

– Some designs were submitted with incorrect mirroring

TIPP 2011, Chicago 9

Fabrication Problems• 3D wafer fabrication done in

Chartered prototype line• Chartered was bought by

Global Foundries which slowed our wafer fabrication process– Personnel knowledgeable in 3D

fab issues were moved– Some equipment use for 3D fab

moved to higher profit production line

• Global/Chartered did not properly place frames on wafers for 4 different lots of wafers being processed for Tezzaron. The wafers could not be aligned properly for 3D bonding.– Never happened before

• These wafers however could be used for some 2D IC testing as discussed later.

Frames are not placed symmetrically about the wafer center lines

1.2 mm misalignment

TIPP 2011, Chicago 10

Fabrication Problems

• A new lot of 31 wafers was fabricated at no cost to Tezzaron or us except for time (3 months)

• Due to delays in fabrication, the 3D wafer bonding facilities were not available when the second batch of wafers were ready.

• The wafers have 400 nm of protective nitride which must be removed from the surface before bonding at about 240 lb/in2 and 400 degrees C.

Newly fabricated wafer with properframe placement on the wafer

TIPP 2011, Chicago 11

Assembly Problems• After the nitride removal, 3 wafer

pairs were bonded but all 3 had large unbonded areas in the center of the wafer making thinning impossible.

• One bonded pair was broken and a SEM image taken showing a residue 3-7 nm on the wafer surface.

• A Auger electron microscope showed the residue to be carbon

• The remaining unbonded wafers used CMP to remove the carbon.

• The unbonded wafers were then sent for bonding

• At this point 3 bonded wafers pairs are being thinned in Singapore

• Back side metalization follows the thinning process to complete the 3D assembly.

carbon

12TIPP 2011, Chicago

Tests Performed on Global/Chartered Parts

• Unfortunately 3D circuits and test structures are still not available.

• Fortunately some circuits have been fabricated in 2D for testing and some 3D wafers had pads added so testing could be done of individual tiers on our misaligned 2D wafers.

• All circuits tested by various collaborators in 2D have been found to performed as expected with no deleterious effects due to the TSVs.

TIPP 2011, Chicago 13

• VIP2a design for ILC pixels is separated into separate digital and analog tiers.

• Circuits on analog tier could be tested independently.

• Functionality of each block of analog circuit was verified.

• Good linearity and range• Process findings

– NMOS thresholds ~ 100 mv lower than simulations

– NMOS gm a few % lower than simulations

– PMOS gm 10-15% lower than simulations

– MiM caps ~4% lower than expected

– Noise @ 75 ns time constant is equal to 8e + 0.5e/fF* Cin

Tests on Fermilab Circuits

TIPP 2011, Chicago 14

• Idea for track trigger is to discriminate on tracks with high pt

• Compare hits locally on two closely spaced strip sensors.

• Very aggressive use of 3D technologies.

• One tier processes signals from top tier

• Other tier processes hits from bottom tier, accepts hit information from top tier, performs comparison and transmits data off detector.

• Functionality of short strip tier has been proven on 2D chip– Downloading of registers– Control of front end bias– Front end response– Backend readout– DAQ system– Strip Vth sigma = 197e– Noise mean= 75e, sigma= 13e

Tests on VIPIC for CMS Track TriggerLongstrips

Shortstrips

Short strip readout tier

Two rings of strip sensorsshown with bent track

TIPP 2011, Chicago 15

Device Testing• Radiation tests

– Tests performed by CPPM– ELT devices and core linear

devices with TSVs tested at CERN’s X-ray test lab• Linear PMOS and ELT

NMOS and PMOS show insignificant rad effects.

• NMOS leakage current shows peak around 1 Mrad which is similar to other 130 nm processes tested by CERN.

• The main difference observed is that the Chartered NMOS Vt shift is positive rather than negative as seen in other processes tested by CERN

• NMOS and PMOS Vt shifts are acceptable

• Cryogenic tests– Fermilab is interested in

designing CMOS cryo electronics

– The main problem reported in the literature is that Hot Carrier Effects cause lifetime degradation and operating voltage derating is one means of correcting the problem.

– Stress tests were performed on minimum size Chartered 130 nm devices.

– Preliminary results indicate that the Chartered transistors will not require any voltage derating whatsoever to achieve a lifetime greater than 20 years.

16TIPP 2011, Chicago

Commercial Silicon Brokers Move Toward 3D Circuits using

Chartered/Tezzaron• Partnership announced for 3D circuit fabrication

– CMP will provide and maintain 3D/Chartered design kit– CMC and CMP will accept designs and send them to MOSIS for

interfacing with Tezzaron– Tezzaron will handle NDAs and submission of designs to

Global/Chartered– 3D assembly will be done by Tezzaron– Parts will be distributed by MOSIS

TIPP 2011, Chicago 17

• A comprehensive design kit has been assembled by CMP.

• Tools included for– Cadence

• Cadence data base• Open access• Encounter for 3D

– Calibre– Hercules– Mentor (Eldo, HSPICE)– Micromagic– ARM libraries including

physicals

• Numerous programs and libraries provided by HEP Consortium

• Monte Carlo models• Automatic fill program• User set up files• Two packages are

available– Design kit with ARM

libraries– Design kit without ARM

libraries

Design Kit Features

18TIPP 2011, Chicago

Future• Tezzaron working to improve process flow by

moving all steps except TSVs to NC• Tezzaron moving toward using wafers from other

foundries and inserting TSVs at SVTC• Tezzaron TSV process has been installed at

Honeywell on SOI process• Tezzaron and IBM are having discussions about

running 65 nm with TSVs at IBM • MOSIS is planning to have two 3D runs this year.

– A run in Sept 2011 is scheduled for non-HEP customers

– Another run is scheduled for HEP designs a few months after the first run chips have been tested.

19TIPP 2011, Chicago

Summary• Through silicon Vias have begun to receive

significant attention not only in industry but now in HEP. Wafer level packaging using TSVs is being investigated for current HEP projects and silicon interposers are being investigated for future projects. Perhaps the most dramatic change is the use of TSVs to design multi-tier 3D integrated circuits for HEP. The efforts of the 3D design consortium when successful will open the door for a new wave of detector circuits which will surely revolutionize some approaches to detector design.