Stp02 3 Three Phase Motor Controller ICs

-

Upload

bogdan-costea -

Category

Documents

-

view

15 -

download

0

description

Transcript of Stp02 3 Three Phase Motor Controller ICs

-

STP02-3-AN

Product DescriptionThree-Phase Motor Controller IC Drives External FETs

for PWM Current Control, Synchronous Rectification, and100% Duty-Cycle Capability

By Peter MorrisAllegro MicroSystems, LLC

ABSTRACTThe increasing use of high-current brushless dc (BLDC)three-phase motors puts stringent requirements on thedrive electronics for function and safety. A new three-phase motor controller has integrated all the circuitry tocontrol the six power NMOS FETs for fractional horse-power motors up to 50 V. The basic techniques of fixedoff-time PWM current control and bootstrapped high-sidegate drives are enhanced by adding synchronous rectifica-tion control, cross-conduction protection and on-chipcharge pumps to allow 100% PWM duty cycles. Safetyfeatures and diagnostic output prevent inappropriateswitching of the power FETs and allow programmablemotor spin-down on power loss.This paper presents the system concepts and describes thecircuit implementation of several key features.

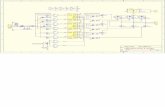

FUNCTIONAL DESCRIPTIONArchitecture overviewThe block diagram of the A3932 chip (figure 1) shows allthe main functions. Being a three-phase driver, there arethree half-bridge drive circuits (one only shown in thediagram). Each phase has a high and low side drive circuitproviding the push-pull control to charge and dischargethe external FET gates. The low side gate driver simplyruns off the regulated voltage VREG (13 V with respect toground), while the high side driver circuit supply isbootstrapped up above the motor supply Vbb (Cx is about12 V with respect to the Sx terminal, see below).It is common practice to add resistors in series with thegates when driving high current FETs in motor drivecircuits, to reduce slew rates and hence noise, couplingand emission problems. Since this technique increasesturn-on and off times there is a danger that both FETs in aphase could be partially on at the same time during statechanges. To prevent the resulting high shoot-throughcurrents the design provides a turn-on delay circuit, which

stops either driver turning on until the other has beenturned off for a fixed time (the deadtime), set by anexternal resistor on the DEAD terminal. It is up to the userto ensure that this time is sufficient. Directly sensing thegate voltages would allow an automatic cross-over protec-tion scheme to be implemented, but this would add 6terminals to the chip. It is also not generally preferred bydesigners, the deadtime scheme giving more flexibility forsystem design.PWM current control is achieved by chopping the high-side FET (which also guarantees frequent refresh of thebootstrap capacitor during normal operation). A fixed off-time control scheme is implemented the user setting thescale (external sense resistor in the bridges ground return)and the timing (parallel resistor/capacitor on the RCterminal). This fixed off-time function can be used as themain current-control loop or as an upper current limit withthe PWM terminal duty cycle providing the main control.To prevent false tripping by reverse recovery spikes, useradjustable leading edge blanking is integral with thisscheme.Correct commutation of the three half-bridges requiresaccurate rotor position information. A standard way ofdoing this is via three hall-effect sensors placed at 120electrical degree intervals, their logic outputs being fed tothe Hx inputs. Any scheme that provides a clear logic-level signal (such as angular position sensors or back-emf(bemf) detection) can also be used.The control logic block takes the commutation informa-tion and the fixed off-time signal, together with other usercontrolled input (PWM, DIR, MODE, SR, BRAKE &RESET), so as to provide the appropriate logic states toall six outputs as shown in the state tables in figure 2.Standard control functions of direction (DIR), pulse-width-modulation of the active high-side driver (PWM),RESET and BRAKE, are complemented by more ad-vanced features MODE and SR.

-

STP02-3-AN2

Figure 1 A3932 block diagram (only one phase of three shown)

Figure 2a Commutation truth table

H1 H2 H3 DIR GLA GLB GLC GHA GHB GHC SA SB SC1 0 1 1 0 0 1 1 0 0 HI Z LO1 0 0 1 0 0 1 0 1 0 Z HI LO1 1 0 1 1 0 0 0 1 0 LO HI Z0 1 0 1 1 0 0 0 0 1 LO Z HI0 1 1 1 0 1 0 0 0 1 Z LO HI0 0 1 1 0 1 0 1 0 0 HI LO Z1 0 1 0 1 0 0 0 0 1 LO Z HI1 0 0 0 0 1 0 0 0 1 Z LO HI1 1 0 0 0 1 0 1 0 0 HI LO Z0 1 0 0 0 0 1 1 0 0 HI Z LO0 1 1 0 0 0 1 0 1 0 Z HI LO0 0 1 0 1 0 0 0 1 0 LO HI Z

-

STP02-3-AN3

Figure 2b Current control state logic

BRAKE MODE PWM SR RESET Quadrant Mode of operation0 0 0 0 0 Fast decay PWM chop current decay, all drivers OFF0 0 1 0 0 Fast decay Peak current limit, selected drivers ON0 1 0 0 0 Slow decay PWM chop current decay, selected low-side drivers ON0 1 1 0 0 Slow decay Peak current limit, selected drivers ON0 0 0 1 0 Fast decay PWM chop current decay with opposite drivers ON0 0 1 1 0 Fast decay Peak current limit, selected drivers ON0 1 0 1 0 Slow decay PWM chop current decay with both low-side drivers ON0 1 1 1 0 Slow decay Peak current limit, selected drivers ONX X X X 1 N/A All gate outputs to 0 V clear fault logic1 X X X 0 N/A Brake all low-side drivers ON, all high-side drivers OFF

The MODE terminal allows the selection of slow or fastdecay modes, which defines the load current recirculationpath during the off-time (see figure 3) allowing the userflexibility to profile the load current waveform. Duringslow decay the high-side driver only is turned off and thecurrent recirculates through the same phases low side.During fast decay the same thing happens but in additionthe low-side driver is turned off so the current also recir-culates through its partner high-side FET.The SR input allows selection of synchronous rectifica-tion, which turns on the appropriate low- or high-sidedriver during recirculation shorting out the reversed bodydiode and hence reducing dissipation in the power FETs.The body diodes will still be conducting for the durationof the deadtime.It is crucial for these types of high-current applications tohave protection circuits to prevent inappropriate FETdrive signals, as well as general circuit protection. Theseare covered in a later section.The process chosen for this device is Allegro ABCD3process (Allegro, Bipolar, CMOS, DMOS, 3rd generation).Merging analogue bipolar/CMOS, low-voltage CMOSlogic and power DMOS transistors, ABCD3 features 65 Vvertical power DMOS as well as 12, 35, and 65 V lateralDMOS transistors. In addition, it provides several fea-tures that allow an efficient die size to be achieved forthis design, such as the twin buried layers (see nextsection). One complication is that the maximum on-chipgate-source voltage is restricted to 10 V, so the design ofseveral circuit blocks requires care to ensure no gates are

overstressed ABCD3 again helps, as there are suitableZener-diode structures available for gate clamping.The device is assembled into a standard low-cost 32-leadPLCC package.Gate driversThe requirements of the gate drive circuitry (especiallythe high-side driver) are very demanding:

Provide an absolute minimum gate drive of 10 V forefficient power FET selection.Minimal static current consumption from the bootstrappedsupply this governs the size of the top-up charge pump(see next section).Operate from a 50 V motor supply (VBB), which means upto 65 V maximum on the bootstrapped supply nodes.Keep propagation delays low target 100-200 nsCapable of driving 100 nC and higher FET gate charge.

Of course all of these requirements plus the other neces-sary circuit functions, must be integrated for as low a costas possible hence silicon area is at a premium.The circuit technique for the high-side driver circuit isshown simplified in figure 4. The bootstrapped supplyVcs is created by Cboot being charged from the 13 VVreg supply through diode d1 while the low-side powerFET is on. Normally, during PWM operation (synchro-nous rectification ON and in slow decay mode) Cboot willcharge up to:

Vcs = Vreg Vfwd(d1) + Vds(low-side)

-

STP02-3-AN4

Vds should be low, to keep power FET losses to a minimum.Operating with synchronous rectification OFF will changethe Vds term to the drain-bulk diode forward drop, whilechanging the mode to fast decay will add in Vsense (voltagedrop across the sense resistor) figure 3 may help to explain

this. Care should also be taken in the board layout toensure that the SENSE node (sources of the low-sidedriver) does not show excessive negative transients dueto stray inductance, as this could potentially lead toVcs getting too high. As will become apparent, the

Figure 3 Driver modes and current paths

-

STP02-3-AN5

design approach adopted does allow for correct and safeoperation even with several volts negative on this node.The above explanation applies once the phase drive hassettled into PWM cycling initial turn on of a particularphases high-side may see Cboot charged to a lower level,due to the current being in the opposite direction in thelow-side driver :

Vcs = Vreg Vfwd(d1) Vds VsenseAs this will only occur for one or two cycles the slight lossof efficient drive is negligible. It is also likely that Cbootstill retains its charge level from the previous phaseactivation.The gate of the external high-side FET is push-pull driventhrough terminal GH by transistors m1 and m2, which aresized for adequate drive levels (rdson of 14 for thepmos and 4 for the nmos). To turn the high-side powerFET on, m2 is driven on by current sink Ih2 fed throughcascode transistor m7. Similarly, the high-side powerFET is turned off by current sink Il2 fed through cascodem9, mirrored and fed into m1 gate, turning it on. As m1and m2 are high gm devices and we must keep parasiticcharge depletion of Cboot to a minimum, m1 and m2 mustbe prevented from being on at the same time during

transitions. To do this, the extra current sinks Ih1 and Il2are switched in. For example, to turn on the high side (m2on), Ih1 starts to discharge m1s gate, but until this falls toa Vt m3 and m4 remain on holding off the gate of m2 once m3 turns off, m4 turns off and m2 can start to turnon, driven by Ih2. Similarly for turn-off, m5 prevents Il2from turning on m1 until m2 has virtually gone off. Ih1and Il2 could have been derived from mirrors up at thebootstrap supply, but this would have added some extraconsumption from Vcp and would have slowed down thetransition time as the turn-off signal would have takenlonger to propagate to the output.This technique was chosen over the pulsed high-side latchmethod (ref 2) for two reasons:

To ensure a steady-state drive in case of noise tran-sients that might cause loss of correct state.Maximum Vgs limitation makes gate clampingmandatory, so some current limiting (and hencecurrent consumption) is required leading naturally toa current-driven approach.

To keep current consumption from the bootstrappedsupply to a minimum when the high-side driver is on, thecurrent sinks are pulsed at 0.5 mA for 1 s to allow

Figure 4 High-side gate driver circuit

-

STP02-3-AN6

sufficient time for all nodes to settle before falling back toa 2 A retention level. This gives a total static currentconsumption of about 10 A from the Cboot. The actualpulse time is made proportional to the user selected deadtime, so can vary from around 0.3 to 4 s this providesslightly better matched drive duration.The last, but by no means trivial, advantage of the boot-strap technique is in silicon area. Because most of thecircuitry is floating across Vcs (

-

STP02-3-AN7

Figure 6 Top-up charge pump

The method chosen for this chip is an internal low-currenttop-up charge pump that is active when the high-side FETis turned on (figure 6). In clock cycle Cb the pumpcapacitor C1 is charged to 12 V with respect to Vbb, setby the switched current sink I1 into R2 and clamped byQ1. In clock cycle C switches S1 and S2 are opened andS3 closed this pulls the bottom end of the capacitor toVbb, reverse biases D1 and forward biases D2 passingcharge to GH through M2. Regulating in the charge cyclehas the advantage of avoiding having to sense the voltageon the charge pump output (which can be as high as 62 Vnominal) and level shift a control signal back down; whilepumping relative to Vbb avoids large and variable voltageswings on m1s drain and hence loss of charge due toparasitic capacitances on this node.The presence of M2, 3, 4, and DZ1 is to allow the outputto go below ground as happens during output flyback.Due to the high-voltage operation of the charge pump, thepump diode D2 has a parasitic diode to substrate on itscathode, so this node cannot be allowed to go belowground. Once the output and D2 cathode have droppedbelow Vbb, then M2 is switched off as its Vgs is negative.DZ1 clamps D2s cathode two diodes below Vdd and alsoprevents negative transients to M2s gate. M3 and M4ensure that during a normal pumping cycle there is no

appreciable current leakage through DZ1 to Vbb wouldnot turn on until Vz + 2Vthp (app. 12.5 V).The charge-pump circuit is driven by a 1.8 MHz on-chipclock.ProtectionA feature of this chip design is to implement a fairlyrigorous set of protection features to ensure that undervirtually any circumstance the FET drivers can be pro-tected from fault conditions, poor set-up (e.g., deadtimetoo short) and situations that might limit the gate drive insome way, leading to excessive system power dissipation.Outputs are disabled in the event of:

VREGuvlo (undervoltage lockout) if the 13 Vregulated output falls below 9.1 V.Invalid Hall state only six of the possible eight Hallstates are valid positions all 0s or all 1s are faults.

-

STP02-3-AN8

Die temperature > 165C outputs disabled until dietemperature cools 15C then re-enable.A short-to-ground on any phase node detected if theS node does not get within 2 V of Vbb when the high-side driver is turned on. This comparator is disableduntil the high-side driver goes into its low current drivestate, to prevent false tripping as the drive settles. Thisfault is cleared at each phase commutation to allowlimited operation even with one phase dead however,if the fault causes the motor to stop before a commuta-tion change then a system reset will be required to clearthe fault.Note that short to supply faults are effectively dealtwith by the main current-control loop.Inadequate charging of Cboot see below.

Ensuring that the bootstrap procedure is carried out correctlyis one of the trickier protection features implemented.Monitoring the voltage across Cboot during charging andduring use might be seen as ideal (ref 1), however a circuitimplementation compatible with all the other operatingrequirements is non-trivial especially the very low currentconsumption required while the high side is on. So a three-way approach was adopted:i. During Cboot charging the charge current is monitored

as the bootstrap charge path is about 9 , Cboot is notconsidered to be charged until this current has droppedto around 9 mA. This means it will be guaranteed to becharged to about 100 mV from the maximum.

ii. The bottom end of Cboot (i.e., the S node) is monitoredto ensure it is less than 1 V from ground.

iii. Time-out if conditions i and ii above are not metwithin 60 s then there must be a fault preventing Cbootfrom charging, so to prevent excessive power dissipationand/or VREG failure, the Cboot charging path is discon-nected. Reset or commutation is required to clear this.

The combination of the above conditions (plus theVREGuvlo) ensures that the high side is only turned on ifCboot is fully charged if not the phase is disabled andmade safe. The only lack of direct protection in this schemeis the lack of monitor of the high-side gate drive voltage however, this is covered indirectly by the short-to-grounddetector. If the FET starts to lose gate drive its Vds will

increase and be detected by the high-side short-to-ground monitor (in this case maybe it should havebeen called a not-shorted-to-Vbb monitor!).Of course it would be easy to dream up fault scenariosthat would damage any IC, but the target with thisdesign was to cover the likely faults that could occur inreal applications. For example, there are no directcurrent limits on the gate-driver outputs (GLx andGHx), but in a real application these nodes would havesome series gate resistance and would not go off-board, so a direct short is unlikely. In the event of apower FET becoming damaged and causing a gate shortthen one of the other protection functions may wellcome into play. In addition there are other morestandard protection features not mentioned so far such as current limits on both VREG and the 5 V logicoutput LCAP.Power loss brake/coastThere are two versions of this chip so far the abovedescriptions have been applicable to both, but the A3938version has an extra function added to allow controlledmotor operation during a power-loss event. In some motorapplications (such as reel to reel tape drives) it is impor-tant to control the operation of the motor as power is beingremoved. For example, in a tape drive application onereel should brake and the other coast, to ensure the tapedoes not run off the reel or snap.The default system operation during power loss (detectedby the VREGuvlo) is to coast the motor i.e., turn off alldrivers. The alternative is dynamic braking where allthree phase windings are shorted (to ground in this case)by turning on all three low-side drivers. The extra circuitblock provides a means to remember the required power-down state and drive the low-side power FETs appropri-ately, even when the Vbb and VREG supplies havedisappeared.Figure 7 shows the concept. A user-selected capacitor onBRKCAP is charged through an internal diode D1 toVREG during normal operation. The required power-down state is applied to the BRKSEL terminal this canbe dynamically changed during normal operation but thestate is latched on the VREGuvlo falling edge (i.e., onpower loss being detected). Output from this block isinhibited during normal operation by the same signal.

-

STP02-3-AN9

Figure 7 Power-loss brake

Figure 8 A3932 die layout

Once power is lost, the falling VREG voltage will reversebias the diode leaving the BRKCAP capacitor to providepower. If a brake mode was selected (BRKSEL = 1) thenthe D flip-flop clocks a 1 to its output, turning on Q1 anddriving directly the three GLx to turn on the externalFETs. D2-4 are required to block interactions betweenoutputs in normal operation. Also, each output-stagedriver circuit has a blocking diode added to its pmos pull-up drive, to prevent the parasitic drain-bulk diode fromforward biasing and shunting the brake drive current intothe VREG capacitor and VBB. Once the gates have beencharged up there will be effectively zero output current,so the only current discharging the BRKCAP capacitorwill be this blocks static consumption, which is kept low(a 4.7 F capacitor will provide > 6.5 V gate drive for300 ms).If a coast mode was selected then obviously the D flip-floplatches a 0 on its output, holding off the gate drives, allowingthe normal power-down circuitry to operate.

-

STP02-3-AN10

CONCLUSIONA new three-phase motor controller design, the A3932 hasbeen described (die layout shown in figure 8), with keycircuit features highlighted. Some of the trade-offs oftenmade in IC design to balance function, die size/packageand process design constraints/opportunities have beendiscussed also.The market for high-power 3-phase BLDC motors contin-ues to expand, pushing the further development of thepresented techniques. Higher operating voltages and gate-drive capabilities, as well as better diagnostic capabilitiesfor safety-critical applications, will fuel the push tosmaller geometries and smarter processes and designtechniques.

REFERENCES1. Allegro MicroSystems LLC A3933 datasheet.2. High-voltage integrated circuits for off-line power

applications by C. Diazzi (chapter 8 of Smart PowerApplications B. Murari, F. Bertotti & G. A Vignola(Eds) Springer 1996.

-

STP02-3-AN11

Copyright held by Primedia Business Exhibitions, a Division of Primedia Business Magazines & Media. Originally published in the Power Elec-tronics Technology 2002 Proceedings for the Power Systems World Conference held in Rosemont, IL, October 29, 2002. Reprinted by permission.

Portions not copyrighted by Primedia, Copyright 2002-2013, Allegro MicroSystems, LLC.

The information contained in this document does not constitute any representation, warranty, assurance, guaranty, or inducement by Allegro to the customer with respect to the subject matter of this document. The information being provided does not guarantee that a process based on this infor-mation will be reliable, or that Allegro has explored all of the possible failure modes. It is the customers responsibility to do sufficient qualification testing of the final product to insure that it is reliable and meets all design requirements.

For the latest version of this document, visit our website:www.allegromicro.com