Project RNG: Radiation-Based Random Number Generator

description

Transcript of Project RNG: Radiation-Based Random Number Generator

Senior Design

1

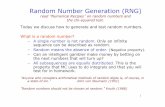

Project RNG: Radiation-BasedRandom Number Generator

• Team Oregon Chub– Ashley Donahoo– Colton Hamm– Alex Brotherston– Matt Johnson

University of Portland School of Engineering

Advisor:Dr. VanDeGrift, Dr. Hoffbeck,

Dr. Osterberg

Industry Representative:Mr. John Haner

Bonneville Power Administration

Senior Design

2

Introduction

• Our project generates random numbers from radioactivity

• Building a radiation sensor, designing a MOSIS chip and using 7-segment displays

University of Portland School of Engineering

Senior Design

3

Scorecard

• Received all ordered parts for analog circuitry.

• Successfully used .abl file to burn-in the CPLD macromodel.

University of Portland School of Engineering

Senior Design

4

Additional Accomplishments

• Completed LabVIEW tutorial

• Received BCD-to-7-segment decoders and 7-segment displays from Craig Henry.

University of Portland School of Engineering

Senior Design

5

Plans• Completely test and verify CPLD

functionality.

• Completely test and verify 7-segment display and decoder functionality.

• Meet with Allen about case design.

University of Portland School of Engineering

Senior Design

6University of Portland School of Engineering

MilestonesStatus Description Original

TargetPreviousTarget

PresentTarget

Completed Submit final .edf file 19 Nov 10 19 Nov 10 21 Nov 10

Completed Design Document v0.95 19 Nov 10 19 Nov 10 19 Nov 10

Completed Simulate pulse generator, transformer, voltage multiplier, and load interfacing in PSPICE

30 Nov 10 30 Nov 10 30 Nov 10

Completed Design Document 1.0 3 Dec 10 3 Dec 10 30 Nov 10

Completed Use .abl file to create CPLD macro model

10 Dec 10 10 Dec 10 10 Dec 10

Completed Analog parts ordered 17 Dec 10 17 Dec 10 17 Dec 10

Completed Construct and test pulse generator/transformer

31 Jan 11 31 Jan 11 23 Jan 11

On track Verify CPLD functionality 6 Feb 11 6 Feb 11 6 Feb 11

On track Verify 7-seg display and decoder functionality

6 Feb 11 6 Feb 11 6 Feb 11

On track Construct and test the prototype voltage multiplier.

14 Feb 11 14 Feb 11 14 Feb 11

On track Construct final voltage multiplier

21 Feb 11 21 Feb 11 21 Feb 11

Senior Design

7

Concerns/Issues

• Inexperience with CPLD’s, 555 timers, 7-segment displays and decoders could lead to delays

• Concerned about how much time LabVIEW will take to set up

• Various interfacing issues

University of Portland School of Engineering

Senior Design

8

Conclusions• CPLD has been created and is ready for

testing before implementation into analog circuitry.

• We are now focused on the analog portion and having it interface with the Geiger tube.

University of Portland School of Engineering

Senior Design

9

Questions?

University of Portland School of Engineering