Directions - INSILVISeGREGE formae DIRECTIONS DIRECTIONS 2 MADE IN ITALY

Progress and Planned Future Directions in Optical ...Progress and Planned Future Directions in...

Transcript of Progress and Planned Future Directions in Optical ...Progress and Planned Future Directions in...

Progress and Planned Future Directions in Optical Processing and

Communications

DARPA/MTO Microsystems Technology Symposium

Daniel J. BlumenthalDept. of ECE

University of California at Santa BarbaraSanta Barbara, CA 93106

LASOR research supported under DARPA/MTO DoD-N Program Award Number W911NF-04-9-0001CSWDM research supported under DARPA/MTO Program Award Number

Report Documentation Page Form ApprovedOMB No. 0704-0188

Public reporting burden for the collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering andmaintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information,including suggestions for reducing this burden, to Washington Headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, ArlingtonVA 22202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to a penalty for failing to comply with a collection of information if itdoes not display a currently valid OMB control number.

1. REPORT DATE 05 MAR 2007

2. REPORT TYPE N/A

3. DATES COVERED -

4. TITLE AND SUBTITLE Progress and Planned Future Directions in Optical Processing and Communications

5a. CONTRACT NUMBER

5b. GRANT NUMBER

5c. PROGRAM ELEMENT NUMBER

6. AUTHOR(S) 5d. PROJECT NUMBER

5e. TASK NUMBER

5f. WORK UNIT NUMBER

7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES) University of California at Santa BarbaraSanta Barbara, CA 93106

8. PERFORMING ORGANIZATIONREPORT NUMBER

9. SPONSORING/MONITORING AGENCY NAME(S) AND ADDRESS(ES) 10. SPONSOR/MONITOR’S ACRONYM(S)

11. SPONSOR/MONITOR’S REPORT NUMBER(S)

12. DISTRIBUTION/AVAILABILITY STATEMENT Approved for public release, distribution unlimited

13. SUPPLEMENTARY NOTES DARPA Microsystems Technology Symposium held in San Jose, California on March 5-7, 2007.Presentations, The original document contains color images.

14. ABSTRACT

15. SUBJECT TERMS

16. SECURITY CLASSIFICATION OF: 17. LIMITATION OF ABSTRACT

UU

18. NUMBEROF PAGES

40

19a. NAME OFRESPONSIBLE PERSON

a. REPORT unclassified

b. ABSTRACT unclassified

c. THIS PAGE unclassified

Standard Form 298 (Rev. 8-98) Prescribed by ANSI Std Z39-18

DARPA MTO Symposium, March 4-6, 2007 2

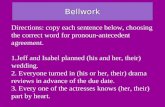

Technology Push and Integration Trends

101

103

105

107

109

1011

1013

1015

1940 1950 1960 1970 1980 1990 2000 2010

Intel 8080Eniac

Cray 1

Cray 2Cray X-MP

CDC6600

IBM 704

NEC earth simulator

IBM ASCI white

Intel 80286

MotorolaPowerPC 604

Intel Dual

IntelP4

AMD XP

Optiputer

Photonics for chip-to-chip multiprocessor

Supercomputers on-chip Distributed Systems

a

a

b

c

d

bc

d

Transistor

Million to Billion transistor integration

Multiprocessor chips

b

Heterojunction Laser, Optical Waveguides,Integrated & Silicon PhotonicsHeterojunction Laser, Fiber Optics, Integrated Photonics, Optical Networks

Cisco GSR

Cisco CRS-1 (92 Tbps - 40 Racks

Powerbook G5

e Vertical Magnetic Storage

e

Approximately every 10 years we see the results of basic technology research reduce systems from lab size to the desktop size. This trend

enables vast new applications that cannot be fully forecast.

Approximately every 10 years we see the results of basic technology research reduce systems from lab size to the desktop size. This trend

enables vast new applications that cannot be fully forecast.

DARPA MTO Symposium, March 4-6, 2007 3

Power and Size: The Next Frontier• Decreased transistor size, 2x transistors on chip every

18 months, increased frequency• Leakage current is huge problem, chips (hence

systems) become power constrained• New transistor technologies aim to decrease leakage

current but requires new processing infrastructure. Costly to roll over to new foundries from current.

• Moving to multi-processor cores to keep up performance without increasing speed

µPµP

µPµP µPµP

µPµP µPµP

linecard

linecard

Rack

Rack

µPµP µPµPµPµP µPµP

µPµP µPµPµPµP µPµP

µPµP µPµPµPµP µPµP

Multi-processor

Increased Performance

Pow

er S

prea

ding

Pro

blem

Communication Links

Source: Intel

DARPA MTO Symposium, March 4-6, 2007 4

Technical Contributors

CSWDMIntegrated Optical Wavelength Converters and Routers for Robust Wavelength-Agile Analog/ Digital Optical Networks

DoD-NLASOR: A Label Switched Optical Router

UCSB: M. Masanovic, V. Lal, J. Summers, H. -F Chou, E. Skogen, J. S. Barton M. Sysak, D. J. Blumenthal, J. E. Bowers, L. A. Coldren, N. Dagli, E. Hu

Cisco Systems: D. Civello, G. EppsJDSUniphase: C. Coldren, G. FishStanford University: N. Beheshti, Y. Ganjali, N. McKeownUCSB: B. Koch, M. Chun, L. Garza, M. Mashanovitch, J. Barton, T. Berg, J. Mack, H. Poulsen, S. Nicholes, E. Burmeister, H. Park, M. Dummer, A. Tauke-Pedretti, B. Stamenic, D. J. Blumenthal, J. E. Bowers, L. A. Coldren

DARPA MTO Symposium, March 4-6, 2007 5

CSWDM- Motivation and Applications

λ1 – λ32

λ1 – λ32

λ1 – λ32

λ1 – λ32λ5λ5

λ1

Working fiberProtection fiber

T-AOWC

Working fiber/lambda

Protection fiber/lambda

T-AOWC

T-AOWC

ROADM

Optical CrossconnectROADM

ROADM

ROADM

ROADM

ROADM

ROADM

ROADM

ROADM

ROADM

ROADM

Monolithically integrate widely tunable digital and analog wavelength conversion from any input λ to any output λMake tunable wavelength converters inexpensive to useEliminate off-chip high speed electrical for WC and regenerationAnalog operation to 20GHzIntegrate signal quality monitoringPush limits of on-chip component and function density

DARPA MTO Symposium, March 4-6, 2007 6C

ombi

ner

CS-WDM

λout1λin

1

λin2

λin32

Agile Wavelength Converter

Agile Wavelength Converter

Agile Wavelength Converter

DeM

ux

λτ1

λτ2

λτ32

λout2

λout32

12

32

1

2

32

3Wavelength

Router

Wavelength/Space Switch

λin1

λin2

λin32

Agile Wavelength Converter

Agile Wavelength Converter

Agile Wavelength Converter

Dem

ultiplexer

λτ1

λτ2

λτ32

Wavelength Interchanger

All-Optical Switching on-Chip for DoD Applications

DARPA MTO Symposium, March 4-6, 2007 7

0.5mm

7mm

λinput = λoutput

λinput ≠ λoutput

Back-to-Back

2-Stage Tunable Wavelength ConvertersJ. Summers, et. Al.

CS-WDM

DARPA MTO Symposium, March 4-6, 2007 8

All-Optical Push-Pull Wavelength Converters

0.6mm

7mm

TIR Mirror

Single Arm

Push-Pull

Increasing1st stage

probe power

Single Arm-large phase swing-poor noise (noise floor)

Push-Pull-full π phase swing-improved noise

Phase Measurements Eye Diagrams BERs

J. Summers, et. Al.

CS-WDM

DARPA MTO Symposium, March 4-6, 2007 9

Materials-Device-Function-System• 1st generation: Feb. ‘04

•Chip-on-carrier 2.5Gbs wavelength tunable all-optical wavelength converters sent to MIT-LL.

• 2nd generation: Aug. ‘05•Packaged 2.5Gbps T-AOWCs sent to MIT-LL.

• 3rd generation: Dec. ‘05 - Jan. ‘06• (4) x T-AOWCs packaged and integrated on control circuit boards installed on in-flight demo.

CS-WDM

DARPA MTO Symposium, March 4-6, 2007 10

Manipulating Light with Photonic Crystals

L=30µm

M. Davanço, A. Xing, J. Raring, E. L. Hu, and D.J. Blumenthal”“Broadband Photonic Crystal Passive Filters for Monolithically Integrated InP Photonic Integrated Circuits,” Submitted to OFC 2006.

100nm holes

But

terfl

y W

ings

-C

olor

+ C

oolin

g

Ultra-Short Optical Filters

CS-WDM

DARPA MTO Symposium, March 4-6, 2007 11

Were Does Integrated Photonics Fit into the Picture?

Today’s Technology

32/64 40G Inputs

32/64 40G Outputs

ORAM

OH Read

ERP

Line WC/

Regen

Optical Packet

Forwarding Engine

DARPA MTO DOD-N Program - LASOR (Haney, Shah)

UCSB: Blumenthal, Bowers, Coldren

Stanford: McKeown

Cisco

JDSU

Rack Rack

Process and switch photons around toreduce power

Integrate Photonic Functions onto a Chip to reduce size

Research in:• Physics• Materials• Devices and PICs• Processing• Architectures

Photonic Integrated Circuits (PICs) still at 1960s of Electronics

5 Tbps Linecard

DoD-N

DARPA MTO Symposium, March 4-6, 2007 12

LASOR Optical Packet Router Linecard

32 x 32(64 x 64) AWGR

32 x 32(64 x 64) AWGR

40GFTWC/OLE/OLW

40GFTWC/OLE/OLW

Sync/ ORAMSync/ ORAM

OLR/EPED

OLR/EPED

40G-3RTWCArray

40G-3RTWCArray

Optical LabelRecovery/

Payload EnvelopeDetect

Optical LabelRecovery/

Payload EnvelopeDetect

Electronic Routing ProcessorElectronic Routing Processor

Photons processed by PIC technology

PICs controlled by electronics

Pushing envelope on density and functionality of InP and Silicon Photonics

DARPA MTO Symposium, March 4-6, 2007 13

100 Tbps Optical Routing Node

Linecards connected to WDM transmission system and local ports via ROB

Optical express paths added to linecard

ISP traffic engineering applied to realize 100 Tbps capacity

Supports multiple architecturesMultistageDistributedBalanced

Support any ratio of express WDM traffic, optically packet routed traffic, and added/dropped traffic

Modular capacity growth of WDM on a link-by-link basis

Mux/D

eMux

Reconfigurable O

ptical Backplane (R

OB

)

1.28/2.56 TbpsODR Linecard

WDM Fiber Transmission System

40G Packet Add/Drop

1.28/2.56 TbpsODR Linecard

1.28/2.56 TbpsODR Linecard

40G WDM Line Add/Drop

DARPA MTO Symposium, March 4-6, 2007 14

Optically Buffered ODR

Synchronizer Synchronizer ORAMORAM

Local Reference Clock

PEDPED

Memory Read

Buffer Size

Delay Set

Memory Write

Optical Packet Forwarding

Optical Packet Forwarding

ORAMORAMPEDPED

Memory Read

Buffer Size

Delay Set

Memory Write

Output A Time Domain

Input A Time Domain

Input B Time Domain

Input B

Input A

Output B

Output A

Synchronizer Synchronizer

3R WC3R WC

3R WC3R WC

Optical Header Recovery and Payload Envelope Detect

32 x 32(64 x 64) AWGR

32 x 32(64 x 64) AWGR

40GFTWC/OLE/OLWArray

40GFTWC/OLE/OLWArray

Sync/ ORAMSync/

ORAMOLR/E

PEDOLR/E

PED

Basic Optical Data Router (ODR)

40GTWCArray

40GTWCArray

Optical L

abelR

ecovery/Payload E

nvelopeD

etect

Optical L

abelR

ecovery/Payload E

nvelopeD

etect Electronic Routing ProcessorElectronic Routing Processor

DARPA MTO Symposium, March 4-6, 2007 16

Payload Envelope Detection (PED)

DARPA MTO Symposium, March 4-6, 2007 17

Phase 1 Hybrid PEDHybrid Integrated Optoelectronic Payload Envelope Detection (PED) device

variable length PED signals generated3ns rise/fall time150 ps RMS jitter~7 dB input power dynamic rangeRemoved and inserted labels using this PED signal with <1dB power penalty

40Gbps payload input

PED output

16ns 8ns 32ns 16ns 8ns

Ref: Koch et al., OFC 2006, JLT, 2006, Optics Express, 2006.

DARPA MTO Symposium, March 4-6, 2007 18

Phase II - All-Optical PED

Ref: Koch et al., PTL, 2006, ECOC 2006.

Integrated all-optical PED: Compact, single component, low power consumption, Less expensive, low latency

DARPA MTO Symposium, March 4-6, 2007 19

All-Optical 3R Regeneration

Ref: Koch et al. OFC 2007Clock output

Clock output under different bias conditions

Data input

Clock Recovery with tunable output pulsewidth

ApproachIntegrated Mode Locked Lasers with optical gatesShort, transform limited pulsesVery high extinction ratiosHigh output powers possibleIntegrate MLLs with other components

GoalsPrecisely determine the repetition rateVery high quality pulse reshaping and re-timingintegrated all-optical 3R regenerator

40 GHz InP MLL

DARPA MTO Symposium, March 4-6, 2007 20

40Gbps Wavelength Converter Technology

32 x 32(64 x 64) AWGR

32 x 32(64 x 64) AWGR

40GFTWC/OLE/OLWArray

40GFTWC/OLE/OLWArray

Sync/ ORAMSync/

ORAMOLR/E

PEDOLR/E

PED

Basic Optical Data Router (ODR)

40GTWCArray

40GTWCArray

Optical L

abelR

ecovery/Payload E

nvelopeD

etect

Optical L

abelR

ecovery/Payload E

nvelopeD

etect Electronic Routing ProcessorElectronic Routing Processor

DARPA MTO Symposium, March 4-6, 2007 21

40Gbps Packet WC: Operating Principle

Input Pulse

SOA Carrier Density

CW signal phase

SGDBR signal power at Output

SOA1 SOA2

Switching window

DARPA MTO Symposium, March 4-6, 2007 22

Gen. 2 : Integrated Input Differential Delay

Chip Area = 2.5mm2

Chip Area = 3.8mm2

Gen. 1 : External Delay

Gen. 3 : Compact Integrated Balanced Delay

Chip Area = 2.4mm2

40Gbps Monolithic Widely-Tunable Differential Wavelength Converters

J. A. Summers, V. Lal, M. L. Mašanović, L. A. Coldren, and D. J. Blumenthal, "Widely-Tunable All-Optical Wavelength Converter Monolithically Integrated with a Total Internal Reflection Corner Mirror Delay Line for 40Gbps RZ Operation," Integrated Photonics Research and Applications (IPRA '05), Paper IMC5, San Diego, California, April 11-13, 2005.

V. Lal, M. L. Mašanović, J. A. Summers, L. A. Coldren, and D. J. Blumenthal, "40Gbps Operation of an Offset Quantum Well Active Region Based Widely Tunable All-Optical Wavelength Converter,“Optical Fiber Communication Conference, Anaheim, California, 2005.

V. Lal, J. A. Summers, M. L. Masanovic, L. A. Coldren, and D. J. Blumenthal, “Novel Compact InP-based Monolithic Widely Tunable Differential Mach-Zehnder Interferometer Wavelength Converter for 40Gbps Operation,”Indium Phosphide and Related Materials, Opto-I (IPRM '05), Glasgow, Scotland, May 8-12.

DARPA MTO Symposium, March 4-6, 2007 23

40G Tunable Wavelength Converters with Integrated DelayWorld’s First Monolithic Integrated 40G Tunable All-Optical WCOn-chip delay lines using TIR mirrors for RZ operationOptical preamplifiersOptical power splitters and combinersMach-Zehnder interferometer optical wavelength converterTunable laserLaser booster optical amplifier

MZI SOAsInput SOA

MZI PhaseSG-DBR Laser Booster SOAs

6.3mm

0.6m

m

MZI SOAs

Input SOAs

MZI Phase

SG-DBR Laser

λin

λout

Booster SOA

2.9mm

0.8m

m

λin

λout

Power Penalty 5dB

PRBS 27-1

1553 in 1541 out

1553 in 1541 out

DARPA MTO Symposium, March 4-6, 2007 24

Field-based Monolithic Wavelength Converters

Input 1548 nm Converted 1556 nm

Mach-Zehnder Electro-Absorption

10 Gb/s 20 Gb/s

Wavelength Converted EyesWavelength Converted EyesWavelength Conversion at 10 Gb/sWavelength Conversion at 10 Gb/s

Integrated RF interconnections and terminationsBandwidth greater than 20 GHz

Frequency response limited by QW detectorsA. Tauke-Pedretti, J. Barton, L. JohanssonM. Dummer, M. Sysak, J. Raring, L. Coldren

DARPA MTO Symposium, March 4-6, 2007 25

Packet Forwarding

32 x 32(64 x 64) AWGR

32 x 32(64 x 64) AWGR

40GFTWC/OLE/OLWArray

40GFTWC/OLE/OLWArray

Sync/ ORAMSync/

ORAMOLR/E

PEDOLR/E

PED

Basic Optical Data Router (ODR)

40GTWCArray

40GTWCArray

Optical L

abelR

ecovery/Payload E

nvelopeD

etect

Optical L

abelR

ecovery/Payload E

nvelopeD

etect Electronic Routing ProcessorElectronic Routing Processor

DARPA MTO Symposium, March 4-6, 2007 26

PFC Chip and Module

~10 ps Delay Line

Fast Tunable Laser

Signal Power Control SOAs

Pump Power Control SOA

Pump/Signal Combiners

XPM SOA ’s

Label Write Phase Shifter

MZ Phase

7 mm

0.75

mm

Signal Splitter

Chip Area = 5.25 mm2

“Monolithic Widely Tunable Optical Packet Forwarding Chip in InP for All-Optical Label Switching with 40 Gbps Payloads and 10 Gbps Labels,” V. Lal, M. Mašanović, D. Wolfson, G. Fish, C. Coldren, and D. J. Blumenthal, Accepted for presentation as Postdeadline Paper, ECOC 2005 Glasgow, Scotland.

DARPA MTO Symposium, March 4-6, 2007 27

Variable Length Packets and Dynamic Forwarding + 100ns Guard Band

PFC Packet λ-Conversion and OH Re-Write

Input Signal Blanking EAM

10ps Delay using deep-etched waveguide

SGDBR Tunable Laser

Flared Input Pre-amp SOAs

Dual SGDBR Signal Booster SOAs

1mm MZI SOAs

Label Rewrite EAM

Output λ2

A C E G I

Output λ1

B D F H JiMix 7:4:1 -> 40B:570B:1500B

1500B

A B C D E F G H I J

100ns Guard Band

40B570B

Input

WC 8ns 40GNew 10G OL

WC 300ns 40GNew 10G OL

WC 114ns 40GNew 10G OL

10G Optical Header Re-Write

DARPA MTO Symposium, March 4-6, 2007 28

32 x 32(64 x 64) AWGR

32 x 32(64 x 64) AWGR

40GFTWC/OLE/OLWArray

40GFTWC/OLE/OLWArray

Sync/ ORAMSync/

ORAMOLR/E

PEDOLR/E

PED

Basic Optical Data Router (ODR)

40GTWCArray

40GTWCArray

Optical L

abelR

ecovery/Payload E

nvelopeD

etect

Optical L

abelR

ecovery/Payload E

nvelopeD

etect Electronic Routing ProcessorElectronic Routing Processor

Synchronizers and Buffers

DARPA MTO Symposium, March 4-6, 2007 29

Small Buffer PerformanceOptical routers will receive access flows at much lower bandwidths than backbone links

-> naturally spaces packets

Small numbers of buffers make a large difference.

Only 20-50 buffers are needed (assuming customer is willing to sacrifice 25% of link capacity)

Studies were performed by Professor McKeown’s group (Enachescu et al ACM/SIGCOMM 2005)

Output-queued router. An increase of 60% in throughput is achieved with <15 buffers.

0

1

.5

Thro

ughp

ut

Number of buffer cells0 10050

DARPA MTO Symposium, March 4-6, 2007 30

Epitaxial layers, including lower two 1.2 Q layers for spot size conversion.

Fabricated SOA gate matrix switch wirebonded to an aluminum nitride submount.Input and output of a buffer showing spot size converters (left)

and 90˚ bends (right).

40-Gb/s RZ 27-1.

Hybrid Recircualating Packet Buffers

DARPA MTO Symposium, March 4-6, 2007 31

Optical Buffer (ORAM)Recirculating buffers for on-chip,

integrated optical packet buffer with dynamic control of storage time and random read.

Hybrid buffers are designed to combine the fast switching available with InGaAsP-based photonic chips and the low propagation loss available with silica waveguides.

Silica waveguides have been designed and fabricated. Testing shows loss of less than 0.02 dB/cm.

Recent device fabrication shows good results on improved design features such as spot size converters and 90˚ bends, however out-sourced material regrowth created contamination which limited performance.

InGaAsP gate matrix switches were designed, fabricated, and tested. Error-free performance was shown with negligible power penalty. [Burmeister, Photon. Technol. Lett., vol. 18, no. 1, 2006].

DARPA MTO Symposium, March 4-6, 2007 32

Integrated optical buffer-silicon evanescent amplifier

Thermal effect

1st generation resultsMaximum fiber to fiber gain: 3 dBEstimated chip gain of 13 dBThermally limited by heat generation due to high series resistance

2nd generation ObjectivesMaximum gain > 20 dBSilicon Input/Output waveguide for integration with silicon delay lines

Current statusFabrication is finished.Gain ripple because of reflections at the junction of silicon and III-V sectionBetter transition design needed such as tapers on III-V side.

Silicon waveguide

III-V bonded gain section

Long Term Goal: Demonstrate fully integrated optical packet buffer. Short Term Goals: 1) Demonstrate 10 passes around loo . 2) Demonstrate gain based switch architecture.

DARPA MTO Symposium, March 4-6, 2007 33

Chip Level 2x2 Optically Buffered ODR

Movie File

System Demonstrations

DARPA MTO Symposium, March 4-6, 2007 35

2x2 ODR Functional Diagram

• 10G Header Data• 10G Header Clock• Digital Payload Envelope

OHD/PED

•Analog Electrical•10G NRZ Optical Header•40G Payload Envelope

Burst Mode10G CDR

OH ErasePacket

Forwarding/OH Write

AWGRERP

•OH

B

lanking

•λ-select

∆optical

•New

OH

I1

I2

I3

I4

I5

I6

I7

I8

O1

O2

O3

O4

O5

O6

O7

O8

• 10G Header Data• 10G Header Clock• Digital Payload Envelope

OHD/PED

•Analog Electrical•10G NRZ Optical Header•40G Payload Envelope

Burst Mode10G CDR

OH ErasePacket

Forwarding/OH Write

•OH

B

lanking

•λ-select

∆optical

•New

OH

Input A

Input B

Output A

Output B

DARPA MTO Symposium, March 4-6, 2007 36

Electronic Control

Input A• PED• OH CDR

Input B• PED• OH CDR

Output A• Label Blanker• PFC Module

Output B• Label Blanker• PFC Module

Input A

Input B

OLR/PED OH CDROH Erase

PF Board

PFC Module

DARPA MTO Symposium, March 4-6, 2007 37

Layer-2/3 Results: Payload Throughput

1500B

Input iMix = 7:4:1

A B C D E F G H I J

95ns Guard Band

40B

570BOutput B (λ2)

A C E G I

Input A

Output λ1B D F H J

Output A (λ1)

20

40

60

80

100

120

0 1 2 3 4 5 6 7

1550.12 nm (w/o switching)1533.76 nm1539.28 nm

Payl

oad

Thro

ughp

ut (

%)

Optical input power (dBm)

~1 dB

Due to Tx/Rx bit errors

DARPA MTO Symposium, March 4-6, 2007 38

2x2 ODR Demonstration

H. Poulsen, W. Donat, V. Lal, M. Mashanovitch, G.Epps, D. Civello, C. Coldren, G. Fish, D. Blumenthal, “Demonstration of Simultaneous Multiplexing/Demultiplexing Operation of an All-Optical 2x2 Packet Switch with Asynchronous Variable-length Optically Labeled 40Gbps Packets,” Accepted for presentation at ECOC 2006.

ERP

LE

LE

CDRPED

CDRPED

1550.02nm

1553.32nm

Path A

Path B

1553.32nm

1550.02nm 1547.51nm

1541.90nm

1541.90nm

1547.75nm

Egress Port A

Egress Port B

DEM

UX

PFC

PFC

AWGR

From Ingress Port A

From Ingress Port B

Combined output

Egress port A Egress port B

From Ingress Port A

From Ingress Port B

Combined output

100ns/div

100ps/div

100ns/divFrom Ingress Port A

From Ingress Port B

Combined output

From Ingress Port A

From Ingress Port B

Combined output

Egress port A Egress port B

From Ingress Port A

From Ingress Port B

Combined output

From Ingress Port A

From Ingress Port B

Combined output

100ns/div

100ps/div

100ns/div

DARPA MTO Symposium, March 4-6, 2007 39

CSWDM and LASOR Building BlocksMonolithic dynamic wavelength converters

Regenerative, cascadable, input-output isolationTwo stage - internal wavelengths or wavebandsInternal wavelength optimized signal processing and memories

Dynamic data (packet) storage cells

Dynamic data (packet) synchronization cells

Data envelope detectors

All-optical clock and data recovery elements

Switches and gain blocks

Optical carrier filters

Optical data filters

DARPA MTO Symposium, March 4-6, 2007 40

Future Directions

Advance 2-stage wavelength converters with intermediate signal processing stages

Ultra low-loss waveguides

Phonon engineering for heat removal

Integrated coherent wavelength converters

Integration of FPGA electronics + digtial/analog + photonics

All-optical FPGAs made with programmable optical cells

New composite material systems that are engineered for optimum optical performance + thermal properties + integration with Si electronics