Process Simulation for 65 nm - SMDPII-VLSI:Special ... Process Simulation for 65 nm By ... Hierarchy...

Transcript of Process Simulation for 65 nm - SMDPII-VLSI:Special ... Process Simulation for 65 nm By ... Hierarchy...

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Process Simulation for 65 nm

ByHarish B.P.

Microelectronics Lab,Dept. of Electrical Communication Engg.,

Indian Institute of Science, Bangalore.E-mail: [email protected]

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Outline

• Introduction• Mechanism of process simulation• DIOS process simulator• Modeling and simulation of semiconductor processes• Case Study: Simulated 65 nm NMOS• Summary

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Introduction: Why Process Simulation?

• Computer simulation is now an essential tool for research and development of semiconductor process and device.

• Costs can be dramatically reduced by using simulation instead of experimentation, as much as possible, to fine-tune the process recipe.

• Shorter process development cycle.

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

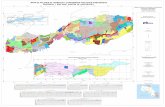

Hierarchy of Simulation Tools

Parameters for a. Oxidation, b. Ion implantation, c. Diffusion

SPICE parameters:VT, Tox, Ion, Ioff, SS, γ, Netlist

Delay, Power, NM

Process Simulation

Device Simulation

Circuit Simulation

Eq.s for a. Oxidationb. Ion implantationc. Diffusion

Tox, Xj, Tsp, TgateNa, Nd

Poisson’s Eq.Continuity Eq.

Nodal Eq. KCL, KVL

(Circuit Performance)

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Process Simulator

• Inputs to process simulation: lithography mask pattern, implantation dose and energy, temperatures and times for oxidation and annealing steps, etc.

• The process simulator generates a 2-D or 3-D structures with all the deposited or grown and etched thin films and doped regions.

• The output may be fed into a device simulator as input together with applied voltages, to evaluate the device electrical characteristics.

• Process/device is designed and optimized to meet the device design specifications, by process and device simulation based design approach.

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Outline

• Introduction• Mechanism of process simulation• DIOS process simulator• Modeling and simulation of semiconductor processes• Case Study: Simulated 65 nm NMOS• Summary

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Process Simulation - Mechanism

Space - time discretization• Represents device cross-section into a small cell.• Time discretization - Evaluate physical/chemical change

at each cell at every discrete time step.• Space discretization - Increment time step, update the

physical structure at each cell.• Moving boundary problem:

- Changing chemical composition at several mesh points- Simultaneous update Ex. Dynamically changing boundaries during oxide growth.

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Space Discretization

• The device cross section is represented as the collection of small cells .The various quantites such as φ, n, p etc are constant within the cell.

• Granularity of discretization: meshing - fine or coarse• Mesh must be densest in device regions where

- current density is high (MOS channels, bipolar base)- electric fields are high (MOS channels, drain, depletion regions)- charge generation is high (SEU alpha particle)

• Dynamic mesh re-adaptation – when a parameter varies by an order of magnitude from one mesh point to next.

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Time Discretization

• Discretize the time instants at which each cell is evaluated for its physical and chemical composition.

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Control Commands

• To select physical models for processes and their respective parameters

• Gridding/meshing strategies• Graphical output preferences

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Process simulators

1. T-SUPREM-IV from Stanford University (TAURUS- TSUPREM-IV from Synopsys)

2. Prophet from Bell Labs. 3. Florida Object Oriented Process Simulator (FLOOPS)4. DADOS5. Sentaurus Process from Synopsys6. SSuprem4 from SILVACO7. DIOS from Synopsys

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Outline

• Introduction• Mechanism of process simulation• DIOS process simulator• Modeling and simulation of semiconductor processes• Case Study: Simulated 65 nm NMOS• Summary

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Introduction to DIOS• DIOS is a multi-dimensional process simulator.• Supports simulations of complete fabrication sequences

– oxidation, diffusion, ion implantation, deposition/ etching, with models in 1-D and 2-D.

• Fully automatic meshing through adaptive grids.• Linear and non-linear solvers allow for simulation of

complex structures – 10,000 to 100,000 grid points.• Crystal-TRIM: 1-D and 2-D Monte Carlo simulator • Interface to 3-D Monte Carlo simulator - MCimpl.• Applicable to VLSI CMOS, power devices and advanced

SOI technologies.• Used with device simulator DESSIS to run and optimize

complete simulation flows.• Platforms supported: All UNIX flavours (Linux, Sun, HP,

IBM, SGI), Windows NT.

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

DIOS (contd.)

• Process flow simulated - sequence of commands corresponding to individual process steps.

• Procedure:- interactive mode: entered from standard input, at the prompt in command window.- composed in a command file.

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Outline

• Introduction• Mechanism of process simulation• DIOS process simulator• Modeling and simulation of semiconductor

processes• Case Study: Simulated 65 nm NMOS• Summary

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Modeling and Simulation of Semiconductor Processes

• Oxidation• Ion implantation• Diffusion

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Oxidation• Classification : 1. Growth

2. Deposition

• Growth of SiO2: T > 800oCHeat Si wafer in steam (Wet oxidation)

- in dry O2/N2 mixture (Dry oxidation) at temperatures –800 to 1250o.Dry oxidation: Si + O2 SiO2 ( Tox < 100 – 200nm)Wet oxidation: Si + 2H20 SiO2 + 2H2

• Deposition of SiO2: T < 600oCChemical Vapour Deposition:

SiH4 + O2 SiO2 + 2H2

400oC

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Modeling and simulation: Oxidation• Deal-Grove oxidation model:

Tox2 + ATox = B (t+τ) for Tox > 20 nm

Tox =BA

(t + τ) for Tox < 20 nm

where Tox = oxide thicknesst = oxidation timeB = parabolic rate constant

B/A = linear rate constantτ = native oxide dependent constant

Simulated oxidation parameters : 1. Thickness or time 2. Temperature3. Ambient4. Partial pressure

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Program for oxidation• TITLE (“oxidation”)

grid (x=(0.0,0.4) y=(-1.0,0.0),nx=2)substrate (orientation=100, elem=B, conc=5E14, ysubs=0.0)

replace (control (ngra=10))graph (triangle=off, plot)breaka. comment (‘dry oxidation’)

diff (time=8s, temper=900, atmo=O2, po2=1)b. comment (‘wet oxidation’)

diff (time=8s, temper=900, atmo=H2O)c. comment (‘oxide deposition’)

depo (ox, thick=16nm)

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Ion Implantation

• Beam of energetic ions implants dopants into the substrate.

• Depth and dopant concentration controlled by acceleration energy (implant energy) and beam current (implant dose) respectively.

• Dopant profile – Gaussian• Implantation produces crystal damage – anneal at 700 to

1000oC.

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Modeling and simulation: Ion Implantation

• Implantation is simulated by using:1. Analytical distribution functions – experimental implantation tables2. Monte Carlo simulation to compute implant distribution and implant damage.

• Simulated primary parameters: Implant species, implant energy and implant dose

• Simulated secondary parameters: Tilt, rotation (related to wafer)

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Program for Ion Implantation• TITLE (“implantation”)

comment (‘Ion implantation’)grid(x=(0.0,0.4) y=(-1.0,0.0),nx=2)substrate (orientation=100, elem=B, conc=5E14, ysubs=0.0)replace (control(ngra=10))graph (triangle=off, plot)breakimplant (element=P, dose=2E13, energy=300keV, tilt=0)

• elements: B, As; tilt: 6, 9,30.

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Diffusion• Diffusion - Dopant redistribution caused by dopant and

point defect diffusion by chemical reactions at interfaces and inside layers by convective dopant transport due to

a. internal electrical fields, b. material flow and c. moving material interfaces.

• Diffusion takes place during all high temperature processes.

• Process atmospheres – O2, N2, H2O, H2O2.• Diffusion is simulated on the basis of point defect

models.

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Modeling and simulation: Diffusion• Fick’s I law of diffusion:

Diffusion flux density F = -D ∂ C(x)

• Fick’s II law of diffusion:

∂ C(x,t) ∂ F(x,t) D ∂2 C(x,t)

∂x

∂x∂t= -

∂x2=

where D = Diffusivity (cm2/sec)C(x) = Vol. conc. gradient at x

F = Diffusion flux density (No. of particles/cm2-sec)Simulated diffusion parameters : 1. Time

2. Temperature3. Ambient4. Partial pressure

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Program for Diffusion• TITLE(“Diffusion”)

comment (‘diffusion’)grid(x=(0.0,0.4) y=(-1.0,0.0),nx=2)substrate (orientation=100, elem=B, conc=5E14, ysubs=0.0)replace (control(ngra=10))graph (triangle=off, plot)breakdepo (material=P, thickness=10nm)DIFFusion (time=10s, temperature=1050degC, atmo=N2, po2=0.75)

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Program for Annealing of DopantImplants

• TITLE (“implantation”)comment (‘Ion implantation’)grid(x=(0.0,0.4) y=(-1.0,0.0),nx=2)substrate (orientation=100, elem=B, conc=5E14, ysubs=0.0)replace (control(ngra=10))graph (triangle=off, plot)implant (element=P, dose=2E13, energy=300keV, tilt=0)breakDIFFusion (time=10, temperature=1050degC)

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Outline

• Introduction• Mechanism of process simulation• DIOS process simulator• Modeling and simulation of semiconductor processes• Case Study: Simulated 65 nm NMOS• Summary

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Full Program for simple NMOS

• TITLE (“65 nm NMOS example”)grid (x=(0.0,0.2325) y=(-10,0.0), nx=2)

substrate (orientation=100, elem=B, conc=1E16, ysubs=0.0)

replace (control (ngra=10))graph (triangle=on, plot)

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Program (contd.)

comment (‘p-well, anti punch-through and Vt implants’)

implant (element=B, dose=2E12, energy=200kev, tilt=0)

implant (element=B, dose=1E12, energy=100kev, tilt=7)

implant (element=In, dose=5.7E12, energy=150kev, tilt=7)

comment (‘p-well: RTA of channel implants’)

diff (time=10s, temper=1050)

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Program (contd.)comment (‘gate oxidation’)

diff (thickness=1.35nm, temper=800, atmo=O2, po2=0.75)

comment (‘poly gate deposition’)deposit (material=po, thickness=100nm)

comment (‘poly gate pattern’)mask (material=resist, thickness=800nm,xleft=0, xright=0.0325)

comment (‘poly gate etch’)etch (material=po, stop=oxgas, rate (anisotropic=100))

etch (material=ox, time=0.5, rate (aniso=10))

etch (material=resist)

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Program (contd.)

comment (‘poly reoxidation’)diffusion (temp=(700,800), temprate=3000, atmo=N2)diffusion (time=4.5s, temp=800, atmo=O2, po2=0.5)diffusion (temp=(800,700), temprate=3000, atmo=N2)

comment(‘initial nitride spacer’)depo (material=ni, thickness=96nm)etch (material=ni, remove=96nm, rate(aniso=75))

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Program (contd.)

etch (material=ni, stop=pogas, rate(aniso=10))

comment (N+ impl. and 20 sec RTA)impl (element=As, dose=6E15, energy=20keV, rotation=0, tilt=0)diff (time=20s, temp=1050, atmo=N2)

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Program (contd.)comment (‘dispose spacer’)

etch (material=ni)comment (‘overlap control spacer’)

depo (material=ni, thickness=14nm)etch (material=ni, remove=14nm, rate(aniso=75))

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Program (contd.)comment (‘nldd implantation’)

implant (element=As, dose=1E15, energy=5keV, rotation=0,tilt=0)

comment (‘Quad halo implant’)impl (element=B, Funct=Gauss, dose= 3.5E12,energy=8keV,rotation=0,tilt=30)

impl ( ,, rotation=90 ,,)impl ( ,, rotation=180 ,,)impl ( ,, rotation=270 ,,)

comment (‘screening oxide’)depo (material=ox, thickness=10nm)

comment (‘spike anneal’)diffusion (time=4sec, temp=1050, atmo=N2)

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Program (contd.)

comment (‘final nitride spacer’)depo (material=ni, thickness=40nm)etch (material=ni, remove=40nm,

rate(a1=75))

comment (‘etching screening oxide’)etch (material=oxide, stop=sigas,

rate (aniso=75))

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Program (contd.)

comment (‘full device structure”)reflect (window (bottom=-0.5)reflect (reflect=0.0)

comment (‘metal s/d contacts’)mask (material=al, thick=0.03, x(-0.2325, -0.1325, 0.1325, 0.2325))

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Program (contd.)comment (‘oxide fill’)mask (material=resist, thick=800nm, x((-

0.2325, -0.1325, -0.0325,0.0325, 0.1325, 0.2325))

depo (material=ox,dtype=fill)etch (material=ox, remove=728 nm)etch (material=resist)

Comment (’save final structure for device simulation’)

save ( file=’nmos’, type=mdraw, synonyms (po=metal, al=metal))

contacts (contact1(name=’source’, -0.1825, 0.01)

contact2(name=’gate’, 0.0, 0.05)contact3(name=’drain’, 0.1825, 0.01)contact4(name=’subs’,loc=bottom)

))end

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Input/Output Files of DIOS

• Input files:- filename.cmd – sequence of commands for processes.

• Output files:1. nmos_mdr.bnd – final region boundary descriptions.2. nmos_mdr.cmd – set of commands for MDRAW (meshing tool).3. nmos_dio.grd.gz – contains DIOS grid.4. nmos_dio.dat.gz – contains DIOS doping data.

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

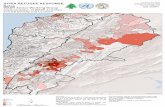

DIOS Generated Devices

a. NMOS b. PMOS

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Outline

• Introduction• Mechanism of process simulation• DIOS process simulator• Modeling and simulation of semiconductor processes• Case Study: Simulated 65 nm NMOS• Summary

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Summary

• Significance and mechanism of semiconductor process simulation is discussed.

• Modeling and simulation of various processes like oxidation, ion implantation and diffusion are described.

• A case study of generation of 65 nm NMOS is presented.

Harish B.P. Microelectronics Lab, ECE, IISc 8 December 2006

Thank You