poster

Click here to load reader

Transcript of poster

A Heterogeneous Framework for Co-emulation

Using ALDEC FPGA and QEMU-SystemC

=

Fig. 3. Effective bandwidth of the DRAM module

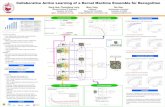

Fig. 1. Block diagram of the heterogeneous simulation framework

The architecture of the heterogeneous simulation framework is plotted in Fig. 1., including a fast and powerful instruction set simulator, QEMU, the ALDEC FPGA and a set of software modules for communication. Here we describe those modules in detail.

QEMU (short for "Quick EMUlator") is an

open-source hosted hypervisor that performs hardware virtualization. QEMU is a hosted virtual machine monitor. It emulates the behaviors of the CPU through dynamic binary translation and provides a set of device models so it can run a variety of unmodified guest operating systems.

QEMU-SystemC is an open source

hardware/software emulation framework for the SoC development provided by GreenSoC Corporation. It allows devices to be inserted into specific addresses of QEMU and communicates through the PCI/AMBA bus or the MMIO interface.

ALDEC’s FPGA and its HES-DVM (hardware

emulation system development tools) enables Hardware and Software Co-Verification utilizing a SCE-MI infrastructure which connects TLM modules to the DUT residing in hardware via high-speed AXI and AHB bus transactors. TLM modules can include virtual platforms utilizing the latest embedded processors, peripherals, and complete OS platforms for a complete SoC environment within HES-DVM.

A typical system design flow is often separated into several stages, such as the hardware/software partition and the co-verification. The bottleneck of a design flow usually occurs in the communication between the hardware and the software. Therefore, the ability to co-simulate the hardware/software interface fast and accurate is important in system-level design. In this work, we achieve efficient HW/SW co-verification through replacing the DRAM model of an instruction set simulator (ISS), QEMU, with the hardware DRAM modules provided by ALDEC’s FPGA.

To test the framework, we compare the read/write bandwidth of the DRAM system using several synthetic benchmarks with read/write operations only. The results are show in Fig. 3.

Through Fig. 3, we find that the bandwidth between random access and sequential access has no difference, corresponding to the characteristic of DRAM, and the bandwidth of byte access is much less than the others, because the access unit of the DRAM in FPGA is word, so we need to do further manipulations.

Introduction

Simulation Framework Simulation Flow

學生:B99902025 吳佳倫

指導教授:楊佳玲

Experiment Results

Fig. 2. Simulation flow of the FPGA implemented as SystemC module

The DRAM modules provided by the FPGA are implemented as an I/O device in QEMU. In QEMU, treatment to the memory access instructions is determined by the address. If the address is for I/O operations, corresponding I/O interfaces (implemented as callback functions) and interrupt handlers are invoked so the CPU can communicate with the I/O device.

The simulation flow is plotted in Fig. 1 and 2. The SystemC module is registered as a MMIO device in QEMU, as well as the callback function, sc_write and sc_read. If the guest OS accesses the MMIO memory region, sc_read or sc_write is called and the corresponding transaction is then passed to the GreenRouter through the TLM2 Socket. The GreenRouter access the SystemC Device based on the memory address (more than on SystemC devices are possible).

We add the API calls of the ALDEC FPGA in the SystemC function which is sensitive to read/write operations to send the read/write requests to FPGA. The results are then sent back from FPGA through the transactor.