PLDs ROM : Programmable OR array PLA : Programmable Logic Array. Programmable OR – AND arrays. PAL...

-

Upload

kristopher-parlett -

Category

Documents

-

view

337 -

download

12

Transcript of PLDs ROM : Programmable OR array PLA : Programmable Logic Array. Programmable OR – AND arrays. PAL...

PLDs

ROM : Programmable OR arrayPLA : Programmable Logic Array .

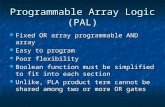

Programmable OR – AND arrays.PAL : Programmable Array Logic .

Programmable AND array, fixed ORGAL : Generic Array Logic

Can be configured to emulate many earlier PLDs including those with

internal Flip-Flops CPLD : Complex PLD FPGA : Field Programmable Gate Arrays

ROM : Read Only Memories

Matrix of data that is accesded one row at a timeInternaly a ROM contains a decoder and a storage array.

Functionally the data array can be viewed as a programmable OR array.

Types:Mask programmed ROMField programmable ROM – PROMErasable ROM – EPROMEllectrically programmable ROM - EEROM

PLDs

PALs and PLAs

Pre-fabricated building block of many AND/OR gates (or NOR, NAND)"Personalized" by making or breaking connections among the gates

Programmable Array Block Diagram for Sum of Products Form

Inputs

Dense array of AND gates Product

terms

Dense array of OR gates

Outputs

PALs and PLAs

Example:F0 = A + B' C'F1 = A C' + A BF2 = B' C' + A BF3 = B' C + A

Equations

Personality Matrix

Key to Success: Shared Product Terms

1 = asserted in term0 = negated in term- = does not participate

1 = term connected to output0 = no connection to output

Input Side:

Output Side:

Outputs Inputs Product t erm

Reuse of

t erms

A 1 - 1 - 1

B 1 0 - 0 -

C - 1 0 0 -

F 0 0 0 0 1 1

F 1 1 0 1 0 0

F 2 1 0 0 1 0

F 3 0 1 0 0 1

A B B C A C B C A

PALs and PLAsExample Continued

All possible connections are availablebefore programming

PALs and PLAsExample Continued

Unwanted connections are "blown"

Note: some array structureswork by making connections

rather than breaking them

PALs and PLAsAlternative representation for high fan-in structures

Short-hand notationso we don't have todraw all the wires!

Notation for implementingF0 = A B + A' B'F1 = C D' + C' D

PALs and PLAs

ABC

A

B

C

A

B

C

ABC

ABC

ABC

ABC

ABC

ABC

ABC

F1 F2 F3 F4 F5 F6

Design Example

F1 = A B C

F2 = A + B + C

F3 = A B C

F4 = A + B + C

F5 = A xor B xor C

F6 = A xnor B xnor C

Multiple functions of A, B, C

PALs and PLAsWhat is difference between Programmable Array Logic (PAL) and Programmable Logic Array (PLA)?

PAL concept — implemented by Monolithic Memories constrained topology of the OR Array

A given column of the OR arrayhas access to only a subset of

the possible product terms

PLA concept — generalized topologies in AND and OR planes

The main advantage of the PAL over the Pla and the ROM is that it is faster

PALs and PLAsDesign Example: BCD to Gray Code Converter

Truth Table K-maps

W = A + B D + B CX = B C'Y = B + CZ = A'B'C'D + B C D + A D' + B' C D'

Minimized Functions:

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

W 0 0 0 0 0 1 1 1 1 1 X X X X X X

X 0 0 0 0 1 1 0 0 0 0 X X X X X X

Y 0 0 1 1 1 1 1 1 0 0 X X X X X X

Z 0 1 1 0 0 0 0 1 1 0 X X X X X X

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

0 0 X 1

0 1 X 1

0 1 X X

0 1 X X

K-map for W

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

0 1 X 0

0 1 X 0

0 0 X X

0 0 X X

K-map for X

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

0 1 X 0

0 1 X 0

1 1 X X

1 1 X X

K-map for Y

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

0 0 X 1

1 0 X 0

0 1 X X

1 0 X X

K-map for Z

PALs and PLAsProgrammed PAL:

4 product terms per each OR gate

A B C D

0

0

0

0

0

0

PALs and PLAsCode Converter Discrete Gate Implementation

4 SSI Packages vs. 1 PLA/PAL Package!

B

\ B C

C

A

D

\ D

D W

X

Y B

B

B

B

C

C

A

D

\ A

\ C

\ B

\B \C

\A

\ D

2

2

1 1: 7404 hex inverters 2,5: 7400 quad 2-input NAND 3: 7410 t ri 3-input NAND 4: 7420 dual 4-input NAND

4

4

3

3

5

Z

1

3

2 1

2

D 1

1

4

2

PALs and PLAsAnother Example: Magnitude Comparator

EQ NE LT GT

ABCD

ABCD

ABCD

ABCD

AC

AC

BD

BD

ABD

BCD

ABC

BCD

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

1 0 0 0

0 1 0 0

0 0 1 0

0 0 0 1

K-map for EQ

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

0 1 1 1

1 0 1 1

1 1 0 1

1 1 1 0

K-map for NE

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

0 0 0 0

1 0 0 0

1 1 0 1

1 1 0 0

K-map for L T

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

0 1 1 1

0 0 1 1

0 0 0 0

0 0 1 0

K-map for GT

Typical First Generation PAL : 16L810 input, 2 complemented output, 6 I/O pinsProgrammable (one AND term) 3- state outputsSeven product terms per output20 pin chip

EXAMPLES

GAL 16V8C and 20V8C ( 20 pins and 24 pins)10 input (14 for 20V8)Programmable (one AND term) 3-state outputsSeven or eigth product terms per outputProgrammable output polarityThree combinational ouputs configurations: Bidir I/O ,

dedicated output , dedicated input.

PALs and PLAs

GAL 22V10C24 pin chip, 12 input terminals and 10 I/O terminalsTwo of the outputs can have up to 8 product terms, two have 10, two have 12, two have 14 and two have 16, not counting the ouput buffer control.Combinational configurations.

Combinational Logic Word ProblemsBCD to 7 Segment Display Controller

Understanding the problem:

input is a 4 bit bcd digit

output is the control signals for the display

4 inputs A, B, C, D

7 outputs C0 — C6

Block Diagram

C 5

C 0

C 6

C 3

C 4

C 1

C 2

C 0

C 1

C 2

C 3

C 4

C 5

C 6

BCD-to-7-segment control signal

decoder

7-Segment display

C 0 C 1 C 2 C 3 C 4 C 5 C 6

A B C D

BCD to 7 Segment Display Controller

C0 = A + B D + C + B' D'C1 = A + C' D' + C D + B'C2 = A + B + C' + D

C3 = B' D' + C D' + B C' D + B' CC4 = B' D' + C DC5 = A + C' D' + B D' + B C'C6 = A + C D' + B C' + B' C14 Unique Product Terms

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

1 0 X 1

0 1 X 1

1 1 X X

1 1 X X

K-map for C 0

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

1 1 X 1

1 0 X 1

1 1 X X

1 0 X X

K-map for C 1

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

1 1 X 1

1 1 X 1

1 1 X X

0 1 X X

K-map for C 2

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

1 0 X 1

0 1 X 0

1 0 X X

1 1 X X

K-map for C 3

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

1 0 X 1

0 0 X 0

0 0 X X

1 1 X X

K-map for C 4

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

1 1 X 1

0 1 X 1

0 0 X X

0 1 X X

K-map for C 5

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

0 1 X 1

0 1 X 1

1 0 X X

1 1 X X

K-map for C 6

BCD to 7 Segment Display Controller 0

32 64 96

128 160 192 224

First fuse numbers

1

19

2

0 4 8 12 16 20 24 28

256 288 320 352 384 416 448 480

18

3

512 544 576 608 640 672 704 736

17

4

768 800 832 864 896 928 960 992

16

5

1024 1056 1088 1120 1152 1184 1216 1248

15

6

1280 1312 1344 1376 1408 1440 1472 1504

14

7

1536 1568 1600 1632 1664 1696 1728 1760

13

8

1792 1824 1856 1888 1920 1952 1984 2016

12

9 11

Increment

Note: Fuse number = first fuse number + increment

16H8PALCan Implementthe function

BCD to 7 Segment Display Controller

14H8PALCannot Implementthe function

1

2 23

First fuse numbers

0 28 56 84

3

4

14

13

5

6

7

8

9

10

11

21 112 140

20 168 196

19 224 252

18 280 308

17 336 364

16 392 420

1 22

448 476 504 532

15

0 1 2 3 4 8 10 12 14 16 18 20 24 27

Note: Fuse number = first fuse number + increment

Increment

BCD to 7 Segment Display Controller

PLA Implementation

BCD to7 Segment Display Controller

Multilevel Implementation

X = C' + D'

Y = B' C'

C0 = C3 + A' B X' + A D Y

C1 = Y + A' C5' + C' D' C6

C2 = C5 + A' B' D + A' C D

C3 = C4 + B D C5 + A' B' X'

C4 = D' Y + A' C D'

C5 = C' C4 + A Y + A' B X

C6 = A C4 + C C5 + C4' C5 + A' B' C

52 literals

33 gates

Ineffective use of don't cares

Implementation StrategiesMore Advanced PAL Architectures

Registered PAL ArchitectureBuffered Input

or product term

Negative LogicFeedbackD2 = Q2 • Q0 + Q2 • Q0

D1 = X • Q2 • Q1 • Q0 + X • Q2 + X • Q0 + Q2 • Q0 + Q1 • Q0

D0 = Q0

Z = X • Q1 + X • Q1

CLK OE

D2 Q2+

Q2+

Q2 Q2 Q0 Q0

X

D Q

Q

Q2 • Q0

Q2 • Q0

Q2 • Q0 + Q2 • Q0

Q2 • Q0 + Q2 • Q0

Q2+

Implementation StrategiesAdvanced PAL Architectures

Programmable Output Polarity/XOR PALs

Buried Registers: decouple FF from the output pin

CLK OE

D Q

Q

A B C D A B C D A B C D A B C D A B C D A B C D A B C D A B C D

A B C D A B A B

C D C D

A B C D

Advantage of XOR PALs: Parity and Arithmetic Operations

Implementation Strategies

1

040

80120

23D Q

Q

2

160200

240280

22D Q

Q

3

320360

400440

21D Q

Q

4

480520

560600

20D Q

Q

5

640680

720760

19D Q

Q

6

800840

880920

18D Q

Q

7

9601000

10401080

17D Q

Q

8

11201160

12001240

16D Q

Q

9

12801320

13601400

15D Q

Q

10

14401480

15201560

14D Q

Q

11 13

0 4 8 12 16 20 24 28 32 36

0 4 8 12 16 20 24 28 32 36

NOTE: FUSE NUMBER = FIRST FUSE NUMBER + INCREMENT

INCREMENT

FIRST FUSE

NUMBER

INCREMENT

Example of XOR PAL

1

11

0 4 8 12 16 20 24 28

INCREMENT

0

19

2

326496

128160192224

256

18

3

288320352384416448480

D Q

Q

512

17

4

544576608640672704736

D Q

Q

768

16

5

800832864896928960992

D Q

Q

1024

15

6

1056108811201152118412161248

D Q

Q

1280

14

7

1312134413761408144014721504

D Q

Q

1536

13

8

1568160016321664169617281760

D Q

Q

1792

12

9

1824185618881920195219842016

FIRST FUSE NUMBERS

Example of Registered PAL

Implementation StrategiesFSM Design with More Sophisticated PLDs

Programmable Logic Devices = PLD

Field Programmable Gate Arrays = FPGAs (CLB:Configurable Logic Block)

• Altera MAX Family

• Actel Programmable Gate Array

• Xilinx Logical Cell Array

PALs, PLAs = 10 - 100 Gate Equivalents

100 - 1000(s) of Gate Equivalents!

CPLDs Increasing the size of a conventional PAL or GAL is not

aneffective way to increase complexity.

Several PALs on one chip. Xilinx 9500-series : PLDs have 18 output macrocells,

CPLDs have from 2 to 16 PLDs Packages have from 44 to 352 pins

Clk MUX

Output MUXQ

F/B MUX

Invert Control

AND ARRAY

CLK

pad

Implementation StrategiesDesign with More Sophisticated PLDs

Altera EPLD (Erasable Programmable Logic Devices)

Historical Perspective: PALs – same technology as programmed once bipolar PROM EPLDs — CMOS erasable programmable ROM (EPROM) erased by UV light

Altera building block = MACROCELL

8 Product TermAND-OR Array

+Programmable

MUX's

Programmable polarity

I/O Pin

Seq. LogicBlock

Programmable feedback

Implementation StrategiesDesign with More Sophisticated PLDs

Altera EPLDs contain 8 to 48 independently programmed macrocells

Personalized by EPROM bits:

Flipflop controlledby global clock signal

local signal computesoutput enable

Flipflop controlledby locally generatedclock signal

+ Seq Logic: could be D, T positive or negative edge triggered+ product term to implement clear function

Synchronous Mode

Asynchronous Mode

Global CLK

OE/Local CLK

EPROM Cell

1

Global CLK

OE/Local CLK

EPROM Cell

1

Clk MUX

Clk MUX

Q

Q

LAB A LAB H

LAB B LAB G

LAB C LAB F

LAB D LAB E

P I A

Implementation StrategiesDesign with More Sophisticated PLDs

AND-OR structures are relatively limited Cannot share signals/product terms among macrocells

Altera solution: Multiple Array Matrix (MAX)

LogicArray

Blocks

(similar tomacrocells)

Global Routing:ProgrammableInterconnect

Array

8 Fixed Inputs52 I/O Pins8 LABs16 Macrocells/LAB32 Expanders/LAB

EPM5128:

Implementation StrategiesDesign with More Sophisticated PLDs

LAB Architecture

Expander Terms shared among allmacrocells within the LAB

Macrocell ARRAY

I/O Block

Expander Product

Term ARRAY

I NPUTS

P I A

I/O Pad

I/O Pad

Macrocell P-Terms

Expander P-Terms