Phase-Locked Loop Circuit Design...Phase-Locked Loop Circuit Design —From Basics to...

Transcript of Phase-Locked Loop Circuit Design...Phase-Locked Loop Circuit Design —From Basics to...

Phase-Locked Loop Circuit Design

— From Basics to State-of-The-Art and Industrial Practices —

Atsushi Motozawa(email: [email protected] )

Renesas Electronics Corporation

A. Motozawa Page2

Outline

◼What is a PLL?

◼ Applications

◼ Building blocks & Design tips

◼ Advanced architecture

◼ Summary

A. Motozawa Page3

MCU Operation Frequency

6300

2MHz

H8/500

10MHz

SH7055

40MHz

V850

195MHz

Quadruple

over decade

1980 1990 2000 2010

Year

Op

era

tio

n f

req

ue

nc

y f

or

MC

U

◼ Operation frequency getting higher year by year

◼ Quadruples every decade

◼ Clocks of a few giga Hz are needed for SoCs

A. Motozawa Page4

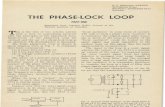

What is a PLL?

◼ Frequency multiplication ◼ Phase difference reduction

PLLCLKin CLKout

CLKin

CLKout

x N

CLKin

CLKout

A. Motozawa Page5

How to distribute high frequency clock

◼ IC without PLL ◼ IC with PLL

CPU

1.5GHz

Logic

500MHz

PLL

PLL

20MHzCPU

1.5GHz

Logic

500MHz

1.5GHz

500MHz

✓Crosstalk and reflectioncan occur

✓Extra space in PCB

✓Many pins are needed

✓Low input frequency

✓w/o crosstalk or reflection

✓Several identical PLLs with different divisors in one IC

X 75

X 25

A. Motozawa Page6

Outline

◼What is a PLL?

◼ Applications

◼ Building blocks & Design tips

◼ Advanced architecture

◼ Summary

A. Motozawa Page7

Clock Deskewing

◼ Clock skew due to clock distribution

◼ With skew, It’s difficult to make synchronous systems

◼ Skew is dependent on power supply voltage and temperature

Skew

CLK1Logic1

Logic2CLK2

CLK1

CLK2

Data

buffers

A. Motozawa Page8

Clock Deskewing

◼ Clock buffers are put into deskew PLL

◼ PLL reduces the phase difference between CLK1 and CLK2

◼ PLL can work even if supply voltage and temperature change.

PFD

/CP Filter VCO

Logic1

Logic2

Deskew PLL

CLK1

CLK2

CLK1

CLK2

Data

A. Motozawa Page9

Spread Spectrum Clock (SSC)

PFD

/CPFilter VCO

1/N

Fin=10MHz

DIV

Fout

1GHz

➢ Output frequency

➢ PSD

1

GHz

Conventional

◼ An LSI operates at 1GHz.The LSI emits EMI noise.

◼ It can interfere with other LSIs and signals on PCBs.

Freq.

Am

plit

ude

N=100

time

A. Motozawa Page10

Spread Spectrum Clock (SSC)

PFD

/CPFilter VCO

1/N

ΔΣ

Fin=10MHz

N=100

N=99

DIV

1%

Fout

1GHz

0.99GHz10MHz

➢ Output frequency

➢ PSD

1

GHz

0.99

GHz

SSC

ConventionalEMI

reduction

(1% of 1GHz)

◼ ΔΣ modulated divider to generate SSC

◼ ΔΣ noise is filtered by PLL

Freq.

Am

plit

ude

1/fmod

A. Motozawa Page11

CDR(Clock and Data recovery)

PLL

Incoming

data Data

Recovered

CLK1 0 1 0 1 0

Recovered

CLK

Data

D Q

◼ Incoming data without accompanying clock

◼ CDR extracts a clock to sample incoming data

Incoming

data

1

0

A. Motozawa Page12

Outline

◼What is a PLL?

◼ Applications

◼ Building blocks & Design tips

◼ Advanced architecture

◼ Summary

A. Motozawa Page13

PLL Diagram

D Q

R

D QR

UP

DN

Rdeg

gm

Cpl R

Cz

DQ DQ

Icp

Icp

IN

OUT

How do we design a PLL?

A. Motozawa Page14

Block diagram and Domains

IN

rad→rad

OUT

rad→A A→V V→A A→rad/s→rad

radrad

PFD Filter CCOCP GM

DIV

PLL’s building blocks

⚫ PFD: Phase-Frequency Detector

⚫ CP: Charge Pump

⚫ Loop filter

⚫ GM (Voltage-current converter)

⚫ CCO: Current-controlled Oscillator

⚫ Divider

[rad]

[A]

[V]

Line Domain

A. Motozawa Page15

PLL Diagram

IN

OUT

PFD

(Phase-frequency detector)

D Q

R

D QR

UP

DN

Rdeg

gm

Cpl R

Cz

DQ DQ

Icp

Icp

A. Motozawa Page16

PFD(Phase-frequency detector)

D Q

R

D QR

DelayCLKin

CLKfb

UP

DN

CLKin

CLKfb

RST

RSTd

UP

DN

CLKin

CLKfb

RST

RSTd

UP

DN

Case1 (CLKfb is behind) Case2 (CLKfb is ahead)

RSTRSTd

VDD

◼ CLKfb is behind CLKin

→UP is wider

◼ CLKfb is ahead of CLKin

→DN is wider

◼ RST is delayed

to avoid dead zone

A. Motozawa Page17

D Q

R

D QR

UP

DN

Rdeg

gm

Cpl R

Cz

DQ DQ

Icp

Icp

PLL Diagram

IN

OUT

CP

(Charge pump)

A. Motozawa Page18

UP

DN

IoutICP

-ICP

0

CP (Charge Pump)

◼ Output is pulse-shaped current that is dependent on the width of the phase difference

◼ CP gain is Icp/(2*pi) [A/rad]

UP

DN

Iout

ICP

ICP

CLKin

CLKfb

Case1 Case2 Case3

Average

of Iout [A] −𝜽𝟏

𝟐𝛑∙ 𝐈𝐂𝐏

𝜽𝟏 𝜽𝟐 𝜽𝟑

−𝜽𝟐

𝟐𝛑∙ 𝐈𝐂𝐏

𝜽𝟑

𝟐𝛑∙ 𝐈𝐂𝐏

A. Motozawa Page19

Modeling of PFD and CP set

◼ PFD becomes summing block.

◼ CP becomes gain block

D Q

R

D QR

CLKin

CLKfb

UP

DN

VDD

Iout

ICP

ICP

ICP

2π

Φin[rad]

Φfb[rad]

Iout[A]

PFD CP

PFD CP

A. Motozawa Page20

PLL Diagram

IN

OUT

Loop filter

(Lead-lag filter)

D Q

R

D QR

UP

DN

Rdeg

gm

Cpl R

Cz

DQ DQ

Icp

Icp

A. Motozawa Page21

Loop Filter

◼ Converts the domain: current → voltage

◼ Cz is much larger than Cpl → Cz+Cpl ≈ Cz

◼ Lead-lag compensation

Iin Vout

CplR

Cz

H s =Vout

Iin=

1

sCz∙sRCz + 1

sRCpl + 1

20*l

og|H

|[dB

]

-20dB/dec

∠H

[deg]

fp =1

2πRCplfz =

1

2πRCz [Hz] [Hz]

log(f) [Hz]

fp 10fpfz/10 fz

-90

-45

0

log(f) [Hz]

From CP To GM

Zero 2nd pole

A. Motozawa Page22

PLL Diagram

IN

OUT

GM

(Transconductor)

D Q

R

D QR

UP

DN

Rdeg

gm

Cpl R

Cz

DQ DQ

Icp

Icp

A. Motozawa Page23

GM

◼ Voltage-current converter

◼ Rdeg reduces the transconductance but the linear range becomes wider.

Rdeg

Vin

From Filter Icco

Connected to CCO

gm gm_eq =gm

gmRdeg + 1

A. Motozawa Page24

Modeling of loop filter and GM set

Rdeg

Icco

Connected to CCO

gm

CplR

Cz

From CP

Iin

Loop Filter GM

1

sCz∙sRCz + 1

sRCpl + 1

Icco[A]gm_eq

Iin[A]Vc

Vc[V]

◼ Loop filter converts the domain from current to voltage

◼ GM becomes gain block and coverts the domain from voltage to current

gm_eq =gm

gmRdeg + 1

Loop Filter GM

A. Motozawa Page25

D Q

R

D QR

UP

DN

Rdeg

gm

Cpl R

Cz

DQ DQ

Icp

Icp

PLL Diagram

IN

OUT

CCO

(Current-controlled oscillator)

A. Motozawa Page26

CCO (Current-Controlled Oscillator)

Icco

Icco[A]

𝜕

𝜕Icco

Icco[A]

ωcco[r

ad/s

]K

cco

rad/s

A

◼ The number of stages is commonly 3—5.

◼ Fcco=1/(2*Td*N) [Hz]

◼ In this talk, [rad/s/A] is used for Kcco. NOT [Hz/A]

Delay = Td

N: the number of stages for CCO

A. Motozawa Page27

t[s]

t[s]

Relationship Between Frequency and Phase

𝛚

1

s

0 0.5 1 1.5

𝛚[ Τ𝐫𝐚𝐝 𝐬] 𝛉 𝐫𝐚𝐝

t t

◼ Phase is the time integral of frequency

𝛚 ∙ 𝒕ω 𝜃

𝛉

𝛉

Frequency Phase

A. Motozawa Page28

Modeling of CCO

◼ Domain change: A → rad/s → rad

◼ -90° phase shift at DC

◼ Kcco is dependent on the operation frequency

Icco

1

sKcco

Icco[A]

[rad/s/A]

ωcco

[rad/s]

ϕout[rad]

CCO CCO

A. Motozawa Page29

D Q

R

D QR

UP

DN

Rdeg

gm

Cpl R

Cz

DQ DQ

Icp

Icp

PLL Diagram

IN

OUT

Divider

A. Motozawa Page30

Divider

D Q D Q

CLK

D Q D Q

CLK

D1

Q1(Divide-by-2)

D2D1

Q1Q2

CLK

Q1

D1

Q2

D2

CLK

Q1

D1

Q2

• Divide-by-2 and 4 divider • Divide-by-3 divider

Q2(Divide-by-4)

Q2(Divide-by-3)

A. Motozawa Page31

Modeling of Divider

D Q D Q

CLK

D1

Q1

D2

1

𝑁𝜔𝑖𝑛

𝜔𝑜𝑢𝑡𝜑𝑖𝑛 𝜑𝑜𝑢𝑡

Divide-by-N divider Divide-by-N divider

𝜔𝑜𝑢𝑡 =1

𝑁𝜔𝑖𝑛

𝜙𝑜𝑢𝑡 =1

𝑁𝜙𝑖𝑛

Frequency Domain

Phase Domain

[rad/s]

[rad]

A. Motozawa Page32

Modeling of Single-Path PLL

Φfb[rad]

ICP

2π

Φin[rad] Iout[A] 1

sCz∙sRCz + 1

sRCpl + 1gm_eq

Vc[V] 1

sKcco

Icco[A]

ωcco

[rad/s]Φout[rad]

D Q

R

D QR

UP

DN

Rdeg

gm

Cpl R

Cz

DQ DQ

Icp

Icp

PFDCP CCO

GMFilter

Divider

PFD CP Filter GMCCO

Divider

CLKin

CLKfb

CLKout

IoutVc Icco

A. Motozawa Page33

PLL transfer function and Bode Plot

Φfb[rad]

ICP

2π

Φin[rad] Iout[A] 1

sCz∙sRCz + 1

sRCpl + 1gm_eq

Vc[V] 1

sKcco

Icco[A]

ωcco

[rad/s]Φout[rad]

PFD CP Filter GMCCO

Divider

𝐻𝑜𝑝 =𝐾𝐶𝐶𝑂𝐼𝑐𝑝

2𝜋𝑁∙1

𝑠2∙𝑔𝑚_𝑒𝑞

𝐶𝑧∙𝑠𝑅𝐶𝑧 + 1

𝑠𝑅𝐶𝑝𝑙 + 1

1

2𝜋𝑅𝐶𝑝𝑙00 , ,Poles[Hz]

1

2𝜋𝑅𝐶𝑧Zero[Hz]

Crossover freq.[Hz] ≈𝐾𝐶𝐶𝑂𝐼𝑐𝑝𝑔𝑚_𝑒𝑞𝑅

2𝜋 2𝑁

Open loop

Gain

[dB

]

-180°

-135°

-90°

-40dB/dec

-20dB/dec

Phase[d

eg]

Log(f)

0dB

-40dB/dec

Log(f)

Open loop

Transfer function

A. Motozawa Page34

-360 -345 -330 -315 -300 -285 -270 -255 -240 -225 -210 -195 -180 -165 -150 -135 -120 -105 -90 -75 -60 -45 -30 -15 0-60

-50

-40

-30

-20

-10

0

10

20

30

40

50

60

6 dB

3 dB

1 dB

0.5 dB

0.25 dB

0 dB

-1 dB

-3 dB

-6 dB

-12 dB

-20 dB

-40 dB

-60 dB

ニコルス線図

開ループ位相 (deg)

開ル

ープ

ゲイ

ン (

dB)

PLL open loop line on Nichols Chart

◼ The X-axis: Open loop PhaseThe Y-axis: Open loop GainDashed circles: Closed loop Gain

◼ If the open loop line passes by the right side of the red cross(-180deg, 0dB), the system is stable.

◼ System is stable as long as the open loop gain is large enough

60

0

Open Loop Phase [deg]

40

Open loop

Gain

[dB

]

-180

-135

-90

Open loop

Phase[d

eg]

Log(f)

Log(f)

1dB

Nichols chart

-180deg

0dB

0.25dB

3dB

60dB

20

-20

Open loop G

ain

[dB

]

Bode chart

A. Motozawa Page35

Dual-Path PLL

𝐻𝑜𝑝 =𝐾𝐶𝐶𝑂𝐼𝐶𝑃𝐼

2𝜋𝑁∙1

𝑠2∙𝑔𝑚_𝑒𝑞

𝐶𝑧∙

𝑠𝐶𝑧

𝑔𝑚_𝑒𝑞

𝐼𝐶𝑃𝑃𝐼𝐶𝑃𝐼

+ 1

𝑠𝑅𝐶𝑝𝑙 + 1

Open loop

Transfer function

1

2𝜋𝑅𝐶𝑝𝑙00 , ,Poles[Hz]

1

2𝜋

𝑔𝑚_𝑒𝑞

𝐶𝑧

𝐼𝐶𝑃𝐼

𝐼𝐶𝑃𝑃Zero[Hz]

Crossover freq.[Hz] ≈𝐾𝐶𝐶𝑂𝐼𝐶𝑃𝑃

2𝜋 2𝑁

Integral Path

Proportional Path

◼ Zero can be controlled by the ratio of ICPP and ICPI. That leads to smaller Cz

◼ Single-path PLL: Cz~100pFDual-path PLL : Cz~20pF

Φfb[rad]

ICPP

2π

Φin[rad] 1

sRCpl + 1

gm_eq

1

sKcco

Φout[rad]

ICP

2π

1

sCz

A. Motozawa Page36

Outline

◼What is a PLL?

◼ Applications

◼ Building blocks & Design tips

◼ Advanced architecture

◼ Summary

A. Motozawa Page37

Hybrid PLL

“A 0.7-to-3.5 GHz 0.6-to-2.8 mW

Highly Digital Phase-Locked Loop With Bandwidth Tracking”Wenjing Yin, et al., IEEE JSSC, VOL. 46, NO. 8, pp1870—1880, AUG. 2011

◼ Analog-Digital Hybrid

✓Small & programmable

✓Analog proportional path to reduce quantization error

◼ !!PD instead of TDC

✓Simple, Small, and Low power

✓ Intrinsically nonlinear → Jitter makes it linear

A. Motozawa Page38

Outline

◼What is a PLL?

◼ Applications

◼ Building blocks & Design tips

◼ Advanced architecture

◼ Summary

A. Motozawa Page39

Summary

◼ PLLs are utilized in many ICs✓One IC contains several identical PLLs to provide different

frequency clocks while reducing I/O pins and avoiding the reflection

◼ Many PLL applications✓Not only frequency multiplication

✓SSC to reduce EMI noise

✓CDR system to generate from incoming data

✓Deskew PLL to decrease phase error among clocks

◼ Building blocks and transfer functions are discussed✓Several domains in PLL loop

✓Dual-path PLL is used to reduce capacitor

◼ Analog-digital hybrid PLL with !!PD is introduced✓The keywords, digital-rich and !!PD , are important

for an advanced PLL design