Pavilion Dv5 - Quanta QT8 - II AMD

Transcript of Pavilion Dv5 - Quanta QT8 - II AMD

1

2

3

4

5

6

7

8

PCB STACK UPLAYER LAYER LAYER LAYER LAYER LAYER 1 2 3 4 5 6 : : : : : : TOP IN1 IN2 VCC IN3 BOT

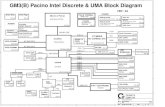

QT8 SYSTEM DIAGRAMDDRII-SODIMM1 PAGE 7,8 DDRII-SODIMM2 PAGE 7,8DDRII 667/800 MHz DDRII 667/800 MHz

0114.318MHzA

A

S1G2 Processor

AMD Lion Sabie Griffin

CPU THERMAL SENSOR PAGE 5CPU_CLK NBGFX_CLK NBGPP_CLK SBLINK_CLK

638P (uPGA)/35W PAGE 3,4,5,6

CLOCK GENICS9LPRS476AKLFT-->HP SLG8SP626VTR-->HP RTM880N-795 -->HP

HT3PCI-Express 16X

PAGE 2

PCI-E Cable Docking VGA RJ-45 CIR/Pwr btn SPDIF Out Stereo MIC Headphone Jack USB Port VOL CntrX1 X1 Express Card X3 Mini PCI-E Card(Wireless LAN/TV TUNNER)

NORTH BRIDGERX781 / RS780MN A1221mm X 21mm, 528pin BGA Side port

HDMI PAGE 23 CRT PAGE 24 LVDS PAGE 23

ATI M82-S for Discrete only 64 Bit,DDR2*4

10

PCI-E WLAN Card x1 PAGE 36 TV-TUNER Card x1 PAGE 36 Express Card x1 PAGE 33 Cable Docking x1 PAGE 37

LANRealtek PCIE-LANRTL8102E/8111C (10/100/GagaLAN)

11 7

(NEW CARD)

B

M82-SCE A11PAGE 17,18,19 20,21,224

B

PAGE 31,32

PAGE 33

PAGE 36 PAGE 8,9,10,11,

PAGE 37 RJ45 PAGE 31SYSTEM CHARGER(ISL6251A)

ALINK X4SATA0,1 150MB

256mb RAM for UMA only

PAGE 8 USB2.01,8,9

SBSRC_CLK

PAGE 44SYSTEM POWER ISL6236IRZA-T

TWO SATA - HDD

5 Blueflame PAGE 30

2

6 Fingerprint PAGE 30

3 Flash Media for UMA only RTS5158 PAGE 25 Touch Screen for Discrete only

PAGE 33SATA - CD-ROM

SOUTH BRIDGESATA0 150MB

USB2.0 Ports PAGE 30 X3

Webcam X1 PAGE 30JMICRON JMD380 for Discrete only

PAGE 38DDR II SMDDR_VTERM 1.8V/1.8VSUS(TPS51116REGR)C

SB700 A1221mm X 21mm, 528pin BGA

PAGE 33E-SATA

PCIE BUS Azalia

4.5W(Ext)

PAGE 41VCCP +1.1V AND +1.2V(MAX8717)

SATA4 150MB PAGE 30 SMBUS

4.3W(Int)

C

PAGE 12,13.14.15.16

PAGE 27

PAGE 39VGACORE(1.1V~1.2V)Oz8118

Accelerometer LIS3LV02DL

PAGE 28 PAGE 34 PAGE 34

LPC MDC CONN PAGE 29

IDT 92HD71B7

PAGE 42CPU CORE ISL6265A

Keyboard Touch Pad

PAGE 27IEEE1394 connect for Discrete only Memory CardReader

ENE KBCKB3926 Cx

PAGE 40SMBUS TABLED

CIR (AUDIO CONN) PAGE 27 Capacitive Sense PAGE 34 SW+3V

AUDIO Amplifier TPA6017A2

PAGE 26

PAGE 25

PAGE 35Digital MIC

PAGE 28D

SB--SCL0/SD0

Clock gen/Robson/TV tuner /DDR2/DDR2 thermal/Accelerometer

AUDIO CONN(Phone/ MIC)

epress card Wlan Card +3VS5 +3VPCU +3V

FAN

SPI

PAGE 30

PAGE 27

Audio Conn PAGE 28

EC --SCL/SD EC--SCL2/SD21

Battery charge/discharge VGA thermal/system thermal

PROJECT : QT8 Quanta Computer Inc.Size Custom NB5/RD5 Document Number

PAGE 37 PAGE 353 4 5 6

Block DiagramSheet 18

Rev 1A of 45

Date: Tuesday, February 19, 20082 7

5

4

3

2

1

+1.2V

L49 BLM18PG181SN1D(180,1.5A)_6

60 ohm, 0.5A

CLOCKS name+1.2V_CLKVDDIO C496 0.1U/10V_4 C527 C521 0.1U/10V_4 0.1U/10V_4 C476 0.1U/10V_4 C515 0.1U/10V_4

RX780 RP64 STUFF

RS780 RP64 STUFF

Clock pin function to NB for VGA reference clock

600 ohms@100Mhz

C523 10U/6.3V_8

C518 0.1U/10V_4

NBGFX_CLKP NBGFX_CLKN EXT_GFX_CLKP EXT_GFX_CLKN

02D

RP66 STUFF

RP66 NC

to M82-S external reference clock -RX780 only

DCR: 0.5 ohmD

600 ohms@100Mhz+3V

+3V_CLKVDD

L51 BLM18PG181SN1D(180,1.5A)_6 C541 10U/6.3V_8

60 ohm, 0.5A

NBGPP_CLKP NBGPP_CLKN+3V_CLKVDD C512 0.1U/10V_4 C522 0.1U/10V_4 C508 0.1U/10V_4 C500 0.1U/10V_4 C474 0.1U/10V_4 C471 0.1U/10V_4 C469 0.1U/10V_4

RP70 STUFF

RP70 NC

to NB for RX780 for PCIEX2 interface reference clock only RS780 is internal share with AC-LINK clock,RS780 not need to NB for AC-LINK reference clock

C468 0.1U/10V_4

C473 0.1U/10V_4

SBLINK_CLKP SBLINK_CLKN

RP72 STUFF

RP72 STUFF

+3V_CLKVDD L42 BLM18PG181SN1D(180,1.5A)_6 C464 10U/6.3V_8

Place very close to C/G+3V_CLK_VDDA C482 0.1U/10V_4 +3V_CLK_VDDA C470 0.1U/10V_4 U10A 49 48 62 66 69 29 54 61 38 17 44 3 53 28 37 12 18 72 27 6 52 58 47 36 11 19 CG_XIN CG_XOUT CLK_PD# 67 68 57 1 2 VDDA GNDA VDDREF GNDREF VDD48 VDDATIG VDDCPU VDDHTT VDDSB_SRC VDDSRC VDDSATA VDDDOT VDDCPU_IO VDDATIG_IO VDDSB_SRC_IO VDDSRC_IO1 VDDSRC_IO2 GND48 GNDATIG1 GNDDOT GNDCPU GNDHTT GNDSATA GNDSB_SRC GNDSRC1 GNDSRC2 X1 X2 PD# SMBCLK SMBDAT REF0/SEL_HTT66 REF1/SEL_SATA REF2/SEL_27 CLKREQ0# CLKREQ1# CLKREQ2# CLKREQ3# CLKREQ4# CPUKG0T_LPRS CPUKG0C_LPRS ATIG0T_LPRS ATIG0C_LPRS ATIG1T_LPRS ATIG1C_LPRS ATIG2T_LPRS ATIG2C_LPRS SB_SRC0T_LPRS SB_SRC0C_LPRS SB_SRC1T_LPRS SB_SRC1C_LPRS SRC0T_LPRS SRC0C_LPRS SRC1T_LPRS SRC1C_LPRS SRC2T_LPRS SRC2C_LPRS SRC3T_LPRS SRC3C_LPRS SRC4T_LPRS SRC4C_LPRS SRC5T_LPRS SRC5C_LPRS SRC6T/SATAT_LPRS SRC6C/SATAC_LPRS SRC7T_LPRS/27Mhz_SS SRC7C_LPRS/27Mhz_NS HTT0T/66M_LPRS HTT0C/66M_LPRS 48MHz_0 48MHz_1

CLK_VGA_27M_SS CLK_VGA_27M_NSS

R653,R656,R612 R653,R656,R612 STUFF NC

To M82-S 27Mhz - RX780 only

Place within 0.5" of CLKGEN56 55 33 32 31 30 26 25 40 39 35 34 23 22 21 20 16 15 14 13 10 9 8 7 46 45 5 4 60 59 71 70 65 64 63 24 51 50 43 42 CPUCLKP CPUCLKN NBGFX_CLKP NBGFX_CLKN EXT_GFX_CLKP EXT_GFX_CLKN RP43 RP54 RP53 T196 T84 PCIE_MINI2_CLKP PCIE_MINI2_CLKN CLK_PCIE_CARD CLK_PCIE_CARD# NBGPP_CLKN_R NBGPP_CLKN_L PCIE_NEW_CLKP PCIE_NEW_CLKN PCIE_MINI1_CLKP PCIE_MINI1_CLKN SBLINK_CLKP SBLINK_CLKN SBSRC_CLKP SBSRC_CLKN PCIE_LAN_CLKP PCIE_LAN_CLKN CLK_VGA_27M_SS CLK_VGA_27M_NSS NBHTREFCLK0P NBHTREFCLK0N CLK_48M_CR_L CLK48MUSB SEL_HT66 SEL_SATA SEL_27 CLKREQ0# EXT_NWD_CLK_REQ# CLKREQ2# CLKREQ3# CLKREQ4# RP48 RP55 4 2 4 2 4 2 4 2 4 2

R196

*261_4

Del RP for TP on PVCPUCLKP 3 CPUCLKN 3 NBGFX_CLKP 10 NBGFX_CLKN 10 EXT_GFX_CLKP 17 EXT_GFX_CLKN 17

3 *0_4P2R_4 CPUCLKP CPUCLKN 1 3 *0_4P2R_4 NBGFX_CLKP NBGFX_CLKN 1 3 *0_4P2R_4 EXT_GFX_CLKP EXT_GFX_CLKN 1

to NB for external Graphics reference clock to M82-S -RX780 only

C

+3V_CLKVDD

3 *0_4P2R_4 PCIE_MINI2_CLKP PCIE_MINI2_CLKN 1 3 *0_4P2R_4 CLK_PCIE_CARD CLK_PCIE_CARD# 1 T59 T62 3 1 3 1 3 1 3 1 3 1

PCIE_MINI2_CLKP 36 PCIE_MINI2_CLKN 36 CLK_PCIE_CARD 26 CLK_PCIE_CARD# 26

to TV TUNER CARD to PCIE-CARD READER

C

Del RP52 for NBGPP CLK*0_4P2R_4 PCIE_NEW_CLKP PCIE_NEW_CLKN *0_4P2R_4 PCIE_MINI1_CLKP PCIE_MINI1_CLKN *0_4P2R_4 SBLINK_CLKP SBLINK_CLKN *0_4P2R_4 SBSRC_CLKP SBSRC_CLKN *0_4P2R_4 PCIE_LAN_CLKP PCIE_LAN_CLKN 33_4 75/F_4 100/F_4 OSC_SPREAD PCIE_NEW_CLKP 33 PCIE_NEW_CLKN 33 PCIE_MINI1_CLKP 36 PCIE_MINI1_CLKN 36 SBLINK_CLKP 10 SBLINK_CLKN 10 SBSRC_CLKP 12 SBSRC_CLKN 12 PCIE_LAN_CLKP 31 PCIE_LAN_CLKN 31 OSC_SPREAD 18 EVGA-XTALI 18 NBHT_REFCLKP 10 NBHT_REFCLKN 10 CLK_48M_CR 25 CLK_48M_USB 13 T58 T167

RP51 RP49 RP47 RP45 RP44

+1.2V_CLKVDDIO C466 33P/50V_4 2 Y2 14.318MHZ 1 C465 33P/50V_4 CG_XOUT CG_XIN

4 2 4 2 4 2 4 2 4 2

to EPRESS CARD to WLAN to NB for AC-LINK reference clock to SB to PCIE-LAN to ROBSONSSIN - for M82 - 3.3V level input X_TALIN --for M82 -1.8V level input

R527 R215 R490 R193 R194 R201 R192 0_4 0_4 33_4 33_4

SI-1 Modified --remove

NBHT_REFCLKP NBHT_REFCLKN CLK_48M_CR CLK_48M_USB

can remove MOSFET level shift SB/clock gen / DDR2 is 3.3V/S0 6,7,13,28,36 PCLK_SMB power levelB

R186 R184 1

Ra

158/F_4 2 90.9/F_4 EXT_NB_OSC 10B

6,7,13,28,36 PDAT_SMB

PCLK_SMB PDAT_SMB

RbEXT_NWD_CLK_REQ# 33

14 CHIPSET_PCIE_SLOW_SB#

D17

1

SB_SRC_SLOW# 2 *CH501H-40PT L-F

41

SB_SRC_SLOW#

RX780

RS780 1.1V 158R 90.9R

when driven low SB_SRC clocks slow only supported with to reduced setpoint custom CG IC+3V C952 C953 C954 C955 C956 *10P/50V_4 *10P/50V_4 *10P/50V_4 *10P/50V_4 *10P/50V_4 EXT_NB_OSC CLK_48M_USB CLK_48M_CR EVGA-XTALI OSC_SPREAD R756 R757 R758 R759 *8.2K_4 *8.2K_4 *8.2K_4 *8.2K_4 CLKREQ0# CLKREQ2# CLKREQ3# CLKREQ4#

SLG8SP626VTR 73 74 75 THERMAL GND 77 76 78

eGND73 eGND74 eGND75

eGND77 eGND76 eGND78

Clock chip has internal serial terminations for differencial pairs, external resistors are reserved for debug purpose.

1.8V Ra Rb 82.5R 130R

U10B SLG8SP626VTR

+3V_CLKVDD

RES CHIP 130 1/16W +-1%(0402)L-F -->CS11302FB15 RES CHIP 158 1/16W +-1%(0402) -->CS11582FB00 RES CHIP 90.9 1/16W +-1%(0402) -->CS09092FB15 RES CHIP 82.5 1/16W +-1%(0402) -->CS08252FB11

if use clock request pin , need to pull Hi for default sttting

ICS SLG RTL

ICS9LPR476BKLFT--AJRS4760000 SLG8SP626VTR--AJ006260000 RTM880N-795-- AJ008800000* default 66 MHz 3.3V single ended HTT clock 1 R189 *8.2K_4 R195 8.2K_4 SEL_27 SEL_SATA SEL_HT66 R203 8.2K_4 R202 *8.2K_4 EXT_NWD_CLK_REQ# CLK_PD# SB_SRC_SLOW# 8.2K_4 8.2K_4 8.2K_4 R219 R204 R261

+3V

SI-1 modified -- reserve for EMTA

SEL_HTT66 0* SEL_SATA 1 0* SEL_27 1* 0 100 MHz spreading differential SRC clock 27MHz non-spreading singled clock 100 MHz spreading differential SRC clock 100 MHz differential HTT clock 100 MHz non-spreading differential SRC clock

A

RS780M/RX780MSize Custom NB5/RD5

PROJECT : QT8 Quanta Computer Inc.Document Number

Clock GeneratorSheet 2 of 451

Rev 1A

Date: Tuesday, February 19, 20085 4 3 2

5

4

3

2

1

BLM21PG221SN1D(220,100M,2A)_8 +2.5V +1.2V R474 R473 0_8 0_8 +1.2V_VLDT U31A C739 C744 C758 C753 4.7U/6.3V_6 4.7U/6.3V_6 0.22U/6.3V_4 180P/50V_4 +1.2V_VLDT +1.2V_VLDT +1.2V_VLDT +1.2V_VLDT D1 D2 D3 D4 E3 E2 E1 F1 G3 G2 G1 H1 J1 K1 L3 L2 L1 M1 N3 N2 E5 F5 F3 F4 G5 H5 H3 H4 K3 K4 L5 M5 M3 M4 N5 P5 J3 J2 J5 K5 N1 P1 P3 P4 VLDT_A0 VLDT_A1 VLDT_A2 VLDT_A3 +1.2V_VLDT +CPUVDDA L36 C416 LS0805-100M-N 10U/6.3V_8 C392 4.7U/6.3V_6

W/S= 15 mil/20mil CPU CLKC363 3300P/50V_4 CPUCLKP CPUCLKN +CPUVDDA

CPU_THERMDC CPU_THERMDA CPU_LDT_RST# CPU_LDT_STOP# CPU_PWRGD CPU_LDT_REQ#_CPU U31D F8 F9 A9 A8 B7 A7 F10 C6 AF4 AF5 AE6 R6 P6 F6 E6 Y6 AB6 CPU_DBRDY CPU_TMS CPU_TCK CPU_TRST# CPU_TDI T7 CPUTEST23 CPUTEST18 CPUTEST19 CPUTEST25H CPUTEST25L G10 AA9 AC9 AD9 AF9 AD7 H10 G9 E9 E8 AB8 AF7 AE7 AE8 AC8 AF8 C2 AA6 A3 A5 B3 B5 C1 VDDA1 VDDA2

R569 R567 300_4 300_4 300_4 300_4

0_4 0_4 R142 R140 R144 R563

H_THRMDC 5 H_THRMDA 5 +1.8V

C368 0.22U/6.3V_4

2 2

CPUCLKP CPUCLKN

Keep trace from resisor to CPU within 0.6" keep trace from caps to CPU within 1.2" HT LINK+1.2V_VLDT 4.7U/6.3V_6 +1.2V_VLDT 0.22U/6.3V_4 +1.2V_VLDT 180P/50V_4 +1.2V_VLDT HT_CPU_NB_CAD_H0 HT_CPU_NB_CAD_L0 HT_CPU_NB_CAD_H1 HT_CPU_NB_CAD_L1 HT_CPU_NB_CAD_H2 HT_CPU_NB_CAD_L2 HT_CPU_NB_CAD_H3 HT_CPU_NB_CAD_L3 HT_CPU_NB_CAD_H4 HT_CPU_NB_CAD_L4 HT_CPU_NB_CAD_H5 HT_CPU_NB_CAD_L5 HT_CPU_NB_CAD_H6 HT_CPU_NB_CAD_L6 HT_CPU_NB_CAD_H7 HT_CPU_NB_CAD_L7 HT_CPU_NB_CAD_H8 HT_CPU_NB_CAD_L8 HT_CPU_NB_CAD_H9 HT_CPU_NB_CAD_L9 HT_CPU_NB_CAD_H10 HT_CPU_NB_CAD_L10 HT_CPU_NB_CAD_H11 HT_CPU_NB_CAD_L11 HT_CPU_NB_CAD_H12 HT_CPU_NB_CAD_L12 HT_CPU_NB_CAD_H13 HT_CPU_NB_CAD_L13 HT_CPU_NB_CAD_H14 HT_CPU_NB_CAD_L14 HT_CPU_NB_CAD_H15 HT_CPU_NB_CAD_L15 HT_CPU_NB_CLK_H0 HT_CPU_NB_CLK_L0 HT_CPU_NB_CLK_H1 HT_CPU_NB_CLK_L1 HT_CPU_NB_CTL_H0 HT_CPU_NB_CTL_L0 HT_CPU_NB_CTL_H1 HT_CPU_NB_CTL_L1 C840 C818 C829 CPUCLKIN CPUCLKP CPUCLKN R137 C408 C409 169/F_4 CPUCLKIN#

SI-2 modified -confirm AMD R563 need to stuffM11 W18 A6 A4 CPU_SVC_R CPU_SVD_R

03D

D

VLDT_B0 VLDT_B1 VLDT_B2 VLDT_B3

AE2 AE3 AE4 AE5 AD1 AC1 AC2 AC3 AB1 AA1 AA2 AA3 W2 W3 V1 U1 U2 U3 T1 R1 AD4 AD3 AD5 AC5 AB4 AB3 AB5 AA5 Y5 W5 V4 V3 V5 U5 T4 T3 Y1 W1 Y4 Y3 R2 R3 T5 R5

W/S= 15 mil/20mil +CPUVDDA +CPUVDDA CPUCLKIN CPUCLKIN# CPU_LDT_RST# CPU_PWRGD CPU_LDT_STOP# CPU_LDT_REQ#_CPU CPU_SIC CPU_SID CPU_ALERT

KEY1 KEY2 SVC SVD

3900P/25V_4 3900P/25V_4

CLKIN_H CLKIN_L RESET_L PWROK LDTSTOP_L LDTREQ_L SIC SID ALERT_L HT_REF0 HT_REF1 VDD0_FB_H VDD0_FB_L VDD1_FB_H VDD1_FB_L DBRDY TMS TCK TRST_L TDI TEST23 TEST18 TEST19 TEST25_H TEST25_L TEST21 TEST20 TEST24 TEST22 TEST12 TEST27 TEST9 TEST6 RSVD1 RSVD2 RSVD3 RSVD4 RSVD5 SOCKET_638_PIN

8 HT_NB_CPU_CAD_H[15..0] 8 HT_NB_CPU_CAD_L[15..0] 8 HT_NB_CPU_CLK_H[1..0] 8 HT_NB_CPU_CLK_L[1..0] 8 HT_NB_CPU_CTL_H[1..0] 8 HT_NB_CPU_CTL_L[1..0] 8 HT_CPU_NB_CAD_H[15..0] 8 HT_CPU_NB_CAD_L[15..0] 8 HT_CPU_NB_CLK_H[1..0] 8 HT_CPU_NB_CLK_L[1..0]C

HT_NB_CPU_CAD_H[15..0] HT_NB_CPU_CAD_L[15..0] HT_NB_CPU_CLK_H[1..0] HT_NB_CPU_CLK_L[1..0] HT_NB_CPU_CTL_H[1..0] HT_NB_CPU_CTL_L[1..0] HT_CPU_NB_CAD_H[15..0] HT_CPU_NB_CAD_L[15..0] HT_CPU_NB_CLK_H[1..0] HT_CPU_NB_CLK_L[1..0] HT_CPU_NB_CTL_H[1..0] HT_CPU_NB_CTL_L[1..0]

8 HT_CPU_NB_CTL_H[1..0] 8 HT_CPU_NB_CTL_L[1..0]

HT_NB_CPU_CAD_H0 HT_NB_CPU_CAD_L0 HT_NB_CPU_CAD_H1 HT_NB_CPU_CAD_L1 HT_NB_CPU_CAD_H2 HT_NB_CPU_CAD_L2 HT_NB_CPU_CAD_H3 HT_NB_CPU_CAD_L3 HT_NB_CPU_CAD_H4 HT_NB_CPU_CAD_L4 HT_NB_CPU_CAD_H5 HT_NB_CPU_CAD_L5 HT_NB_CPU_CAD_H6 HT_NB_CPU_CAD_L6 HT_NB_CPU_CAD_H7 HT_NB_CPU_CAD_L7 HT_NB_CPU_CAD_H8 HT_NB_CPU_CAD_L8 HT_NB_CPU_CAD_H9 HT_NB_CPU_CAD_L9 HT_NB_CPU_CAD_H10 HT_NB_CPU_CAD_L10 HT_NB_CPU_CAD_H11 HT_NB_CPU_CAD_L11 HT_NB_CPU_CAD_H12 HT_NB_CPU_CAD_L12 HT_NB_CPU_CAD_H13 HT_NB_CPU_CAD_L13 HT_NB_CPU_CAD_H14 HT_NB_CPU_CAD_L14 HT_NB_CPU_CAD_H15 HT_NB_CPU_CAD_L15 HT_NB_CPU_CLK_H0 HT_NB_CPU_CLK_L0 HT_NB_CPU_CLK_H1 HT_NB_CPU_CLK_L1 HT_NB_CPU_CTL_H0 HT_NB_CPU_CTL_L0 HT_NB_CPU_CTL_H1 HT_NB_CPU_CTL_L1

L0_CADIN_H0 L0_CADIN_L0 L0_CADIN_H1 L0_CADIN_L1 L0_CADIN_H2 L0_CADIN_L2 L0_CADIN_H3 L0_CADIN_L3 L0_CADIN_H4 L0_CADIN_L4 L0_CADIN_H5 L0_CADIN_L5 L0_CADIN_H6 L0_CADIN_L6 L0_CADIN_H7 L0_CADIN_L7 L0_CADIN_H8 L0_CADIN_L8 L0_CADIN_H9 L0_CADIN_L9 L0_CADIN_H10 L0_CADIN_L10 L0_CADIN_H11 L0_CADIN_L11 L0_CADIN_H12 L0_CADIN_L12 L0_CADIN_H13 L0_CADIN_L13 L0_CADIN_H14 L0_CADIN_L14 L0_CADIN_H15 L0_CADIN_L15 L0_CLKIN_H0 L0_CLKIN_L0 L0_CLKIN_H1 L0_CLKIN_L1 L0_CTLIN_H0 L0_CTLIN_L0 L0_CTLIN_H1 L0_CTLIN_L1 SOCKET_638_PIN

L0_CADOUT_H0 L0_CADOUT_L0 L0_CADOUT_H1 L0_CADOUT_L1 L0_CADOUT_H2 L0_CADOUT_L2 L0_CADOUT_H3 L0_CADOUT_L3 L0_CADOUT_H4 L0_CADOUT_L4 L0_CADOUT_H5 L0_CADOUT_L5 L0_CADOUT_H6 L0_CADOUT_L6 L0_CADOUT_H7 L0_CADOUT_L7 L0_CADOUT_H8 L0_CADOUT_L8 L0_CADOUT_H9 L0_CADOUT_L9 L0_CADOUT_H10 L0_CADOUT_L10 L0_CADOUT_H11 L0_CADOUT_L11 L0_CADOUT_H12 L0_CADOUT_L12 L0_CADOUT_H13 L0_CADOUT_L13 L0_CADOUT_H14 L0_CADOUT_L14 L0_CADOUT_H15 L0_CADOUT_L15 L0_CLKOUT_H0 L0_CLKOUT_L0 L0_CLKOUT_H1 L0_CLKOUT_L1 L0_CTLOUT_H0 L0_CTLOUT_L0 L0_CTLOUT_H1 L0_CTLOUT_L1

10,12 CPU_LDT_RST# 12 CPU_PWRGD 10,12 CPU_LDT_STOP# 5 CPU_SIC CPU_SID CPU_ALERT R128 R135

THERMTRIP_L PROCHOT_L MEMHOT_L THERMDC THERMDA

AF6 AC7 AA8 W7 W8

CPU_THERMTRIP_L# CPU_PROCHOT_L# CPU_MEMHOT_L# CPU_THERMDC CPU_THERMDA

SideBand Temp sense I2C 55 +1.2V_VLDT

CPU_HTREF0 44.2/F_4 44.2/F_4 CPU_HTREF1 place them to CPU within 1.5"

40 CPU_VDD0_RUN_FB_H 40 CPU_VDD0_RUN_FB_L 40 CPU_VDD1_RUN_FB_H 40 CPU_VDD1_RUN_FB_L

VDDIO_FB_H VDDIO_FB_L VDDNB_FB_H VDDNB_FB_L DBREQ_L TDO TEST28_H TEST28_L TEST17 TEST16 TEST15 TEST14 TEST7 TEST10 TEST8 TEST29_H TEST29_L RSVD10 RSVD9 RSVD8 RSVD7 RSVD6

W9 Y9 H6 G6 E10

VDDIO_FB_H VDDIO_FB_L

VDDIO_FB_H 41 VDDIO_FB_L 41

CPU_VDDNB_RUN_FB_H 40 CPU_VDDNB_RUN_FB_L 40 CPU_DBREQ# R775 300/F_4 +1.8VSUS

AE9 CPU_TDO J7 H8 D7 E7 F7 C7 C3 K8 C4 C9 C8 H18 H19 AA7 D5 C5 CPUTEST29H CPUTEST29L CPUTEST28H CPUTEST28L CPUTEST17 CPUTEST16 CPUTEST15 CPUTEST14

SI-2 modified for AMD sighting update+1.8VSUS R776 R777 +1.8VSUS R455 300_4 R535 R141 R108 300/F_4 300/F_4

T40 T43 T48 T46 T44 T49

T42 T45 510/F_4 510/F_4

SI-2 modified for AMD sighting update

C

T116 T118 T9 0_4

CPUTEST21 CPUTEST20 CPUTEST24 CPUTEST22 CPUTEST12 CPUTEST27

T47 T50

FOX PZ63826-284R-41F DG0^8000004 IC SOCKET SMD 638P S1(P1.27,H3.2) MLX 47296-4131 DG0^8000003 IC SOCKET SMD 638P S1(P1.27,H3.2) TYC 4-1903401-2 DG0^8000005 IC SOCKET SMD 638P S1(P1.27,H3.2)

CNTR_VREF C854B

CNTR_VREF 5 0.1U/10V_4 34.8K/F_4 +3V

Serial VID+1.8VSUS R145 R561 R562 R554 R553 R147 R560 R559 C926 *2.2K_4 1K/F_4 1K/F_4 0_4 0_4 0_4 *220_4 *220_4 *0.1U/10V_4 CPU_SVC CPU_SVD CPU_PWRGD_SVID_REG CPU_SVC 40 CPU_SVD 40 CPU_PWRGD_SVID_REG R577 1K/F_4 CPU_SVC_R CPU_SVD_R CPU_PWRGD

VFIX MODE SVC SVD

VID Override CircuitVoltage OutputB

+3V

R571

20K/F_4

R574

CNTR_VREF 2 R143 0_4 CPU_LDT_REQ# 10 CPU_LDT_RST# 1 2

40

Q39 CPU_LDT_REQ#_CPU 1

*BSS138_NL/SOT23 3

CPU_LDT_RST_HTPA# 3 Q40 BSS138_NL/SOT23

0 0 1 1

0 1 0 1

1.4V 1.2V 1.0V 0.8V

R570

0_4

1

G1 *SHORT_ PAD1

SI-2 remove for power up seq

+1.8VSUS +1.8VSUS

R59 R62

10K/F_4 2 300_4 3 Q11 MMBT3904 CPU_MEMHOT# 1

2

for debug onlyCPUTEST20 CPUTEST22 CPUTEST12 CPUTEST15 CPUTEST14 CPUTEST19 CPUTEST18 2 4 6 8 10 12 14 16 18 20 22 24 25 R798 R799 R800 R801 R802 R803 R804 *300/F_4 *300/F_4 *300/F_4 *300/F_4 *300/F_4 *300/F_4 *300/F_4

CPU_MEMHOT_L#

CPU_MEMHOT# 7,13

HDT Connector+1.8VSUS 1 3 5 7 9 11 13 15 17 19 21 23KEY

A

+1.8VSUS +1.8VSUS

R453 R452

10K/F_4 300_4

+1.8VSUS +1.8VSUS 2 Q35

R60 R454

10K/F_4 300_4 CPU_DBREQ# CPU_DBRDY CPU_TCK CPU_TMS CPU_TDI CPU_TRST# CPU_TDO C54 *0.1U/10V_4

SI-2 reserve for AMD recommend

A

2

CPU_THERMTRIP_L# CPU_PROCHOT_L# 1 3 MMBT3904 CPU_PROCHOT# 12

1

Q10 MMBT3904 3

CPU_THERMTRIP# 13

CPU_LDT_RST_HTPA# Size Custom NB5/RD52

PROJECT : QT8 Quanta Computer Inc.Document Number

CN6 *HDT CONN5 4 3

S1G2 HT,CTL I/F 1/3Sheet 3 of 451

Rev 1A

Date: Tuesday, February 19, 2008

A

B

C

D

E

+0.9VSMVTT

U31B D10 C10 B10 AD10 VTT1 VTT2 VTT3 VTT4 MEMZP MEMZN RSVD_M1 MA0_ODT0 MA0_ODT1 MA1_ODT0 MA1_ODT1 MA0_CS_L0 MA0_CS_L1 MA1_CS_L0 MA1_CS_L1 MA_CKE0 MA_CKE1 MA_CLK_H5 MA_CLK_L5 MA_CLK_H1 MA_CLK_L1 MA_CLK_H7 MA_CLK_L7 MA_CLK_H4 MA_CLK_L4 MA_ADD0 MA_ADD1 MA_ADD2 MA_ADD3 MA_ADD4 MA_ADD5 MA_ADD6 MA_ADD7 MA_ADD8 MA_ADD9 MA_ADD10 MA_ADD11 MA_ADD12 MA_ADD13 MA_ADD14 MA_ADD15 MA_BANK0 MA_BANK1 MA_BANK2 MA_RAS_L MA_CAS_L MA_WE_L SOCKET_638_PIN MEM:CMD/CTRL/CLK VTT5 VTT6 VTT7 VTT8 VTT9 VTT_SENSE MEMVREF RSVD_M2 MB0_ODT0 MB0_ODT1 MB1_ODT0 MB0_CS_L0 MB0_CS_L1 MB1_CS_L0 MB_CKE0 MB_CKE1 MB_CLK_H5 MB_CLK_L5 MB_CLK_H1 MB_CLK_L1 MB_CLK_H7 MB_CLK_L7 MB_CLK_H4 MB_CLK_L4 MB_ADD0 MB_ADD1 MB_ADD2 MB_ADD3 MB_ADD4 MB_ADD5 MB_ADD6 MB_ADD7 MB_ADD8 MB_ADD9 MB_ADD10 MB_ADD11 MB_ADD12 MB_ADD13 MB_ADD14 MB_ADD15 MB_BANK0 MB_BANK1 MB_BANK2 MB_RAS_L MB_CAS_L MB_WE_L W10 AC10 AB10 AA10 A10

+0.9VSMVTT +1.8VSUS 6 MEM_MB_DATA[0..63] +0.9VSMVREF 6,41 R81 2K/F_4 CPU_VTT_SENSE 41 R82 *0_4 Reserved

Processor Memory InterfaceU31C MEM:DATA MEM_MB_DATA0 MEM_MB_DATA1 MEM_MB_DATA2 MEM_MB_DATA3 MEM_MB_DATA4 MEM_MB_DATA5 MEM_MB_DATA6 MEM_MB_DATA7 MEM_MB_DATA8 MEM_MB_DATA9 MEM_MB_DATA10 MEM_MB_DATA11 MEM_MB_DATA12 MEM_MB_DATA13 MEM_MB_DATA14 MEM_MB_DATA15 MEM_MB_DATA16 MEM_MB_DATA17 MEM_MB_DATA18 MEM_MB_DATA19 MEM_MB_DATA20 MEM_MB_DATA21 MEM_MB_DATA22 MEM_MB_DATA23 MEM_MB_DATA24 MEM_MB_DATA25 MEM_MB_DATA26 MEM_MB_DATA27 MEM_MB_DATA28 MEM_MB_DATA29 MEM_MB_DATA30 MEM_MB_DATA31 MEM_MB_DATA32 MEM_MB_DATA33 MEM_MB_DATA34 MEM_MB_DATA35 MEM_MB_DATA36 MEM_MB_DATA37 MEM_MB_DATA38 MEM_MB_DATA39 MEM_MB_DATA40 MEM_MB_DATA41 MEM_MB_DATA42 MEM_MB_DATA43 MEM_MB_DATA44 MEM_MB_DATA45 MEM_MB_DATA46 MEM_MB_DATA47 MEM_MB_DATA48 MEM_MB_DATA49 MEM_MB_DATA50 MEM_MB_DATA51 MEM_MB_DATA52 MEM_MB_DATA53 MEM_MB_DATA54 MEM_MB_DATA55 MEM_MB_DATA56 MEM_MB_DATA57 MEM_MB_DATA58 MEM_MB_DATA59 MEM_MB_DATA60 MEM_MB_DATA61 MEM_MB_DATA62 MEM_MB_DATA63 MEM_MB_DM0 MEM_MB_DM1 MEM_MB_DM2 MEM_MB_DM3 MEM_MB_DM4 MEM_MB_DM5 MEM_MB_DM6 MEM_MB_DM7 C11 A11 A14 B14 G11 E11 D12 A13 A15 A16 A19 A20 C14 D14 C18 D18 D20 A21 D24 C25 B20 C20 B24 C24 E23 E24 G25 G26 C26 D26 G23 G24 AA24 AA23 AD24 AE24 AA26 AA25 AD26 AE25 AC22 AD22 AE20 AF20 AF24 AF23 AC20 AD20 AD18 AE18 AC14 AD14 AF19 AC18 AF16 AF15 AF13 AC12 AB11 Y11 AE14 AF14 AF11 AD11 A12 B16 A22 E25 AB26 AE22 AC16 AD12 C12 B12 D16 C16 A24 A23 F26 E26 AC25 AC26 AF21 AF22 AE16 AD16 AF12 AE12 MB_DATA0 MB_DATA1 MB_DATA2 MB_DATA3 MB_DATA4 MB_DATA5 MB_DATA6 MB_DATA7 MB_DATA8 MB_DATA9 MB_DATA10 MB_DATA11 MB_DATA12 MB_DATA13 MB_DATA14 MB_DATA15 MB_DATA16 MB_DATA17 MB_DATA18 MB_DATA19 MB_DATA20 MB_DATA21 MB_DATA22 MB_DATA23 MB_DATA24 MB_DATA25 MB_DATA26 MB_DATA27 MB_DATA28 MB_DATA29 MB_DATA30 MB_DATA31 MB_DATA32 MB_DATA33 MB_DATA34 MB_DATA35 MB_DATA36 MB_DATA37 MB_DATA38 MB_DATA39 MB_DATA40 MB_DATA41 MB_DATA42 MB_DATA43 MB_DATA44 MB_DATA45 MB_DATA46 MB_DATA47 MB_DATA48 MB_DATA49 MB_DATA50 MB_DATA51 MB_DATA52 MB_DATA53 MB_DATA54 MB_DATA55 MB_DATA56 MB_DATA57 MB_DATA58 MB_DATA59 MB_DATA60 MB_DATA61 MB_DATA62 MB_DATA63 MB_DM0 MB_DM1 MB_DM2 MB_DM3 MB_DM4 MB_DM5 MB_DM6 MB_DM7 MB_DQS_H0 MB_DQS_L0 MB_DQS_H1 MB_DQS_L1 MB_DQS_H2 MB_DQS_L2 MB_DQS_H3 MB_DQS_L3 MB_DQS_H4 MB_DQS_L4 MB_DQS_H5 MB_DQS_L5 MB_DQS_H6 MB_DQS_L6 MB_DQS_H7 MB_DQS_L7 SOCKET_638_PIN MA_DATA0 MA_DATA1 MA_DATA2 MA_DATA3 MA_DATA4 MA_DATA5 MA_DATA6 MA_DATA7 MA_DATA8 MA_DATA9 MA_DATA10 MA_DATA11 MA_DATA12 MA_DATA13 MA_DATA14 MA_DATA15 MA_DATA16 MA_DATA17 MA_DATA18 MA_DATA19 MA_DATA20 MA_DATA21 MA_DATA22 MA_DATA23 MA_DATA24 MA_DATA25 MA_DATA26 MA_DATA27 MA_DATA28 MA_DATA29 MA_DATA30 MA_DATA31 MA_DATA32 MA_DATA33 MA_DATA34 MA_DATA35 MA_DATA36 MA_DATA37 MA_DATA38 MA_DATA39 MA_DATA40 MA_DATA41 MA_DATA42 MA_DATA43 MA_DATA44 MA_DATA45 MA_DATA46 MA_DATA47 MA_DATA48 MA_DATA49 MA_DATA50 MA_DATA51 MA_DATA52 MA_DATA53 MA_DATA54 MA_DATA55 MA_DATA56 MA_DATA57 MA_DATA58 MA_DATA59 MA_DATA60 MA_DATA61 MA_DATA62 MA_DATA63 MA_DM0 MA_DM1 MA_DM2 MA_DM3 MA_DM4 MA_DM5 MA_DM6 MA_DM7 MA_DQS_H0 MA_DQS_L0 MA_DQS_H1 MA_DQS_L1 MA_DQS_H2 MA_DQS_L2 MA_DQS_H3 MA_DQS_L3 MA_DQS_H4 MA_DQS_L4 MA_DQS_H5 MA_DQS_L5 MA_DQS_H6 MA_DQS_L6 MA_DQS_H7 MA_DQS_L7 G12 F12 H14 G14 H11 H12 C13 E13 H15 E15 E17 H17 E14 F14 C17 G17 G18 C19 D22 E20 E18 F18 B22 C23 F20 F22 H24 J19 E21 E22 H20 H22 Y24 AB24 AB22 AA21 W22 W21 Y22 AA22 Y20 AA20 AA18 AB18 AB21 AD21 AD19 Y18 AD17 W16 W14 Y14 Y17 AB17 AB15 AD15 AB13 AD13 Y12 W11 AB14 AA14 AB12 AA12 E12 C15 E19 F24 AC24 Y19 AB16 Y13 G13 H13 G16 G15 C22 C21 G22 G21 AD23 AC23 AB19 AB20 Y15 W15 W12 W13 MEM_MA_DATA0 MEM_MA_DATA1 MEM_MA_DATA2 MEM_MA_DATA3 MEM_MA_DATA4 MEM_MA_DATA5 MEM_MA_DATA6 MEM_MA_DATA7 MEM_MA_DATA8 MEM_MA_DATA9 MEM_MA_DATA10 MEM_MA_DATA11 MEM_MA_DATA12 MEM_MA_DATA13 MEM_MA_DATA14 MEM_MA_DATA15 MEM_MA_DATA16 MEM_MA_DATA17 MEM_MA_DATA18 MEM_MA_DATA19 MEM_MA_DATA20 MEM_MA_DATA21 MEM_MA_DATA22 MEM_MA_DATA23 MEM_MA_DATA24 MEM_MA_DATA25 MEM_MA_DATA26 MEM_MA_DATA27 MEM_MA_DATA28 MEM_MA_DATA29 MEM_MA_DATA30 MEM_MA_DATA31 MEM_MA_DATA32 MEM_MA_DATA33 MEM_MA_DATA34 MEM_MA_DATA35 MEM_MA_DATA36 MEM_MA_DATA37 MEM_MA_DATA38 MEM_MA_DATA39 MEM_MA_DATA40 MEM_MA_DATA41 MEM_MA_DATA42 MEM_MA_DATA43 MEM_MA_DATA44 MEM_MA_DATA45 MEM_MA_DATA46 MEM_MA_DATA47 MEM_MA_DATA48 MEM_MA_DATA49 MEM_MA_DATA50 MEM_MA_DATA51 MEM_MA_DATA52 MEM_MA_DATA53 MEM_MA_DATA54 MEM_MA_DATA55 MEM_MA_DATA56 MEM_MA_DATA57 MEM_MA_DATA58 MEM_MA_DATA59 MEM_MA_DATA60 MEM_MA_DATA61 MEM_MA_DATA62 MEM_MA_DATA63 MEM_MA_DM0 MEM_MA_DM1 MEM_MA_DM2 MEM_MA_DM3 MEM_MA_DM4 MEM_MA_DM5 MEM_MA_DM6 MEM_MA_DM7

PLACE THEM CLOSE TO CPU WITHIN 1"R459 R458 T414

750 mA

04MEM_MA_DATA[0..63] 64

+1.8VSUS

39.2/F_4 M_ZP 39.2/F_4 M_ZN

AF10 AE10

Y10 CPU_VTT_SENSE W17 MEMVREF_CPU B18 MEM_MB_RESET# W26 W23 Y26 V26 W25 U22 J25 H26 P22 R22 A17 A18 AF18 AF17 R26 R25 P24 N24 P26 N23 N26 L23 N25 L24 M26 K26 T26 L26 L25 W24 J23 J24 R24 U26 J26 U25 U24 U23 MEM_MB_ADD0 MEM_MB_ADD1 MEM_MB_ADD2 MEM_MB_ADD3 MEM_MB_ADD4 MEM_MB_ADD5 MEM_MB_ADD6 MEM_MB_ADD7 MEM_MB_ADD8 MEM_MB_ADD9 MEM_MB_ADD10 MEM_MB_ADD11 MEM_MB_ADD12 MEM_MB_ADD13 MEM_MB_ADD14 MEM_MB_ADD15

MEM_MA_RESET# H16 T19 V22 U21 V19 T20 U19 U20 V20 J22 J20 N19 N20 E16 F16 Y16 AA16 P19 P20 MEM_MA_ADD0 MEM_MA_ADD1 MEM_MA_ADD2 MEM_MA_ADD3 MEM_MA_ADD4 MEM_MA_ADD5 MEM_MA_ADD6 MEM_MA_ADD7 MEM_MA_ADD8 MEM_MA_ADD9 MEM_MA_ADD10 MEM_MA_ADD11 MEM_MA_ADD12 MEM_MA_ADD13 MEM_MA_ADD14 MEM_MA_ADD15 N21 M20 N22 M19 M22 L20 M24 L21 L19 K22 R21 L22 K20 V24 K24 K19 R20 R23 J21 R19 T22 T24

6,7 MEM_MA0_ODT0 6,7 MEM_MA0_ODT1

T51 R77 MEM_MB0_ODT0 6,7 2K/F_4 MEM_MB0_ODT1 6,7 MEM_MB0_CS#0 6,7 MEM_MB0_CS#1 6,7 MEM_MB_CKE0 6,7 MEM_MB_CKE1 6,7 C197 0.1U/10V_4 C177 1000P/50V_4

6,7 MEM_MA0_CS#0 6,7 MEM_MA0_CS#1

6,7 MEM_MA_CKE0 6,7 MEM_MA_CKE1

6 6 6 6

MEM_MA_CLK1_P MEM_MA_CLK1_N MEM_MA_CLK7_P MEM_MA_CLK7_N

MEM_MB_CLK1_P MEM_MB_CLK1_N MEM_MB_CLK7_P MEM_MB_CLK7_N

6 6 6 6

6,7 MEM_MA_ADD[0..15]

MEM_MB_ADD[0..15] 6,7

3

3

6,7 MEM_MA_BANK0 6,7 MEM_MA_BANK1 6,7 MEM_MA_BANK2 6,7 MEM_MA_RAS# 6,7 MEM_MA_CAS# 6,7 MEM_MA_WE#

MEM_MB_BANK0 6,7 MEM_MB_BANK1 6,7 MEM_MB_BANK2 6,7 MEM_MB_RAS# 6,7 MEM_MB_CAS# 6,7 MEM_MB_WE# 6,7

2

+0.9VSMVTT

Place close to socketC399 4.7U/6.3V_6 C99 4.7U/6.3V_6 C398 4.7U/6.3V_6 C213 0.22U/6.3V_4 C369 0.22U/6.3V_4 C364 0.22U/6.3V_4

6 MEM_MB_DM[0..7]

MEM_MA_DM[0..7] 62

C112 4.7U/6.3V_6

C201 0.22U/6.3V_4

+0.9VSMVTT

C401 C202 1000P/50V_4 1000P/50V_4

C400 1000P/50V_4

C185 1000P/50V_4

C183 180P/50V_4

C189 180P/50V_4

C390 180P/50V_4

C396 180P/50V_4

Close to CPU within 1500 milsMEM_MA_CLK7_P MEM_MB_CLK7_P C736 1.5P/50V_4 MEM_MA_CLK7_N MEM_MB_CLK7_N MEM_MA_CLK1_P MEM_MB_CLK1_P C366 1.5P/50V_4 MEM_MA_CLK1_N MEM_MB_CLK1_N C367 1.5P/50V_4 C734 1.5P/50V_4

6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6

MEM_MB_DQS0_P MEM_MB_DQS0_N MEM_MB_DQS1_P MEM_MB_DQS1_N MEM_MB_DQS2_P MEM_MB_DQS2_N MEM_MB_DQS3_P MEM_MB_DQS3_N MEM_MB_DQS4_P MEM_MB_DQS4_N MEM_MB_DQS5_P MEM_MB_DQS5_N MEM_MB_DQS6_P MEM_MB_DQS6_N MEM_MB_DQS7_P MEM_MB_DQS7_N

MEM_MA_DQS0_P MEM_MA_DQS0_N MEM_MA_DQS1_P MEM_MA_DQS1_N MEM_MA_DQS2_P MEM_MA_DQS2_N MEM_MA_DQS3_P MEM_MA_DQS3_N MEM_MA_DQS4_P MEM_MA_DQS4_N MEM_MA_DQS5_P MEM_MA_DQS5_N MEM_MA_DQS6_P MEM_MA_DQS6_N MEM_MA_DQS7_P MEM_MA_DQS7_N

6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6

1

1

PROJECT : QT8 Quanta Computer Inc.Size Custom NB5/RD5 Document Number

S1G2 DDRII MEMORY I/F 2/3Sheet 4 of 45E

Rev 1A

Date: Tuesday, February 19, 2008A B C D

5

4

3

2

1

U31F U31E G4 H2 J9 J11 J13 J15 K6 K10 K12 K14 L4 L7 L9 L11 L13 L15 M2 M6 M8 M10 N7 N9 N11 K16 M16 P16 T16 V16 H25 J17 K18 K21 K23 K25 L17 M18 M21 M23 M25 N17 VDD0_1 VDD0_2 VDD0_3 VDD0_4 VDD0_5 VDD0_6 VDD0_7 VDD0_8 VDD0_9 VDD0_10 VDD0_11 VDD0_12 VDD0_13 VDD0_14 VDD0_15 VDD0_16 VDD0_17 VDD0_18 VDD0_19 VDD0_20 VDD0_21 VDD0_22 VDD0_23 VDDNB_1 VDDNB_2 VDDNB_3 VDDNB_4 VDDNB_5 VDDIO1 VDDIO2 VDDIO3 VDDIO4 VDDIO5 VDDIO6 VDDIO7 VDDIO8 VDDIO9 VDDIO10 VDDIO11 VDDIO12 VDD1_1 VDD1_2 VDD1_3 VDD1_4 VDD1_5 VDD1_6 VDD1_7 VDD1_8 VDD1_9 VDD1_10 VDD1_11 VDD1_12 VDD1_13 VDD1_14 VDD1_15 VDD1_16 VDD1_17 VDD1_18 VDD1_19 VDD1_20 VDD1_21 VDD1_22 VDD1_23 VDD1_24 VDD1_25 VDD1_26 VDDIO27 VDDIO26 VDDIO25 VDDIO24 VDDIO23 VDDIO22 VDDIO21 VDDIO20 VDDIO19 VDDIO18 VDDIO17 VDDIO16 VDDIO15 VDDIO14 VDDIO13 P8 P10 R4 R7 R9 R11 T2 T6 T8 T10 T12 T14 U7 U9 U11 U13 U15 V6 V8 V10 V12 V14 W4 Y2 AC4 AD2 Y25 V25 V23 V21 V18 U17 T25 T23 T21 T18 R17 P25 P23 P21 P18 AA4 AA11 AA13 AA15 AA17 AA19 AB2 AB7 AB9 AB23 AB25 AC11 AC13 AC15 AC17 AC19 AC21 AD6 AD8 AD25 AE11 AE13 AE15 AE17 AE19 AE21 AE23 B4 B6 B8 B9 B11 B13 B15 B17 B19 B21 B23 B25 D6 D8 D9 D11 D13 D15 D17 D19 D21 D23 D25 E4 F2 F11 F13 F15 F17 F19 F21 F23 F25 H7 H9 H21 H23 J4 VSS1 VSS2 VSS3 VSS4 VSS5 VSS6 VSS7 VSS8 VSS9 VSS10 VSS11 VSS12 VSS13 VSS14 VSS15 VSS16 VSS17 VSS18 VSS19 VSS20 VSS21 VSS22 VSS23 VSS24 VSS25 VSS26 VSS27 VSS28 VSS29 VSS30 VSS31 VSS32 VSS33 VSS34 VSS35 VSS36 VSS37 VSS38 VSS39 VSS40 VSS41 VSS42 VSS43 VSS44 VSS45 VSS46 VSS47 VSS48 VSS49 VSS50 VSS51 VSS52 VSS53 VSS54 VSS55 VSS56 VSS57 VSS58 VSS59 VSS60 VSS61 VSS62 VSS63 VSS64 VSS65 SOCKET_638_PIN VSS66 VSS67 VSS68 VSS69 VSS70 VSS71 VSS72 VSS73 VSS74 VSS75 VSS76 VSS77 VSS78 VSS79 VSS80 VSS81 VSS82 VSS83 VSS84 VSS85 VSS86 VSS87 VSS88 VSS89 VSS90 VSS91 VSS92 VSS93 VSS94 VSS95 VSS96 VSS97 VSS98 VSS99 VSS100 VSS101 VSS102 VSS103 VSS104 VSS105 VSS106 VSS107 VSS108 VSS109 VSS110 VSS111 VSS112 VSS113 VSS114 VSS115 VSS116 VSS117 VSS118 VSS119 VSS120 VSS121 VSS122 VSS123 VSS124 VSS125 VSS126 VSS127 VSS128 VSS129 J6 J8 J10 J12 J14 J16 J18 K2 K7 K9 K11 K13 K15 K17 L6 L8 L10 L12 L14 L16 L18 M7 M9 AC6 M17 N4 N8 N10 N16 N18 P2 P7 P9 P11 P17 R8 R10 R16 R18 T7 T9 T11 T13 T15 T17 U4 U6 U8 U10 U12 U14 U16 U18 V2 V7 V9 V11 V13 V15 V17 W6 Y21 Y23 N6

+VCORE0

+VCORE1

+VCORE0

05BOTTOM SIDE DECOUPLINGC308 22U/6.3V_8 C307 22U/6.3V_8 C306 22U/6.3V_8 C285 0.22U/6.3V_4 C286 0.01U/16V_4 C301 180P/50V_4D

C287 22U/6.3V_8

D

+VCORE1

C230 22U/6.3V_8

C272 22U/6.3V_8

C273 22U/6.3V_8

C267 22U/6.3V_8

C206 0.22U/6.3V_4

C226 C205 0.01U/16V_4 180P/50V_4

C225 0.01U/16V_4

+CPUVDDNB

+1.8VSUS

+CPUVDDNB

3A

+1.8VSUS

C264 22U/6.3V_8

C231 C279 22U/6.3V_8 22U/6.3V_8

C248 22U/6.3V_8

C284 22U/6.3V_8

C309 C247 0.22U/6.3V_4 0.22U/6.3V_4

C214 180P/50V_4

C315 180P/50V_4

+1.8VSUS

2A

C

C

DECOUPLING BETWEEN PROCESSOR AND DIMMs PLACE CLOSE TO PROCESSOR AS POSSIBLE+1.8VSUS

SOCKET_638_PIN +1.8VSUS

3 CNTR_VREF R164 390_4 2 R166 390_4 R167 1K/F_4

C750 4.7U/6.3V_6 +1.8VSUS

C802 4.7U/6.3V_6

C236 4.7U/6.3V_6

C749 4.7U/6.3V_6

C803 0.22U/6.3V_4

C240 0.22U/6.3V_4

18,35

MBCLK2

MBCLK2

3

Q14 1 2 Q15 1 2 Q13 1

CPU_SIC

CPU_SIC 3

C238 C751 C752 C120 0.22U/6.3V_4 0.22U/6.3V_4 0.01U/16V_4 0.01U/16V_4

C118 180P/50V_4

*BSS138_NL/SOT23 18,35 MBDATA2 MBDATA2 3

CPU_SID

CPU_SID 3

*BSS138_NL/SOT23B

SMBALERT#

3 *BSS138_NL/SOT23

CPU_ALERT

B

CPU_ALERT 3

PROCESSOR POWER AND GROUND+3V +3V +VCORE0 R572 200/F_6 +1.8VSUS EC10 EC5 EC4 EC7 EC1 EC2 EC8 EC9 CH501H-40PT R172 3 10K/F_4 +3V +3VS5 R760 2 *10K/F_4 TEMP_FAIL 18 EC13 EC14 EC11 EC12 Size Custom *0.1U/10V_43

+VCORE1 C69 C71 0.01U/16V_4 0.01U/16V_4 0.01U/16V_4 0.01U/16V_4

0.01U/16V_4 0.01U/16V_4 0.01U/16V_4 0.01U/16V_4 *0.01U/16V_4 *0.01U/16V_4 0.01U/16V_4 0.01U/16V_4

+3VPCU +3VPCU

R149 10K/F_4

R151 10K/F_4

R148 10K/F_4

Update U36 P/N on PV

R170

*0_4 1

SYS_SHDN#

SYS_SHDN#

38,44 +1.8V

Del R150, R152 on PVU36 18,35 18,35 MBCLK2 MBDATA2 8 7 6 13 PM_THERM#A

C856 0.1U/10V_4

reserve for power shutdown ( if can )

C67 C64

D34 *CH500H

+1.8V +3VPCU +5V 3920_RST# 35,44

+3V +3V +1.8VSUS +3V +5V +1.8V

2

EC3 EC6

0.01U/16V_4 0.01U/16V_4

SCLK SDA ALERT# OVERT#

VCC DXP DXN GND

1 2 3 5 C855 2200P/50V_4

+5V +3VPCU

H_THRMDA 3 Q16 3

R168 MMBT3904 2

0_4 D33 2 1

3920_RST#

4

H_THRMDC 3 1

ECPWROK

ECPWROK 16,35

+VGA_CORE

MSOP

For fix HyperTransport nets across plane splits

A

SI-2 Modified for H/W thermal shutdown+1.8VSUS +1.8VSUS R805 R806 *10K/F_4 *300_4

G781P8

SMBALERT#

+3VS5

+3V

+1.8V

PQ60 Q71 *MMBT3904 3 *2N7002E-G SMBALERT# 1

2

PROJECT : QT8 Quanta Computer Inc.Document Number NB5/RD5

CPU_THERMTRIP_L#

CPU_THERMTRIP_L#

1

ADD VGA TEMP_ FAIL function M8X is active Hi , M7X acvite Low*0.1U/10V_4 *0.1U/10V_42

*0.1U/10V_4

S1G2 PWR & GND 3/3Sheet1

Rev 1A 5 of 45

Date: Tuesday, February 19, 2008

5

4

5

4

3

2

1

+1.8VSUS 81 82 87 88 95 96 103 104 111 112 117 118 4,7 MEM_MA_ADD[0..15] MEM_MA_ADD0 MEM_MA_ADD1 MEM_MA_ADD2 MEM_MA_ADD3 MEM_MA_ADD4 MEM_MA_ADD5 MEM_MA_ADD6 MEM_MA_ADD7 MEM_MA_ADD8 MEM_MA_ADD9 MEM_MA_ADD10 MEM_MA_ADD11 MEM_MA_ADD12 MEM_MA_ADD13 MEM_MA_ADD14 MEM_MA_ADD15 102 101 100 99 98 97 94 92 93 91 105 90 89 116 86 84 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 BA0 BA1 BA2 DM0 DM1 DM2 DM3 DM4 DM5 DM6 DM7 DQS0 DQS1 DQS2 DQS3 DQS4 DQS5 DQS6 DQS7 DQS0 DQS1 DQS2 DQS3 DQS4 DQS5 DQS6 DQS7 CK0 CK0 CK1 CK1 CKE0 CKE1 RAS CAS WE S0 S1 ODT0 ODT1 SA0 SA1 SDA SCL VDDspd VREF VSS0 VSS1 VSS2 VSS3 VSS4 VSS5 VSS6 VSS7 VSS8 VSS9 VSS10 VSS11 VSS12 VSS13 VSS14 VSS15 VSS16 VSS17 VSS18 VSS19 VSS20 GND GND 201 202 CN30 DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 DQ16 DQ17 DQ18 DQ19 DQ20 DQ21 DQ22 DQ23 DQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31 DQ32 DQ33 DQ34 DQ35 DQ36 DQ37 DQ38 DQ39 DQ40 DQ41 DQ42 DQ43 DQ44 DQ45 DQ46 DQ47 DQ48 DQ49 DQ50 DQ51 DQ52 DQ53 DQ54 DQ55 DQ56 DQ57 DQ58 DQ59 DQ60 DQ61 DQ62 DQ63 NC1 NC2 NC3 NC4 NC/TEST 5 7 17 19 4 6 14 16 23 25 35 37 20 22 36 38 43 45 55 57 44 46 56 58 61 63 73 75 62 64 74 76 123 125 135 137 124 126 134 136 141 143 151 153 140 142 152 154 157 159 173 175 158 160 174 176 179 181 189 191 180 182 192 194 50 69 83 120 163 MEM_MA_DATA0 MEM_MA_DATA1 MEM_MA_DATA2 MEM_MA_DATA3 MEM_MA_DATA4 MEM_MA_DATA5 MEM_MA_DATA6 MEM_MA_DATA7 MEM_MA_DATA8 MEM_MA_DATA9 MEM_MA_DATA10 MEM_MA_DATA11 MEM_MA_DATA12 MEM_MA_DATA13 MEM_MA_DATA14 MEM_MA_DATA15 MEM_MA_DATA16 MEM_MA_DATA17 MEM_MA_DATA18 MEM_MA_DATA19 MEM_MA_DATA20 MEM_MA_DATA21 MEM_MA_DATA22 MEM_MA_DATA23 MEM_MA_DATA24 MEM_MA_DATA25 MEM_MA_DATA26 MEM_MA_DATA27 MEM_MA_DATA28 MEM_MA_DATA29 MEM_MA_DATA30 MEM_MA_DATA31 MEM_MA_DATA36 MEM_MA_DATA37 MEM_MA_DATA35 MEM_MA_DATA39 MEM_MA_DATA38 MEM_MA_DATA32 MEM_MA_DATA33 MEM_MA_DATA34 MEM_MA_DATA40 MEM_MA_DATA41 MEM_MA_DATA46 MEM_MA_DATA47 MEM_MA_DATA44 MEM_MA_DATA45 MEM_MA_DATA42 MEM_MA_DATA43 MEM_MA_DATA52 MEM_MA_DATA49 MEM_MA_DATA54 MEM_MA_DATA55 MEM_MA_DATA53 MEM_MA_DATA48 MEM_MA_DATA51 MEM_MA_DATA50 MEM_MA_DATA61 MEM_MA_DATA60 MEM_MA_DATA63 MEM_MA_DATA62 MEM_MA_DATA56 MEM_MA_DATA57 MEM_MA_DATA58 MEM_MA_DATA59 MEMHOT_SODIMM#_1 MEM_MA_RESET#1 MEM_MA_NC5 R106 T155 T115 +3V VSS56 VSS55 VSS54 VSS53 VSS52 VSS51 VSS50 VSS49 VSS48 VSS47 VSS46 VSS45 VSS44 VSS43 VSS42 VSS41 VSS40 VSS39 VSS38 VSS37 VSS36 VSS35 VSS34 196 193 190 187 184 183 178 177 172 171 168 165 162 161 156 155 150 149 145 144 139 138 133 +0.9VSMVREF_DIMM C848 2.2U/6.3V_6 C406 0.1U/10V_4 0_4 MEM_MA_DATA[0..63] 4 4,7 MEM_MB_ADD[0..15] MEM_MB_ADD0 MEM_MB_ADD1 MEM_MB_ADD2 MEM_MB_ADD3 MEM_MB_ADD4 MEM_MB_ADD5 MEM_MB_ADD6 MEM_MB_ADD7 MEM_MB_ADD8 MEM_MB_ADD9 MEM_MB_ADD10 MEM_MB_ADD11 MEM_MB_ADD12 MEM_MB_ADD13 MEM_MB_ADD14 MEM_MB_ADD15

+1.8VSUS 81 82 87 88 95 96 103 104 111 112 117 118 CN31 DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 DQ16 DQ17 DQ18 DQ19 DQ20 DQ21 DQ22 DQ23 DQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31 DQ32 DQ33 DQ34 DQ35 DQ36 DQ37 DQ38 DQ39 DQ40 DQ41 DQ42 DQ43 DQ44 DQ45 DQ46 DQ47 DQ48 DQ49 DQ50 DQ51 DQ52 DQ53 DQ54 DQ55 DQ56 DQ57 DQ58 DQ59 DQ60 DQ61 DQ62 DQ63 5 7 17 19 4 6 14 16 23 25 35 37 20 22 36 38 43 45 55 57 44 46 56 58 61 63 73 75 62 64 74 76 123 125 135 137 124 126 134 136 141 143 151 153 140 142 152 154 157 159 173 175 158 160 174 176 179 181 189 191 180 182 192 194 50 69 83 120 163 MEM_MB_DATA4 MEM_MB_DATA5 MEM_MB_DATA2 MEM_MB_DATA3 MEM_MB_DATA0 MEM_MB_DATA1 MEM_MB_DATA6 MEM_MB_DATA7 MEM_MB_DATA13 MEM_MB_DATA12 MEM_MB_DATA11 MEM_MB_DATA10 MEM_MB_DATA8 MEM_MB_DATA9 MEM_MB_DATA14 MEM_MB_DATA15 MEM_MB_DATA16 MEM_MB_DATA17 MEM_MB_DATA18 MEM_MB_DATA19 MEM_MB_DATA20 MEM_MB_DATA21 MEM_MB_DATA22 MEM_MB_DATA23 MEM_MB_DATA24 MEM_MB_DATA25 MEM_MB_DATA26 MEM_MB_DATA27 MEM_MB_DATA28 MEM_MB_DATA29 MEM_MB_DATA30 MEM_MB_DATA31 MEM_MB_DATA37 MEM_MB_DATA36 MEM_MB_DATA34 MEM_MB_DATA35 MEM_MB_DATA33 MEM_MB_DATA32 MEM_MB_DATA38 MEM_MB_DATA39 MEM_MB_DATA40 MEM_MB_DATA45 MEM_MB_DATA47 MEM_MB_DATA46 MEM_MB_DATA44 MEM_MB_DATA41 MEM_MB_DATA43 MEM_MB_DATA42 MEM_MB_DATA52 MEM_MB_DATA53 MEM_MB_DATA50 MEM_MB_DATA51 MEM_MB_DATA48 MEM_MB_DATA49 MEM_MB_DATA54 MEM_MB_DATA55 MEM_MB_DATA56 MEM_MB_DATA60 MEM_MB_DATA58 MEM_MB_DATA59 MEM_MB_DATA61 MEM_MB_DATA57 MEM_MB_DATA62 MEM_MB_DATA63 MEMHOT_SODIMM#_2 R105 MEM_MB_RESET#2 T156 MEM_MB_NC5 T114 0_4 MEMHOT_SODIMM# MEM_MB_DATA[0..63] 4

D

4,7 MEM_MA_BANK[0..2]

4,7 MEM_MB_BANK[0..2]

102 101 100 99 98 97 94 92 93 91 105 90 89 116 86 84

VDD0 VDD1 VDD2 VDD3 VDD4 VDD5 VDD6 VDD7 VDD8 VDD9 VDD10 VDD11

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 BA0 BA1 BA2 DM0 DM1 DM2 DM3 DM4 DM5 DM6 DM7 DQS0 DQS1 DQS2 DQS3 DQS4 DQS5 DQS6 DQS7 DQS0 DQS1 DQS2 DQS3 DQS4 DQS5 DQS6 DQS7 CK0 CK0 CK1 CK1 CKE0 CKE1 RAS CAS WE S0 S1 ODT0 ODT1 SA0 SA1 SDA SCL

VDD0 VDD1 VDD2 VDD3 VDD4 VDD5 VDD6 VDD7 VDD8 VDD9 VDD10 VDD11

07D

4 MEM_MA_DM[0..7]

MEM_MA_BANK0 107 MEM_MA_BANK1 106 MEM_MA_BANK2 85 MEM_MA_DM0 MEM_MA_DM1 MEM_MA_DM2 MEM_MA_DM3 MEM_MA_DM4 MEM_MA_DM5 MEM_MA_DM6 MEM_MA_DM7 10 26 52 67 130 147 170 185 13 31 51 70 131 148 169 188 11 29 49 68 129 146 167 186 30 32 164 166 79 80 108 113 109 110 115 114 119 DIM1_SA0 DIM1_SA1 198 200 195 197 199 1 2 3 8 9 12 15 18 21 24 27 28 33 34 39 40 41 42 47 48 53 54

4 MEM_MB_DM[0..7]

MEM_MB_BANK0 107 MEM_MB_BANK1 106 MEM_MB_BANK2 85 MEM_MB_DM0 MEM_MB_DM1 MEM_MB_DM2 MEM_MB_DM3 MEM_MB_DM4 MEM_MB_DM5 MEM_MB_DM6 MEM_MB_DM7 10 26 52 67 130 147 170 185 13 31 51 70 131 148 169 188 11 29 49 68 129 146 167 186 30 32 164 166 79 80 108 113 109 110 115 114 119 DIM2_SA0 DIM2_SA1 PDAT_SMB PCLK_SMB C702 0.1U/10V_4 C397 1000P/50V_4 198 200 195 197 199 1 2 o 3 8 9 12 15 18 21 24 27 28 33 34 39 40 41 42 47 48 53 54

4 4 4 4 4 4 4 4C

MEM_MA_DQS0_P MEM_MA_DQS1_P MEM_MA_DQS2_P MEM_MA_DQS3_P MEM_MA_DQS4_P MEM_MA_DQS5_P MEM_MA_DQS6_P MEM_MA_DQS7_P MEM_MA_DQS0_N MEM_MA_DQS1_N MEM_MA_DQS2_N MEM_MA_DQS3_N MEM_MA_DQS4_N MEM_MA_DQS5_N MEM_MA_DQS6_N MEM_MA_DQS7_N

4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4

MEM_MB_DQS0_P MEM_MB_DQS1_P MEM_MB_DQS2_P MEM_MB_DQS3_P MEM_MB_DQS4_P MEM_MB_DQS5_P MEM_MB_DQS6_P MEM_MB_DQS7_P MEM_MB_DQS0_N MEM_MB_DQS1_N MEM_MB_DQS2_N MEM_MB_DQS3_N MEM_MB_DQS4_N MEM_MB_DQS5_N MEM_MB_DQS6_N MEM_MB_DQS7_N MEM_MB_CLK1_P MEM_MB_CLK1_N MEM_MB_CLK7_P MEM_MB_CLK7_N

4 4 4 4 4 4 4 4 4 4 4 4

C

MEM_MA_CLK1_P MEM_MA_CLK1_N MEM_MA_CLK7_P MEM_MA_CLK7_N

4,7 MEM_MA_CKE0 4,7 MEM_MA_CKE1 4,7 4,7 4,7 4,7 4,7 MEM_MA_RAS# MEM_MA_CAS# MEM_MA_WE# MEM_MA0_CS#0 MEM_MA0_CS#1

4,7 MEM_MB_CKE0 4,7 MEM_MB_CKE1 4,7 MEM_MB_RAS# 4,7 MEM_MB_CAS# 4,7 MEM_MB_WE# 4,7 MEM_MB0_CS#0 4,7 MEM_MB0_CS#1 4,7 MEM_MB0_ODT0 4,7 MEM_MB0_ODT1 MEMHOT_SODIMM# 7

SO-DIMM (Normal)

4,7 MEM_MA0_ODT0 4,7 MEM_MA0_ODT1

B

SO-DIMM (REVERSE)

2,7,13,28,36 PDAT_SMB 2,7,13,28,36 PCLK_SMB +3V

PDAT_SMB PCLK_SMB C701 0.1U/10V_4

NC1 NC2 NC3 NC4 NC/TEST

B

VDDspd VREF VSS0 VSS1 VSS2 o VSS3 VSS4 VSS5 VSS6 VSS7 VSS8 VSS9 VSS10 VSS11 VSS12 VSS13 VSS14 VSS15 VSS16 VSS17 VSS18 VSS19 VSS20 GND GND 201 202

+0.9VSMVREF_DIMM

C849 C391 1000P/50V_4 C370 0.1U/10V_4 2.2U/6.3V_6

+1.8VSUS

+0.9VSMVREF_DIMM

R138 2K/F_4

VSS21 VSS22 VSS23 VSS24 VSS25 VSS26 VSS27 VSS28 VSS29 VSS30 VSS31 VSS32 VSS33

VSS21 VSS22 VSS23 VSS24 VSS25 VSS26 VSS27 VSS28 VSS29 VSS30 VSS31 VSS32 VSS33

4,41 +0.9VSMVREF

R139

*0_4

+0.9VSMVREF_DIMM

VSS56 VSS55 VSS54 VSS53 VSS52 VSS51 VSS50 VSS49 VSS48 VSS47 VSS46 VSS45 VSS44 VSS43 VSS42 VSS41 VSS40 VSS39 VSS38 VSS37 VSS36 VSS35 VSS34

196 193 190 187 184 183 178 177 172 171 168 165 162 161 156 155 150 149 145 144 139 138 133A

59 60 65 66 71 72 77 78 121 122 127 128 132

59 60 65 66 71 72 77 78 121 122 127 128 132

DDR SO-DIMM SOCKET 1.8V

A

Only for reserved

R130 2K/F_4

H=9.2

DDR SO-DIMM SOCKET 1.8V

H=5.2DIM2_SA0 DIM2_SA1 R40 R43 10K/F_4 10K/F_4 DIM1_SA0 DIM1_SA1 R423 R424 10K/F_4 10K/F_4 +3V

SMbus address A2Size Custom NB5/RD5

PROJECT : QT8 Quanta Computer Inc.Document Number

SMbus address A05 4 3 2

DDR2 SODIMMS: A/B CHANNELSheet 6 of 451

Rev 1A

Date: Tuesday, February 19, 2008

5

4

3

2

1

4,6 MEM_MA_ADD[0..15] 4,6 MEM_MA_BANK[0..2]

MEM_MA_ADD[0..15] MEM_MA_BANK[0..2]

4,6 MEM_MB_ADD[0..15] 4,6 MEM_MB_BANK[0..2]

MEM_MB_ADD[0..15] MEM_MB_BANK[0..2]

08+0.9VSMVTT C193 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 +1.8VSUSC

+0.9VSMVTT 4,6 MEM_MA_CKE0D

4,6 4,6 4,6 4,6

MEM_MA_WE# MEM_MA_CAS# MEM_MA0_ODT1 MEM_MA0_CS#1

4,6 MEM_MA_CKE1

MEM_MA_CKE0 MEM_MA_BANK2 MEM_MA_ADD12 MEM_MA_ADD9 MEM_MA_ADD8 MEM_MA_ADD5 MEM_MA_ADD3 MEM_MA_ADD1 MEM_MA_ADD10 MEM_MA_BANK0 MEM_MA_WE# MEM_MA_CAS# MEM_MA0_ODT1 MEM_MA0_CS#1 MEM_MA_ADD15 MEM_MA_CKE1

RP40 RP35 RP28 RP26 RP20 RP16 RP10 RP39

4 2 4 2 2 4 2 4 4 2 4 2 4 2 4 2 4 2 4 2 4 2 2 4 4 2 4 2

3 1 3 1 1 3 1 3 3 1 3 1 3 1 3 1

47_4P2R_4 C176 47_4P2R_4 C256 47_4P2R_4 C223 47_4P2R_4 C104 47_4P2R_4 C217 47_4P2R_4 C96 47_4P2R_4 C152 47_4P2R_4 C271 C162 C101 C208 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 +1.8VSUS +1.8VSUS 0.1U/10V_4 +1.8VSUS 0.1U/10V_4 0.1U/10V_4 +1.8VSUS 0.1U/10V_4 0.1U/10V_4 +1.8VSUS 0.1U/10V_4 0.1U/10V_4 +1.8VSUS

4,6 MEM_MB_CKE0

4,6 4,6 4,6 4,6 4,6

MEM_MB_WE# MEM_MB_CAS# MEM_MB0_ODT1 MEM_MB0_CS#1 MEM_MB_CKE1

MEM_MB_CKE0 MEM_MB_BANK2 MEM_MB_ADD12 MEM_MB_ADD9 MEM_MB_ADD8 MEM_MB_ADD5 MEM_MB_ADD3 MEM_MB_ADD1 MEM_MB_ADD10 MEM_MB_BANK0 MEM_MB_WE# MEM_MB_CAS# MEM_MB0_ODT1 MEM_MB0_CS#1 MEM_MB_CKE1 MEM_MB_ADD15 MEM_MB_ADD7 MEM_MB_ADD14 MEM_MB_ADD6 MEM_MB_ADD11 MEM_MB_ADD2 MEM_MB_ADD4 MEM_MB_BANK1 MEM_MB_ADD0

RP36 RP32 RP27 RP25 RP18 RP15 RP9 RP38 RP34 RP30 RP22 RP19 RP13 RP11

4 2 2 4 4 2 4 2 4 2 4 2 4 2 2 4 4 2 4 2 4 2 4 2 4 2 2 4

3 1 1 3 3 1 3 1 3 1 3 1 3 1 1 3

47_4P2R_4 47_4P2R_4 C245 47_4P2R_4 C154 47_4P2R_4 C100 47_4P2R_4 C137 47_4P2R_4 C94 47_4P2R_4 C190 47_4P2R_4 C93 C160 C254 C173 C255 C126 C253 C178 C105 +1.8VSUS +1.8VSUS +1.8VSUS +1.8VSUSD

MEM_MA_ADD7 RP33 MEM_MA_ADD14 MEM_MA_ADD6 RP29 MEM_MA_ADD11 MEM_MA_ADD2 MEM_MA_ADD4 RP24

3 47_4P2R_4 1 3 47_4P2R_4 1 3 47_4P2R_4 1 1 47_4P2R_4 3 3 47_4P2R_4 1 3 47_4P2R_4 1

+1.8VSUS

3 47_4P2R_4 1 3 47_4P2R_4 1 3 47_4P2R_4 1 3 47_4P2R_4 1 3 47_4P2R_4 1 1 47_4P2R_4 3

+1.8VSUS

+1.8VSUS

C102 C107 C270 C146 C269

MEM_MA_BANK1 RP21 MEM_MA_ADD0 4,6 MEM_MA0_CS#0 4,6 MEM_MA_RAS#C

+1.8VSUS

+1.8VSUS 4,6 MEM_MB0_CS#0 4,6 MEM_MB_RAS# 4,6 MEM_MB0_ODT0

MEM_MA0_CS#0 RP14 MEM_MA_RAS# MEM_MA_ADD13 RP12 MEM_MA0_ODT0

MEM_MB0_CS#0 MEM_MB_RAS# MEM_MB0_ODT0 MEM_MB_ADD13

4,6 MEM_MA0_ODT0

PLACE CLOSE TO PROCESSOR WITHIN 1.5 INCH+1.8VSUS +1.8VSUS

PLACE CLOSE TO PROCESSOR WITHIN 1.5 INCH

C239 0.1U/10V_4

C121 0.1U/10V_4

C241 0.1U/10V_4

C242 0.1U/10V_4

C117 0.1U/10V_4

C235 0.1U/10V_4

C122 0.1U/10V_4

C119 0.1U/10V_4

C237 0.1U/10V_4

C115 0.1U/10V_4

C116 0.1U/10V_4

C745 0.1U/10V_4

PLACE CLOSE TO SOCKET( PER EMI/EMC)

PLACE CLOSE TO SOCKET( PER EMI/EMC)

B

B

+3VS5

SI-2

modified --SB internal pull HI to 3vs5

+3V

R417 *10K/F_4 R421 *10K/F_4

CPU_MEMHOT# 3,13 3

Close DDR2 socketU25 7 6 5 1 2 A0 A1 A2 SDA SCL +VS O.S 2,6,13,28,36 PDAT_SMB 2,6,13,28,36 PCLK_SMB PDAT_SMB PCLK_SMB GND 8 3 4 +3V R416 C706 0.1U/10V_4 3 *33_4 2

+3V

Q32 *2N7002E-G 1

MEMHOT_SODIMM#

2 Q33 *2N7002E-G 1

*DS75U+T&R R422

Address:92hMEMHOT_SODIMM# 6A

A

+3V

10K/F_4 MEMHOT_SODIMM#

PROJECT : QT8 Quanta Computer Inc.Size Custom NB5/RD55 4 3 2

Document Number

DDR2 SODIMMS TERMINATIONSSheet1

Rev 1A 45

Date: Tuesday, February 19, 2008

7

of

5

4

3

2

1

U32A HT_CPU_NB_CAD_H0 HT_CPU_NB_CAD_L0 HT_CPU_NB_CAD_H1 HT_CPU_NB_CAD_L1 HT_CPU_NB_CAD_H2 HT_CPU_NB_CAD_L2 HT_CPU_NB_CAD_H3 HT_CPU_NB_CAD_L3 HT_CPU_NB_CAD_H4 HT_CPU_NB_CAD_L4 HT_CPU_NB_CAD_H5 HT_CPU_NB_CAD_L5 HT_CPU_NB_CAD_H6 HT_CPU_NB_CAD_L6 HT_CPU_NB_CAD_H7 HT_CPU_NB_CAD_L7 HT_CPU_NB_CAD_H8 HT_CPU_NB_CAD_L8 HT_CPU_NB_CAD_H9 HT_CPU_NB_CAD_L9 HT_CPU_NB_CAD_H10 HT_CPU_NB_CAD_L10 HT_CPU_NB_CAD_H11 HT_CPU_NB_CAD_L11 HT_CPU_NB_CAD_H12 HT_CPU_NB_CAD_L12 HT_CPU_NB_CAD_H13 HT_CPU_NB_CAD_L13 HT_CPU_NB_CAD_H14 HT_CPU_NB_CAD_L14 HT_CPU_NB_CAD_H15 HT_CPU_NB_CAD_L15 HT_CPU_NB_CLK_H0 HT_CPU_NB_CLK_L0 HT_CPU_NB_CLK_H1 HT_CPU_NB_CLK_L1 Y25 Y24 V22 V23 V25 V24 U24 U25 T25 T24 P22 P23 P25 P24 N24 N25 AC24 AC25 AB25 AB24 AA24 AA25 Y22 Y23 W21 W20 V21 V20 U20 U21 U19 U18 T22 T23 AB23 AA22 M22 M23 R21 R20 C23 A24 HT_RXCAD0P HT_RXCAD0N HT_RXCAD1P HT_RXCAD1N HT_RXCAD2P HT_RXCAD2N HT_RXCAD3P HT_RXCAD3N HT_RXCAD4P HT_RXCAD4N HT_RXCAD5P HT_RXCAD5N HT_RXCAD6P HT_RXCAD6N HT_RXCAD7P HT_RXCAD7N

PART 1 OF 6

HYPER TRANSPORT CPU I/F

D

HT_TXCAD0P HT_TXCAD0N HT_TXCAD1P HT_TXCAD1N HT_TXCAD2P HT_TXCAD2N HT_TXCAD3P HT_TXCAD3N HT_TXCAD4P HT_TXCAD4N HT_TXCAD5P HT_TXCAD5N HT_TXCAD6P HT_TXCAD6N HT_TXCAD7P HT_TXCAD7N HT_TXCAD8P HT_TXCAD8N HT_TXCAD9P HT_TXCAD9N HT_TXCAD10P HT_TXCAD10N HT_TXCAD11P HT_TXCAD11N HT_TXCAD12P HT_TXCAD12N HT_TXCAD13P HT_TXCAD13N HT_TXCAD14P HT_TXCAD14N HT_TXCAD15P HT_TXCAD15N HT_TXCLK0P HT_TXCLK0N HT_TXCLK1P HT_TXCLK1N HT_TXCTL0P HT_TXCTL0N HT_TXCTL1P HT_TXCTL1N HT_TXCALP HT_TXCALN

D24 D25 E24 E25 F24 F25 F23 F22 H23 H22 J25 J24 K24 K25 K23 K22 F21 G21 G20 H21 J20 J21 J18 K17 L19 J19 M19 L18 M21 P21 P18 M18 H24 H25 L21 L20 M24 M25 P19 R18 B24 B25

HT_NB_CPU_CAD_H0 HT_NB_CPU_CAD_L0 HT_NB_CPU_CAD_H1 HT_NB_CPU_CAD_L1 HT_NB_CPU_CAD_H2 HT_NB_CPU_CAD_L2 HT_NB_CPU_CAD_H3 HT_NB_CPU_CAD_L3 HT_NB_CPU_CAD_H4 HT_NB_CPU_CAD_L4 HT_NB_CPU_CAD_H5 HT_NB_CPU_CAD_L5 HT_NB_CPU_CAD_H6 HT_NB_CPU_CAD_L6 HT_NB_CPU_CAD_H7 HT_NB_CPU_CAD_L7 HT_NB_CPU_CAD_H8 HT_NB_CPU_CAD_L8 HT_NB_CPU_CAD_H9 HT_NB_CPU_CAD_L9 HT_NB_CPU_CAD_H10 HT_NB_CPU_CAD_L10 HT_NB_CPU_CAD_H11 HT_NB_CPU_CAD_L11 HT_NB_CPU_CAD_H12 HT_NB_CPU_CAD_L12 HT_NB_CPU_CAD_H13 HT_NB_CPU_CAD_L13 HT_NB_CPU_CAD_H14 HT_NB_CPU_CAD_L14 HT_NB_CPU_CAD_H15 HT_NB_CPU_CAD_L15 HT_NB_CPU_CLK_H0 HT_NB_CPU_CLK_L0 HT_NB_CPU_CLK_H1 HT_NB_CPU_CLK_L1 HT_NB_CPU_CTL_H0 HT_NB_CPU_CTL_L0 HT_NB_CPU_CTL_H1 HT_NB_CPU_CTL_L1 HT_TXCALP R534 HT_TXCALN

HT_CPU_NB_CAD_H[15..0] HT_CPU_NB_CAD_L[15..0] HT_CPU_NB_CLK_H[1..0] HT_CPU_NB_CLK_L[1..0] HT_CPU_NB_CTL_H[1..0] HT_CPU_NB_CTL_L[1..0] HT_NB_CPU_CAD_H[15..0] HT_NB_CPU_CAD_L[15..0] HT_NB_CPU_CLK_H[1..0] HT_NB_CPU_CLK_L[1..0] HT_NB_CPU_CTL_H[1..0] HT_NB_CPU_CTL_L[1..0]

HT_CPU_NB_CAD_H[15..0] HT_CPU_NB_CAD_L[15..0] HT_CPU_NB_CLK_H[1..0] HT_CPU_NB_CLK_L[1..0] HT_CPU_NB_CTL_H[1..0] HT_CPU_NB_CTL_L[1..0] HT_NB_CPU_CAD_H[15..0] HT_NB_CPU_CAD_L[15..0] HT_NB_CPU_CLK_H[1..0] HT_NB_CPU_CLK_L[1..0] HT_NB_CPU_CTL_H[1..0] HT_NB_CPU_CTL_L[1..0]

3 3 3 3 3 3

08D

3 3 3 3 3 3

HT_RXCAD8P HT_RXCAD8N HT_RXCAD9P HT_RXCAD9N HT_RXCAD10P HT_RXCAD10N HT_RXCAD11P HT_RXCAD11N HT_RXCAD12P HT_RXCAD12N HT_RXCAD13P HT_RXCAD13N HT_RXCAD14P HT_RXCAD14N HT_RXCAD15P HT_RXCAD15N HT_RXCLK0P HT_RXCLK0N HT_RXCLK1P HT_RXCLK1N HT_RXCTL0P HT_RXCTL0N HT_RXCTL1P HT_RXCTL1N HT_RXCALP HT_RXCALN RS780(RX780)

signals HT_TXCALP SI-2 modified -- follow AMD check list to change part number 300 ohm to 301 ohm301/F_4

RS780

RX780 RES CHIP 1.21K 1/16W +-1%(0402) P/N : CS21212FB18

HT_TXCALN HT_RXCALP HT_RXCALN

R641 301 ohm 1%

R641 1.21k ohm 1%

C

SI-2 modified -- follow AMD check list to change part number 300 ohm to 301 ohm

HT_CPU_NB_CTL_H0 HT_CPU_NB_CTL_L0 HT_CPU_NB_CTL_H1 HT_CPU_NB_CTL_L1 R533

R655 301 ohm 1%

R655 1.21k ohm 1%

RES CHIP 301 1/16W +-1%(0402) P/N : CS13012FB14C

R655

301/F_4

HT_RXCALP HT_RXCALN

R641

U27 SPM_BA0 SPM_BA1 SPM_A12 SPM_A11 SPM_A10 SPM_A9 SPM_A8 SPM_A7 SPM_A6 SPM_A5 SPM_A4 SPM_A3 SPM_A2 SPM_A1 SPM_A0 SPM_CLKN SPM_CLKP SPM_CKE L2 L3 R2 P7 M2 P3 P8 P2 N7 N3 N8 N2 M7 M3 M8 K8 J8 K2 BA0 BA1 A12 A11 A10/AP A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 CK CK CKE DQ15 DQ14 DQ13 DQ12 DQ11 DQ10 DQ9 DQ8 DQ7 DQ6 DQ5 DQ4 DQ3 DQ2 DQ1 DQ0 VDDQ1 VDDQ2 VDDQ3 VDDQ4 VDDQ5 VDDQ6 VDDQ7 VDDQ8 VDDQ9 VDDQ10 VDD1 VDD2 VDD3 VDD4 VDD5 VDDL VSSDL ODT LDQS LDQS C757 *1U/10V_4 VSSQ1 VSSQ2 VSSQ3 VSSQ4 VSSQ5 VSSQ6 VSSQ7 VSSQ8 VSSQ9 VSSQ10 VSS1 VSS2 VSS3 VSS4 VSS5 A7 B2 B8 D2 D8 E7 F2 F8 H2 H8 A3 E3 J3 N1 P9 R502 R501 +1.8V_MEM_VDDQ B9 B1 D9 D1 D3 D7 C2 C8 F9 F1 H9 H1 H3 H7 G2 G8 A9 C1 C3 C7 C9 E9 G1 G3 G7 G9 A1 E1 J9 M9 R1 J1 J7 MEM_VDDQ_VDDL SPM_DQ15 SPM_DQ14 SPM_DQ9 SPM_DQ12 SPM_DQ8 SPM_DQ10 SPM_DQ13 SPM_DQ11 SPM_DQ5 SPM_DQ3 SPM_DQ4 SPM_DQ1 SPM_DQ0 SPM_DQ7 SPM_DQ2 SPM_DQ6

This block is for UMA RS780 only , RX780 can remove all component+1.8V U32D SPM_A0 SPM_A1 SPM_A2 SPM_A3 SPM_A4 SPM_A5 SPM_A6 SPM_A7 SPM_A8 SPM_A9 SPM_A10 SPM_A11 SPM_A12 SPM_A13 SPM_BA0 SPM_BA1 SPM_BA2 L76 *BLM18PG181SN1D(180,1.5A)_6 SPM_RAS# SPM_CAS# SPM_WE# SPM_CS# SPM_CKE SPM_ODT SPM_CLKP SPM_CLKN +1.8V_MEM_VDDQ R487 AA18 AA20 AA19 Y19 V17 AA17 AA15 Y15 AC20 AD19 AE22 AC18 AB20 AD22 AC22 AD21 Y17 W18 AD20 AE21 W17 AE19 AE23 AE24 AD23 AE18 SPM_VREF1 SPM_DQ0 SPM_DQ1 SPM_DQ2 SPM_DQ3 SPM_DQ4 SPM_DQ5 SPM_DQ6 SPM_DQ7 SPM_DQ8 SPM_DQ9 SPM_DQ10 SPM_DQ11 SPM_DQ12 SPM_DQ13 SPM_DQ14 SPM_DQ15 SPM_DQS0P SPM_DQS0N SPM_DQS1P SPM_DQS1N SPM_DM0 SPM_DM1 +1.8_IOPLLVDD18_NB +1.1V_IOPLLVDD C762 *2.2U/6.3V_6 C763 *2.2U/6.3V_6 C70 *1U/10V_4 C738 *10U/6.3V_8 C76 *10U/6.3V_8 *0_6

40mils wdith or morePAR 4 OF 6MEM_DQ0/DVO_VSYNC(NC) MEM_DQ1/DVO_HSYNC(NC) MEM_DQ2/DVO_DE(NC) MEM_DQ3/DVO_D0(NC) MEM_DQ4(NC) MEM_DQ5/DVO_D1(NC) MEM_DQ6/DVO_D2(NC) MEM_DQ7/DVO_D4(NC) MEM_DQ8/DVO_D3(NC) MEM_DQ9/DVO_D5(NC) MEM_DQ10/DVO_D6(NC) MEM_DQ11/DVO_D7(NC) MEM_DQ12(NC) MEM_DQ13/DVO_D9(NC) MEM_DQ14/DVO_D10(NC) MEM_DQ15/DVO_D11(NC) MEM_DQS0P/DVO_IDCKP(NC) MEM_DQS0N/DVO_IDCKN(NC) MEM_DQS1P(NC) MEM_DQS1N(NC) MEM_DM0(NC) MEM_DM1/DVO_D8(NC) IOPLLVDD18(NC) IOPLLVDD(NC) IOPLLVSS(NC)

B

R56

*100_4

+1.8V_MEM_VDDQ

Within 200mils

SBD_MEM/DVO_I/F

T24

SPM_CS# SPM_WE# SPM_RAS# SPM_CAS# SPM_DM0 SPM_DM1 SPM_ODT +1.8V_MEM_VDDQ SPM_DQS0P SPM_DQS0N

AB12 AE16 V11 AE15 AA12 AB16 AB14 AD14 AD13 AD15 AC16 AE13 AC14 Y14 AD16 AE17 AD17 W12 Y12 AD18 AB13 AB18 V14 V15 W14

L8 K3 K7 L7 F3 B3 K9 F7 E8

MEM_A0(NC) MEM_A1(NC) MEM_A2(NC) MEM_A3(NC) MEM_A4(NC) MEM_A5(NC) MEM_A6(NC) MEM_A7(NC) MEM_A8(NC) MEM_A9(NC) MEM_A10(NC) MEM_A11(NC) MEM_A12(NC) MEM_A13(NC) MEM_BA0(NC) MEM_BA1(NC) MEM_BA2(NC)

B

C87 *0.1U/10V_4

C77 *0.1U/10V_4

C74 *1U/10V_4

CS WE RAS CAS LDM UDM

MEM_RASb(NC) MEM_CASb(NC) MEM_WEb(NC) MEM_CSb(NC) MEM_CKE(NC) MEM_ODT(NC) MEM_CKP(NC) MEM_CKN(NC)

IOPLLVDD18 - memory PLL not applicable to RX780

Del L77, L78 for TP on PVIOPLLVDD- memory PLL not applicable to RX780

*40.2/F_4 SPM_COMPP AE12 *40.2/F_4 SPM_COMPN AD12

MEM_COMPP(NC) MEM_COMPN(NC) RS780(RX780)

MEM_VREF(NC)

C95 *0.1U/10V_4A

R63 *1K_4

SPM_DQS1P SPM_DQS1N SPM_VREF

B7 A8 J2 A2 E2 L1 R3 R7 R8

UDQS UDQS VREF NC#A2 NC#E2 NC#L1 NC#R3 NC#R7 NC#R8

R498

*1K_4

R497

*1K_4

C775

*0.1U/10V_4

C774

*0.1U/10V_4

+1.8V_MEM_VDDQ

A

C89 *0.1U/10V_4

R61 *1K_4

SPM_BA2

PROJECT : QT8 Quanta Computer Inc.Size Custom NB5/RD5 Document Number

*HYB18T512161B2F-25

RS740/RS780-HT LINK I/F 1/5Sheet 8 of 451

Rev 1A

Date: Tuesday, February 19, 20085 4 3 2

5

4

3

2

1

U32B PEG_RX15 PEG_RX#15 PEG_RX14 PEG_RX#14 PEG_RX13 PEG_RX#13 PEG_RX12 PEG_RX#12 PEG_RX11 PEG_RX#11 PEG_RX10 PEG_RX#10 PEG_RX9 PEG_RX#9 PEG_RX8 PEG_RX#8 PEG_RX7 PEG_RX#7 PEG_RX6 PEG_RX#6 PEG_RX5 PEG_RX#5 PEG_RX4 PEG_RX#4 PEG_RX3 PEG_RX#3 PEG_RX2 PEG_RX#2 PEG_RX1 PEG_RX#1 PEG_RX0 PEG_RX#0 33 PCIE_RXP0 33 PCIE_RXN0 36 PCIE_RXP1 36 PCIE_RXN1 31 PCIE_RXP6_LAN 31 PCIE_RXN6_LAN 36 PCIE_RXP3 36 PCIE_RXN3 T223 T225 26 26 12 12 12 12 12 12 12 12 PCIE_RXP5 PCIE_RXN5 D4 C4 A3 B3 C2 C1 E5 F5 G5 G6 H5 H6 J6 J5 J7 J8 L5 L6 M8 L8 P7 M7 P5 M5 R8 P8 R6 R5 P4 P3 T4 T3 GFX_RX0P GFX_RX0N GFX_RX1P GFX_RX1N GFX_RX2P GFX_RX2N GFX_RX3P GFX_RX3N GFX_RX4P GFX_RX4N GFX_RX5P GFX_RX5N GFX_RX6P GFX_RX6N GFX_RX7P GFX_RX7N GFX_RX8P GFX_RX8N GFX_RX9P GFX_RX9N GFX_RX10P GFX_RX10N GFX_RX11P GFX_RX11N GFX_RX12P GFX_RX12N GFX_RX13P GFX_RX13N GFX_RX14P GFX_RX14N GFX_RX15P GFX_RX15N GPP_RX0P GPP_RX0N GPP_RX1P GPP_RX1N GPP_RX2P GPP_RX2N GPP_RX3P GPP_RX3N GPP_RX4P GPP_RX4N GPP_RX5P GPP_RX5N SB_RX0P SB_RX0N SB_RX1P SB_RX1N SB_RX2P SB_RX2N SB_RX3P SB_RX3N

PART 2 OF 6

D

GFX_TX0P GFX_TX0N GFX_TX1P GFX_TX1N GFX_TX2P GFX_TX2N GFX_TX3P GFX_TX3N GFX_TX4P GFX_TX4N GFX_TX5P GFX_TX5N GFX_TX6P GFX_TX6N GFX_TX7P GFX_TX7N GFX_TX8P GFX_TX8N GFX_TX9P GFX_TX9N GFX_TX10P GFX_TX10N GFX_TX11P GFX_TX11N GFX_TX12P GFX_TX12N GFX_TX13P GFX_TX13N GFX_TX14P GFX_TX14N GFX_TX15P GFX_TX15N GPP_TX0P GPP_TX0N GPP_TX1P GPP_TX1N GPP_TX2P GPP_TX2N GPP_TX3P GPP_TX3N GPP_TX4P GPP_TX4N GPP_TX5P GPP_TX5N SB_TX0P SB_TX0N SB_TX1P SB_TX1N SB_TX2P SB_TX2N SB_TX3P SB_TX3N

A5 B5 A4 B4 C3 B2 D1 D2 E2 E1 F4 F3 F1 F2 H4 H3 H1 H2 J2 J1 K4 K3 K1 K2 M4 M3 M1 M2 N2 N1 P1 P2 AC1 AC2 AB4 AB3 AA2 AA1 Y1 Y2 Y4 Y3 V1 V2 AD7 AE7 AE6 AD6 AB6 AC6 AD5 AE5 AC8 AB8

C_PEG_TX15 C_PEG_TX#15 C_PEG_TX14 C_PEG_TX#14 C_PEG_TX13 C_PEG_TX#13 C_PEG_TX12 C_PEG_TX#12 C_PEG_TX11 C_PEG_TX#11 C_PEG_TX10 C_PEG_TX#10 C_PEG_TX9 C_PEG_TX#9 C_PEG_TX8 C_PEG_TX#8 C_PEG_TX7 C_PEG_TX#7 C_PEG_TX6 C_PEG_TX#6 C_PEG_TX5 C_PEG_TX#5 C_PEG_TX4 C_PEG_TX#4 C_PEG_TX3 C_PEG_TX#3 C_PEG_TX2 C_PEG_TX#2 C_PEG_TX1 C_PEG_TX#1 C_PEG_TX0 C_PEG_TX#0 PCIE_TXP0_C PCIE_TXN0_C PCIE_TXP1_C PCIE_TXN1_C PCIE_TXP6_C PCIE_TXN6_C PCIE_TXP3_C PCIE_TXN3_C PCIE_TXP4_C PCIE_TXN4_C PCIE_TXP5_C PCIE_TXN5_C

C360 C359 C362 C361 C343 C354 C351 C350 C814 C815 C810 C809 C811 C813 C806 C805 C804 C800 C798 C801 C791 C795 C792 C796 C788 C785 C787 C784 C778 C783 C771 C777 C158 C159 C131 C130 C149 C148 C772 C773 C139 C140

0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 T224 T226 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 R491 R489

PEG_TX15 PEG_TX#15 PEG_TX14 PEG_TX#14 PEG_TX13 PEG_TX#13 PEG_TX12 PEG_TX#12 PEG_TX11 PEG_TX#11 PEG_TX10 PEG_TX#10 PEG_TX9 PEG_TX#9 PEG_TX8 PEG_TX#8 PEG_TX7 PEG_TX#7 PEG_TX6 PEG_TX#6 PEG_TX5 PEG_TX#5 PEG_TX4 PEG_TX#4 PEG_TX3 PEG_TX#3 PEG_TX2 PEG_TX#2 PEG_TX1 PEG_TX#1 PEG_TX0 PEG_TX#0 PCIE_TXP0 33 PCIE_TXN0 33 PCIE_TXP1 36 PCIE_TXN1 36 PCIE_TXP6_LAN 31 PCIE_TXN6_LAN 31 PCIE_TXP3 36 PCIE_TXN3 36 PCIE_TXP5 26 PCIE_TXN5 26 PCIE_NB_SB_TX0P PCIE_NB_SB_TX0N PCIE_NB_SB_TX1P PCIE_NB_SB_TX1N PCIE_NB_SB_TX2P PCIE_NB_SB_TX2N PCIE_NB_SB_TX3P PCIE_NB_SB_TX3N +1.1V

17 PEG_RX#[15:0] 17 PEG_RX[15:0]

PEG_RX#[15:0] PEG_RX[15:0]

PEG_TX#[15:0] PEG_TX[15:0]

PEG_TX#[15:0] 17 PEG_TX[15:0] 17

9D

Close to North Bridge

C_PEG_TX15 C_PEG_TX#15 C_PEG_TX14 C_PEG_TX#14 C_PEG_TX13 C_PEG_TX#13 C_PEG_TX12 C_PEG_TX#12

C_PEG_TX15 23 C_PEG_TX#15 23 C_PEG_TX14 23 C_PEG_TX#14 23 C_PEG_TX13 23 C_PEG_TX#13 23 C_PEG_TX12 23 C_PEG_TX#12 23

PCIE I/F GFX

To HDMI CONN

C

PCIE_RXP0 AE3 PCIE_RXN0 AD4 PCIE_RXP1 AE2 PCIE_RXN1 AD3 PCIE_RXP6_LAN AD1 PCIE_RXN6_LAN AD2 PCIE_RXP3 V5 PCIE_RXN3 W6 PCIE_RXP4 U5 PCIE_RXN4 U6 PCIE_RXP5 U8 PCIE_RXN5 U7 AA8 Y8 AA7 Y7 AA5 AA6 W5 Y5

TO EPRESS CARD TO WLAN TO PCIE-LAN TO TV TUNNERC

PCIE I/F GPP

TO PCIE CARD READER12 12 12 12 12 12 12 12

PCIE_SB_NB_RX0P PCIE_SB_NB_RX0N PCIE_SB_NB_RX1P PCIE_SB_NB_RX1N PCIE_SB_NB_RX2P PCIE_SB_NB_RX2N PCIE_SB_NB_RX3P PCIE_SB_NB_RX3N

PCIE I/F SB

A_TX0P_C C766 A_TX0N_C C767 A_TX1P_C C765 A_TX1N_C C764 A_TX2P_C C150 A_TX2N_C C151 A_TX3P_C C754 A_TX3N_C C755 NB_PCIECALRP NB_PCIECALRN

PCE_CALRP(PCE_BCALRP) PCE_CALRN(PCE_BCALRN)

1.27K/F_4 2K/F_4

RS780(RX780)RX780/RS740/RS780 difference table (PCIE LINK)RS740 NB_PCIECALRP GPP4B

RS780 Display Port Support (muxed on GFX)GFX_TX0,TX1,TX2 and TX3

RX780/RS780 1.27K (GND) GPP4 GFX_TX4,TX5,TX6 and TX7 DP1 GPP5 AUX1 and HPD1B

562R (GND) NC NC

DP0 AUX0 and HPD0

GPP5

A

A

PROJECT : QT8 Quanta Computer Inc.Size Custom NB5/RD55 4 3 2

Document Number

RS740/RS780-PCIE I/F 2/5Sheet 9 of 451

Rev 1A

Date: Tuesday, February 19, 2008

5

4

3

2

1

RX780: Powered from the 1.8-V and driven by SB600 LDT_RST#, SB700 LDT_RST# or A_RST#. RS780: Powered from the 3.3-V and driven by SB600 LDT_RST#, SB700 LDT_RST# or A_RST#. RX7803,12 CPU_LDT_RST#

rail or rail or R109 for UAM use 140 ohm

U32C +3V_AVDD_NB +1.8V_AVDDDI_NB +1.8V_AVDDQ_NB S-CD1 *0_4 0_4 NB_RST#_IN 18,24 CRT_R CRT_G CRT_B R446 R109 R445 R110 R444 R111 R549 R540 R133 R134 R119 *0_4 *150/F_4 *0_4 *150/F_4 *0_4 *150/F_4 *0_4 *0_4 *0_4 *0_4 *715/F_6 CRT_R_1 CRT_G_1 CRT_B_1 HSYNC_INT VSYNC_INT DDCDATA_INT DDCCLK_INT DAC_RSET_NB +1.1V_PLLVDD +1.8V_PLLVDD18 +1.8V_VDDA18HTPLL +1.8V_VDDA18PCIEPLL NB_RST#_IN NB_PWRGD_IN NB_LDT_STOP# NB_ALLOW_LDTSTOP NBHT_REFCLKP NBHT_REFCLKN R117 R125 RS780 4.7K_4 0_4 NB_REFCLK_P NB_REFCLK_N

F12 E12 F14 G15 H15 H14 E17 F17 F15 G18 G17 E18 F18 E19 F19 A11 B11 E8 F8 G14 A12 D14 B12 H17 D7 E7 D8 A10 C10 C12 C25 C24 E11 F11 T2 T1 U1 U2 V4 V3 A9 B9 B8 A8 B7 A7 B10 G11

AVDD1(NC) AVDD2(NC) AVDDDI(NC) AVSSDI(NC) AVDDQ(NC) AVSSQ(NC) C_Pr(DFT_GPIO5) Y(DFT_GPIO2) COMP_Pb(DFT_GPIO4) RED(DFT_GPIO0) REDb(NC) GREEN(DFT_GPIO1) GREENb(NC) BLUE(DFT_GPIO3) BLUEb(NC)

PART 3 OF 6

CRT/TVOUT

TXOUT_L0P(NC) TXOUT_L0N(NC) TXOUT_L1P(NC) TXOUT_L1N(NC) TXOUT_L2P(NC) TXOUT_L2N(DBG_GPIO0) TXOUT_L3P(NC) TXOUT_L3N(DBG_GPIO2)

A22 B22 A21 B21 B20 A20 A19 B19 B18 A18 A17 B17 D20 D21 D18 D19 B16 A16 D16 D17 A13 B13 A15 B15 A14 B14 C14 D15 C16 C18 C20 E20 C22

LA_DATAP0 LA_DATAN0 LA_DATAP1 LA_DATAN1 LA_DATAP2 LA_DATAN2 LA_DATAP3 LA_DATAN3 LB_DATAP0 LB_DATAN0 LB_DATAP1 LB_DATAN1 LB_DATAP2 LB_DATAN2 LB_DATAP3 LB_DATAN3 LA_CLK LA_CLK# LB_CLK LB_CLK# +1.8V_VDDLTP18_NB +1.8V_VDDLT_18_NB

LA_DATAP0 LA_DATAN0 LA_DATAP1 LA_DATAN1 LA_DATAP2 LA_DATAN2 T159 T157 LB_DATAP0 LB_DATAN0 LB_DATAP1 LB_DATAN1 LB_DATAP2 LB_DATAN2 T163 T160 LA_CLK LA_CLK# LB_CLK LB_CLK# 23 23 23 23

23 23 23 23 23 23

10D

R157 R160

RS78012 NB_PLTRST#D

18,24 18,24

North Bridge RESET

TXOUT_U0P(NC) TXOUT_U0N(NC) TXOUT_U1P(PCIE_RESET_GPIO3) TXOUT_U1N(PCIE_RESET_GPIO2) TXOUT_U2P(NC) TXOUT_U2N(NC) TXOUT_U3P(PCIE_RESET_GPIO5) TXOUT_U3N(NC) TXCLK_LP(DBG_GPIO1) TXCLK_LN(DBG_GPIO3) TXCLK_UP(PCIE_RESET_GPIO4) TXCLK_UN(PCIE_RESET_GPIO1) VDDLTP18(NC) VSSLTP18(NC)

23 23 23 23 23 23

18,19,24 HSYNC_COM 18,19,24 VSYNC_COM 18,24 DDCDATA 18,24 DDCCLK

DAC_HSYNC(PWM_GPIO4) DAC_VSYNC(PWM_GPIO6) DAC_SDA(PCE_TCALRN) DAC_SCL(PCE_RCALRN) DAC_RSET(PWM_GPIO1)

PLL PWR LVTM

PLLVDD(NC) PLLVDD18(NC) PLLVSS(NC) VDDA18HTPLL VDDA18PCIEPLL1 VDDA18PCIEPLL2 SYSRESETb POWERGOOD LDTSTOPb ALLOW_LDTSTOP HT_REFCLKP HT_REFCLKN

VDDLT18_1(NC) VDDLT18_2(NC) VDDLT33_1(NC) VDDLT33_2(NC) VSSLT1(VSS) VSSLT2(VSS) VSSLT3(VSS) VSSLT4(VSS) VSSLT5(VSS) VSSLT6(VSS) VSSLT7(VSS)

+3V_VDLT33_NB

16 NB_PWRGD_IN

2 NBHT_REFCLKP 2 NBHT_REFCLKN 2 EXT_NB_OSC +1.1V

PM

I

RS780 only

CLOCKs

REFCLK_P/OSCIN(OSCIN) REFCLK_N(PWM_GPIO3) GFX_REFCLKP GFX_REFCLKN GPP_REFCLKP GPP_REFCLKN

I

RS780 R120

4.7K_4

NBGFX_CLKP NBGFX_CLKN NBGPP_CLKP NBGPP_CLKN SBLINK_CLKP SBLINK_CLKN

I/O I/O

LVDS_DIGON(PCE_TCALRP) LVDS_BLON(PCE_RCALRP) LVDS_ENA_BL(PWM_GPIO2)

E9 F7 G12

R132 R126 R118

*0_4 *0_4 *0_4

DISP_ON LVDS_BLON DPST_PWM

DISP_ON 19,23 LVDS_BLON 18,23 DPST_PWM 19,23

Del NBGPP CLKC

2 NBGFX_CLKP 2 NBGFX_CLKN T168 T169 2 SBLINK_CLKP 2 SBLINK_CLKN 18,23 EDIDDATA 18,23 EDIDCLK 23 HDMI_DDC_DATA 23 HDMI_DDC_CLK R547 R546 R537 R544 *0_4 *0_4 *0_4 *0_4 T161 T158 39 DYN_PWR_EN

R121 R127

*1.27K/F_4 *1.27K/F_4 R545 *0_4 T162 R131 0_4 T136 T135 SUS_STAT# 13

For RX780 only

C

GPPSB_REFCLKP(SB_REFCLKP) GPPSB_REFCLKN(SB_REFCLKN) I2C_DATA I2C_CLK DDC_DATA/AUX0N(NC) DDC_CLK/AUX0P(NC) AUX1P(NC) AUX1N(NC) STRP_DATA RSVD AUX_CAL(NC)

+3V

R536 R539 R538

4.7K_4 4.7K_4 4.7K_4

HDTV_DET NB_I2C_DATA NB_I2C_CLK

RS780 only

NB_I2C_DATA NB_I2C_CLK HDTV_DET RS740_DFT_GPIO0 RS740_DFT_GPIO1 R27 0_4 STRP_DATA

MIS.

TMDS_HPD(NC) HPD(NC) TVCLKIN(PWM_GPIO5) THERMALDIODE_P THERMALDIODE_N TESTMODE

D9 D10 D12 AE8 AD8

TMDS_HPD0 TMDS_HPD1 SUS_STAT#_NB R_NB_THRMDA R_NB_THRMDC

UMA onlyTMDS_HPD 18,23

D13 TEST_ENR541 1.82K/F_4

selects Loading of straps from EPROM 1 : use default vaule , default 0 : I2C Master can load strap values from EEPROM if connected, or use default values if not connected RX780 --RS780_AUX_CAL RS780 -- SUS_ATAT

T164

RS780_AUX_CAL

C8

RS780(RX780)

RX780RS780_AUX_CAL R543 3K_4 +3V

RX780 -->NC / RS780 --- ADDL35 BLM18PG181SN1D(180,1.5A)_6 +3V_AVDD_NB +1.1V

BLM18PG181SN1D(180,1.5A)_6 +1.1V_PLLVDD L82 C842 2.2U/6.3V_6

AVDD-DAC Analog not applicable to RX780+1.8VB

C340 2.2U/6.3V_6

PLLVDD - Graphics PLL not applicable to RX780

+1.8V BLM18PG181SN1D(180,1.5A)_6 +1.8V_VDDLTP18_NB L83 C841 2.2U/6.3V_6

VDDLTP18 - LVDS or DVI/HDMI PLL not applicable to RX780B

Enables Debug Bus acess through memory T/O pads and GPIO. 0 : Enable RS780 , Default 1 : Disable RS780 (RS780 use VSYNC#)

RS780VSYNC_COM R124 3K_4 +3V L33 BLM18PG181SN1D(180,1.5A)_6 C405 10U/6.3V_8 +1.8V_PLLVDD18

+1.8V R107 0_6 +1.8V_AVDDDI_NB C321 2.2U/6.3V_6 BLM18PG181SN1D(180,1.5A)_6 +1.8V_AVDDQ_NB L34 C349 2.2U/6.3V_6

AVDDI-DAC Digital not applicable to RX780

BLM21PG221SN1D(220,100M,2A)_8 +1.8V_VDDLT_18_NB L85 C846 4.7U/6.3V_6 C838 0.1U/10V_4

C333 2.2U/6.3V_6

VDDLT18 - LVDS or DVI/HDMI digital not applicable to RX780

Indicates if memory Side port is available or not 0: available RS780 , Default 1: Not available RS780 ( RS780 use HSYNC#)

RS780HSYNC_COM R129 R136 3K_4 *3K_4 +3V

PLLVDD18 - Graphics PLL not applicable to RX780

AVDDQ-DAC Bandgap Reference not applicable to RX780

+1.8V

RX780 +1.8V+1.8V +VDDG_NB

R566

*0_6 +VDDG_NB

VDDA18PCIEPLL -PCIE PLL

R565 Q37 BSS138_NL/SOT23

0_6

For extrnal EEPROM Debug onlySTRP_DATA R548 R558

RS780/RX78010K/F_4 *10K/F_4 +VDDG_NB

L32

20mils width +1.8V_VDDA18PCIEPLL

RS7801

BLM18PG181SN1D(180,1.5A)_6 C358 2.2U/6.3V_6 3,12 CPU_LDT_STOP#

R556 4.7K_4

RS780

RS780

+3V

2

3

NB_LDT_STOP# +3V

L84 +3V_VDLT33_NB C844 *2.2U/6.3V_6A

*BLM21PG221SN1D(220,100M,2A)_8 R555 *0_4

VDDA18HTPLL -HT LINK PLLA

RX780+VDDG_NB +1.8V

Enables Debug Bus acess through memory T/O pads and GPIO. 1 : Enable RX780 , Default 0 : Disable RX780

RX780S-CD1 R810 *3K_4

L31

20mils width +1.8V_VDDA18HTPLL

BLM18PG181SN1D(180,1.5A)_6 C356 2.2U/6.3V_6 3 CPU_LDT_REQ#

RS780Q38 BSS138_NL/SOT23 R568 0_4

RS780R557 4.7K_4 NB_ALLOW_LDTSTOP

VDDLT33 - LVDS or DVI/HDMI ANALOG RS740 only

Reserved only

2

1

3

PROJECT : QT8 Quanta Computer Inc.Size Custom NB5/RD5 Document Number

12 ALLOW_LDTSTOP

R564

*0_4

RX7805 4 3 2

RS740/RS780-SYSTEM I/F 3/5Sheet 10 of 451

Rev 1A

Date: Tuesday, February 19, 2008

5

4

3

2

1

U32F

RX780/RS780 POWER DIFFERENCE TABLEPIN NAME VDDHT VDDHTRX VDDHTTX VDDA18PCIE VDDG18 VDD18_MEM

11RS780+1.1V +3.3V +1.8V +1.8V +1.1V +1.8V +1.8V +1.8V +1.8V +1.8V NCD

VSSAPCIE1 VSSAPCIE2 VSSAPCIE3 VSSAPCIE4 VSSAPCIE5 VSSAPCIE6 VSSAPCIE7 VSSAPCIE8 VSSAPCIE9 VSSAPCIE10 VSSAPCIE11 VSSAPCIE12 VSSAPCIE13 VSSAPCIE14 VSSAPCIE15 VSSAPCIE16 VSSAPCIE17 VSSAPCIE18 VSSAPCIE19 VSSAPCIE20 VSSAPCIE21 VSSAPCIE22 VSSAPCIE23 VSSAPCIE24 VSSAPCIE25 VSSAPCIE26 VSSAPCIE27 VSSAPCIE28 VSSAPCIE29 VSSAPCIE30 VSSAPCIE31 VSSAPCIE32 VSSAPCIE33 VSSAPCIE34 VSSAPCIE35 VSSAPCIE36 VSSAPCIE37 VSSAPCIE38 VSSAPCIE39 VSSAPCIE40

VSS1 VSS2 VSS3 VSS4 VSS5 VSS6 VSS7 VSS8 VSS9 VSS10

AE14 D11 G8 E14 E15 J15 J12 K14 M11 L15

A2 B1 D3 D5 E4 G1 G2 G4 H7 J4 R7 L1 L2 L4 L7 M6 N4 P6 R1 R2 R4 V7 U4 V8 V6 W1 W2 W4 W7 W8 Y6 AA4 AB5 AB1 AB7 AC3 AC4 AE1 AE4 AB2

RX780+1.1V +1.1V +1.2V +1.8V +1.8V NC +1.1V +1.1V NC NC NC

RS780+1.1V +1.1V +1.2V +1.8V +1.8V +1.8V +1.1V +1.1V +1.8V/1.5V +3.3V +1.8V

PIN NAME IOPLLVDD AVDD AVDDDI AVDDQ PLLVDD PLLVDD18 VDDA18PCIEPLL VDDA18HTPLL VDDLTP18 VDDLT18 VDDLT33

RX780NC NC NC NC NC NC +1.8V +1.8V NC NC NC

D

PART 6/6

VSSAHT1 VSSAHT2 VSSAHT3 VSSAHT4 VSSAHT5 VSSAHT6 VSSAHT7 VSSAHT8 VSSAHT9 VSSAHT10 VSSAHT11 VSSAHT12 VSSAHT13 VSSAHT14 VSSAHT15 VSSAHT16 VSSAHT17 VSSAHT18 VSSAHT19 VSSAHT20 VSSAHT21 VSSAHT22 VSSAHT23 VSSAHT24 VSSAHT25 VSSAHT26 VSSAHT27

VSS11 VSS12 VSS13 VSS14 VSS15 VSS16 VSS17 VSS18 VSS19 VSS20 VSS21 VSS22 VSS23 VSS24 VSS25 VSS26 VSS27 VSS28 VSS29 VSS30 VSS31 VSS32 VSS33 VSS34

A25 D23 E22 G22 G24 G25 H19 J22 L17 L22 L24 L25 M20 N22 P20 R19 R22 R24 R25 H20 U22 V19 W22 W24 W25 Y21 AD25

L12 M14 N13 P12 P15 R11 R14 T12 U14 U11 U15 V12 W11 W15 AC12 AA14 Y18 AB11 AB15 AB17 AB19 AE20 AB21 K11

+1.1VC

VDDHT - HT LINK digital I/O for RX780/RS780

+1.1V 2A for RS780M0.6AL72 BLM21PG221SN1D(220,100M,2A)_8 C770 4.7U/6.3V_6 C274 0.1U/10V_4 +1.1V_VDDHT C313 0.1U/10V_4 C280 0.1U/10V_4 J17 K16 L16 M16 P16 R16 T16 H18 G19 F20 E21 D22 B23 A23 AE25 AD24 AC23 AB22 AA21 Y20 W19 V18 U17 T17 R17 P17 M17 J10 P10 K10 M10 L10 W9 H9 T10 R10 Y9 AA9 AB9 AD9 AE9 U10 F9 G9 AE11 AD11

VDDHTRX - HT LINK RX I/O for RX780/RS780

0.45A

L81 BLM21PG221SN1D(220,100M,2A)_8 C847 4.7U/6.3V_6 C323 0.1U/10V_4

L12 +1.2V BLM21PG221SN1D(220,100M,2A)_8

0.5A

+1.2V 2A for RS780M+SB700C124 4.7U/6.3V_6 C195 0.1U/10V_4 C194 0.1U/10V_4

L13 +1.35V *BLM21PG221SN1D(220,100M,2A)_8

B

+1.8V 1A for RS780M+SB700+1.8V L22

POWER

+1.35V for A1-1 chip bug , A1-2 can remove

VDDHTTX - HT LINK TX I/O for RX780/RS780

600mAC188 4.7U/6.3V_6 C175 4.7U/6.3V_6 C258 0.1U/10V_4 C209 0.1U/10V_4

BLM21PG221SN1D(220,100M,2A)_8

VDDA18PCIE PCIE TX stage I/O for RX780/RS780

VDD18 - RS780 I/O +1.8V transform

+1.8V

VDD18_MEM For UMA RS780 only Not applicable to RX780 memory I/O transformA

5

GROUNDU32E VDDHT_1 VDDHT_2 VDDHT_3 VDDHT_4 VDDHT_5 VDDHT_6 VDDHT_7 VDDHTRX_1 VDDHTRX_2 VDDHTRX_3 VDDHTRX_4 VDDHTRX_5 VDDHTRX_6 VDDHTRX_7 VDDHTTX_1 VDDHTTX_2 VDDHTTX_3 VDDHTTX_4 VDDHTTX_5 VDDHTTX_6 VDDHTTX_7 VDDHTTX_8 VDDHTTX_9 VDDHTTX_10 VDDHTTX_11 VDDHTTX_12 VDDHTTX_13 VDDA18PCIE_1 VDDA18PCIE_2 VDDA18PCIE_3 VDDA18PCIE_4 VDDA18PCIE_5 VDDA18PCIE_6 VDDA18PCIE_7 VDDA18PCIE_8 VDDA18PCIE_9 VDDA18PCIE_10 VDDA18PCIE_11 VDDA18PCIE_12 VDDA18PCIE_13 VDDA18PCIE_14 VDDA18PCIE_15 VDDG18_1(VDD18_1) VDDG18_2(VDD18_2) VDD18_MEM1(NC) VDD18_MEM2(NC) RS780(RX780)

VDDPCIE VDDC VDD_MEM VDDG33 IOPLLVDD18

VDDPCIE - PCIE-E Main power

C

PART 5/6

+1.1V_VDDHTRX C843 0.1U/10V_4 C839 0.1U/10V_4

+1.2V_VDDHTTX C199 0.1U/10V_4

VDDPCIE_1 VDDPCIE_2 VDDPCIE_3 VDDPCIE_4 VDDPCIE_5 VDDPCIE_6 VDDPCIE_7 VDDPCIE_8 VDDPCIE_9 VDDPCIE_10 VDDPCIE_11 VDDPCIE_12 VDDPCIE_13 VDDPCIE_14 VDDPCIE_15 VDDPCIE_16 VDDPCIE_17 VDDC_1 VDDC_2 VDDC_3 VDDC_4 VDDC_5 VDDC_6 VDDC_7 VDDC_8 VDDC_9 VDDC_10 VDDC_11 VDDC_12 VDDC_13 VDDC_14 VDDC_15 VDDC_16 VDDC_17 VDDC_18 VDDC_19 VDDC_20 VDDC_21 VDDC_22 VDD_MEM1(NC) VDD_MEM2(NC) VDD_MEM3(NC) VDD_MEM4(NC) VDD_MEM5(NC) VDD_MEM6(NC) VDDG33_1(NC) VDDG33_2(NC)

A6 B6 C6 D6 E6 F6 G7 H8 J9 K9 M9 L9 P9 R9 T9 V9 U9 K12 J14 U16 J11 K15 M12 L14 L11 M13 M15 N12 N14 P11 P13 P14 R12 R15 T11 T15 U12 T14 J16 AE10 AA11 Y11 AD10 AB10 AC10 H11 H12

+1.1V_VDD_PCIE C275 0.1U/10V_4 C337 0.1U/10V_4 C318 1U/10V_4

0.7AC328 1U/10V_4

R542 C845 4.7U/6.3V_6

0_8

+1.1V

7AC251 0.1U/10V_4 C292 0.1U/10V_4 C297 0.1U/10V_4 C303 0.1U/10V_4

VDDC - Core Logic power+1.1V_DYN C59 10U/6.3V_8

C249 0.1U/10V_4

B

+1.8V_VDDA18PCIE C302 0.1U/10V_4 C234 0.1U/10V_4

C281 0.1U/10V_4

C278 0.1U/10V_4

C250 0.1U/10V_4

C60 10U/6.3V_8

+1.8V_VDD_MEM C192 0.1U/10V_4 C179 0.1U/10V_4 C172 0.1U/10V_4

1.8V(0.15A)C216 0.1U/10V_4 RS780 0_6

VDD_MEM For UMA RS780 only Not applicable to RX780 memory I/O transformL23 +1.8V BLM21PG221SN1D(220,100M,2A)_8

R122

0_6

0.005AC317 1U/10V_4 +1.8V_VDDG18_NB +1.8V_VDD18_MEM

C153 4.7U/6.3V_6

R499

0_6

0.005AC769 1U/10V_4

+3V_VDDG33 C336 0.1U/10V_4

R123 C329 0.1U/10V_4

3.3V(0.03A)+3V

VDD33 - 3.3V I/O Not applicable to RX780

A

PROJECT : QT8 Quanta Computer Inc.Size Custom NB5/RD54 3 2

Document Number

RS740/RS780-POWER5/5Sheet1

Rev 1A 11 of 45

Date: Tuesday, February 19, 2008

5

4

3

2

1

10 17 26 31 33 36 9 9 9 9 9 9 9 9 9 9 9 9 9 9 9 9

NB_PLTRST# PCIE_RST# CARD_PLTRST# LAN_PLTRST# EPRESS_PLTRST# MINI_PLTRST# PCIE_SB_NB_RX0P PCIE_SB_NB_RX0N PCIE_SB_NB_RX1P PCIE_SB_NB_RX1N PCIE_SB_NB_RX2P PCIE_SB_NB_RX2N PCIE_SB_NB_RX3P PCIE_SB_NB_RX3N PCIE_NB_SB_TX0P PCIE_NB_SB_TX0N PCIE_NB_SB_TX1P PCIE_NB_SB_TX1N PCIE_NB_SB_TX2P PCIE_NB_SB_TX2N PCIE_NB_SB_TX3P PCIE_NB_SB_TX3N R581 R587

R250 R252 R312 R251 R241 R660 C869 C868 C865 C864 C871 C870 C867 C866

33_4 33_4 33_4 33_4 33_4 33_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4 0.1U/10V_4

12Del R639, R640, R641, R642 on PVU37A A_RST#_SB A_RX0P_C A_RX0N_C A_RX1P_C A_RX1N_C A_RX2P_C A_RX2N_C A_RX3P_C A_RX3N_C N2 V23 V22 V24 V25 U25 U24 T23 T22 U22 U21 U19 V19 R20 R21 R18 R17 T25 T24 P24 P25

SB700A_RST# PCIE_TX0P PCIE_TX0N PCIE_TX1P PCIE_TX1N PCIE_TX2P PCIE_TX2N PCIE_TX3P PCIE_TX3N PCIE_RX0P PCIE_RX0N PCIE_RX1P PCIE_RX1N PCIE_RX2P PCIE_RX2N PCIE_RX3P PCIE_RX3N PCIE_CALRP PCIE_CALRN PCIE_PVDD PCIE_PVSS

PCI CLKS

Part 1 of 5

D

To RS780

PLACE THESE PCIE AC COUPLING CAPS CLOSE TO U600

PCICLK0 PCICLK1 PCICLK2 PCICLK3 PCICLK4 PCICLK5/GPIO41

P4 P3 P1 P2 T4 T3

PCI_CLK2_R PCI_CLK3_R PCI_CLK4_R PCI_CLK5_R

T108 T214 PCI_CLK_TPM 16 PCI_CLK3 16 PCI_CLK4 16 PCI_CLK5 16D

PCIRST#

N1 U2 P7 V4 T1 V3 U1 V1 V2 T2 W1 T9 R6 R7 R5 U8 U5 Y7 W8 V9 Y8 AA8 Y4 Y3 Y2 AA2 AB4 AA1 AB3 AB2 AC1 AC2 AD1 W2 U7 AA7 Y1 AA6 W5 AA5 Y5 U6 W6 W4 V7 AC3 AD4 AB7 AE6 AB6 AD2 AE4 AD5 AC6 AE5 AD6 V5 AD3 AC4 AE2 AE3 G22 E22 H24 H23 J25 J24 H25 H22 AB8 AD7 V15 C3 C2 B2

PCIRST#_L

R643

33_4

PCIRST#

PCIRST# 35

PCIE_NB_SB_TX0P PCIE_NB_SB_TX0N PCIE_NB_SB_TX1P PCIE_NB_SB_TX1N PCIE_NB_SB_TX2P PCIE_NB_SB_TX2N PCIE_NB_SB_TX3P PCIE_NB_SB_TX3N 562/F_4 2.05K/F_4 PCIE_CALRP_SB PCIE_CALRN_SB +1.2V_PCIE_PVDD

PCI EXPRESS INTERFACE

+1.2V_PCIE_VDDR+1.2V L44

BLM18PG181SN1D(180,1.5A)_6 C485 10U/6.3V_8

PCIE_PVDD-- PCIE PLL POWER

40mAC503 1U/10V_4

C

2 2

SBSRC_CLKP SBSRC_CLKN

SBSRC_CLKP SBSRC_CLKN

N25 N24 K23 K22 M24 M25 P17 M18

PCIE_RCLKP/NB_LNK_CLKP PCIE_RCLKN/NB_LNK_CLKN NB_DISP_CLKP NB_DISP_CLKN NB_HT_CLKP NB_HT_CLKN

100MHZ

CPU_HT_CLKP CPU_HT_CLKN SLT_GFX_CLKP SLT_GFX_CLKN GPP_CLK0P GPP_CLK0N GPP_CLK1P GPP_CLK1N GPP_CLK2P GPP_CLK2N GPP_CLK3P GPP_CLK3N 25M_48M_66M_OSC 25M_X1

Y8 3 2

C906 1U/10V_4 SERR# SERR# 35 C907 1U/10V_4

J19 J18 RTC_X2 L20 L19 M19 M20 N22 P22 L18 R257 0_4 J21

20MIL

+VCCRTC_2

RTC_X1

M23 M22

CLOCK GENERATOR

R632 *20M_6B

4

1 32.768KHZ

CLKRUN#_R T94 INTE# INTF# INTG# INTH# LPC_CLK0 LPC_CLK1 LAD0 LAD1 LAD2 LAD3 LFRAME# LDRQ0#_SB LDRQ1#_SB SB_GPIO65 SERIRQ

BT1 2 BAT_CONN

T74

J20

25M_X2

INTE#/GPIO33 INTF#/GPIO34 INTG#/GPIO35 INTH#/GPIO36 LPCCLK0 LPCCLK1 LAD0 LAD1 LAD2 LAD3 LFRAME# LDRQ0# LDRQ1#/GNT5#/GPIO68 BMREQ#/REQ5#/GPIO65 SERIRQ RTCCLK INTRUDER_ALERT# VBAT

T213 T110 T217 INTH# R243 R589 22_4 10_4

R589 change to 10 ohm on PV28 LPC_CLK0 16 LPC_CLK1 16 PCLK_LPC_DEBUG PCLK_LPC_KB3920 35 35,36 35,36 35,36 35,36 35,36 C940 5.6P/50V_6 C939 22P/50V_4 36

If CPU have pull Hi ,this pin should be not need PV-1 Modified -- change to pull hi to 3VS5 for power leakage issueA

RTC XTAL

RTC_X1

A3

X1

+1.8V

R232

*10K/F_4 RTC_X2 B3 X2

LPC

LAD0 LAD1 LAD2 LAD3 LFRAME# T61 T90 T107 SERIRQ RTC_CLK 16

SI-2 modified -- for EMI suggestion

+3VS5 10 ALLOW_LDTSTOP 3 CPU_PROCHOT# 3 CPU_PWRGD 3,10 CPU_LDT_STOP# 3,10 CPU_LDT_RST#

R588

10K/F_4 ALLOW_LDTSTOP CPU_PROCHOT# CPU_PWRGD CPU_LDT_STOP# CPU_LDT_RST# F23 F24 F22 G25 G24 ALLOW_LDTSTP PROCHOT# LDT_PG LDT_STP# LDT_RST# SB700

35

SI-1 Modified - for EMIR782 *1M/F_4 +AVBAT +AVBAT

RTC

CPU

RTC_CLK INTRUDER_ALERT# +AVBAT

SI-2 Modified--reserveA

20MIL

G3 *SHORT_ PAD1

IC CTRL(528P) SB700 A11(218S7EALA11FG) P/N : AJALA110T00

C902 0.1U/10V_4

INTRUDER_ALERT# Left not connected (Southbridge has 50-kohm internal pull-up to VBAT).

2

1

PROJECT : QT8 Quanta Computer Inc.Size Custom NB5/RD5 Document Number

1

C900 18P/50V_4

C899 18P/50V_4

PE_GPIO1

SI-2 Modified-- Add GPIO pin for control D3E wake up ( need low 1ms for Jmicron request)R631 R629 0_4 0_4 LCD_BK 23 CLKRUN# 35

20MIL

+BAT

R626

20M_6

AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 AD8 AD9 AD10 AD11 AD12 AD13 AD14 AD15 AD16 AD17 AD18 AD19 AD20 AD21 AD22 AD23 AD24 AD25 AD26 AD27 AD28 AD29 AD30 AD31 CBE0# CBE1# CBE2# CBE3# FRAME# DEVSEL# IRDY# TRDY# PAR STOP# PERR# SERR# REQ0# REQ1# REQ2# REQ3#/GPIO70 REQ4#/GPIO71 GNT0# GNT1# GNT2# GNT3#/GPIO72 GNT4#/GPIO73 CLKRUN# LOCK#

+3V PE_GPIO1 R294 R299 SB_GPIO65 R274 8.2K_4 *8.2K_4 *100K/F_4

R809

8.2K_4

+3V

C

AD23 AD24 AD25 AD26 AD27 AD28

PCI INTERFACE

AD23 AD24 AD25 AD26 AD27 AD28

16 16 16 16 16 16

change D21, D20 type for PV

+AVBAT

All the PCI bus has build-in Pull-UP/Down resistors

SI-2 mofified for satify -remove R560 , add R796 ,R797499/F_4 +3VRTC_1 R797 10_4 +3VRTC

D21 RB500V-40 +3VPCU

20MILR796

20MIL

20MIL

D20 RB500V-40

R298

SI-2 Modified-- for power leakage issueR187 0_4 RF_OFF# 36 D3E GPIO# 26

Del R783 for TP on PV

0_4

B

SB700-PCIE/PCI/CPU/LPC 1/4Sheet1

Rev 1A of 45

Date: Tuesday, February 19, 20085 4 3 2

12

5

4

3

2

1

+3VSUS R297 R240 R287

NC only ,Can't be install*2.2K_4 *2.2K_4 *2.2K_4 SB_TEST0 U37D SB_TEST1 SB_TEST2 33 NEWCARD_DETECT T211 T99 35 SUSB# 35 SUSC# 35 DNBSWON# 16 SB_PWRGD_IN 10 SUS_STAT# NEWCARD_DETECT RI# SLP_S2 SUSB# SUSC# DNBSWON# SB_PWRGD_IN SUS_STAT# SB_TEST2 SB_TEST1 SB_TEST0 GATEA20 RCIN# SCI# KBSMI# GEVENT5# SYS_RST# PCIE_WAKE# SWI# SB_THERMTRIP# WD_PWRGD E1 E2 H7 F5 G1 H2 H1 K3 H5 H4 H3 Y15 W15 K4 K24 F1 J2 H6 F2 J6 W14 D3

13SB700Part 4 of 5C8 G8 CLK_48M_USB USB_RCOMP_SB R267 CLK_48M_USB 2 11.8K/F_6 CLK_48M_USB USBCLK/14M_25M_48M_OSC

USB MISC

+3VSUSD

ACPI / WAKE UP EVENTS

R271 R191 R233

*0_4 *0_4 *0_4

R289

*10K/F_4 SWI#

SI-2 modified add D3E function+3V SCL0/SDATA0 R245 R253

is 3V tolerance AMD datasheet define it2.2K_4 2.2K_4 PCLK_SMB PDAT_SMB

Clock gen/Robson/TV tuner /DDR2/DDR2 thermal/Accelerometer

35 35 35 35

GATEA20 RCIN# SCI# KBSMI# T109 R211 R786 R284 *0_4 0_4

31,33,36 PCIE_WAKE# 35 SWI# 3 CPU_THERMTRIP# 16 WD_PWRGD

PCI_PME#/GEVENT4# RI#/EXTEVNT0# SLP_S2/GPM9# SLP_S3# SLP_S5# PWR_BTN# PWR_GOOD SUS_STAT# TEST2 TEST1 TEST0 GA20IN/GEVENT0# KBRST#/GEVENT1# LPC_PME#/GEVENT3# LPC_SMI#/EXTEVNT1# S3_STATE/GEVENT5# SYS_RESET#/GPM7# WAKE#/GEVENT8# BLINK/GPM6# SMBALERT#/THRMTRIP#/GEVENT2# NB_PWRGD RSMRST#

USB_RCOMP

USB_FSD13P USB_FSD13N

E6 E7 F7 E8 H11 J10 E11 F11 A11 B11 C10 D10 G11 H12 E12 E14 C12 D12 B12 A12 G12 G14 H14 H15 A13 B13 B14 A14 A18 B18 F21 D21 F19 E20 E21 E19 D19 E18 G20 G21 D25 D24 C25 C24 B25 C23 B24 B23 A23 C22 A22 B22 B21 A21 D20 C20 A20 B20 B19 A19 D18 C18

USB_FSD13P USB_FSD13N USB_FDS12P USB_FSD12N USBP11+ 36 USBP11- 36 USBP10+ 36 USBP10- 36 USBP9+ USBP9USBP8+ USBP8USBP7+ USBP7USBP6+ USBP6USBP5+ USBP5USBP4+ USBP4USBP3+ USBP3USBP2+ USBP2USBP1+ USBP1USBP0+ USBP030 30 30 30 30 30 30 30 30 30 33 33 30 30 30 30 37 37

T101 T199 T91 T93

C554 *2.2P/50V_4

D

USB 1.1

USB_FSD12P USB_FSD12N USB_HSD11P USB_HSD11N USB_HSD10P USB_HSD10N USB_HSD9P USB_HSD9N USB_HSD8P USB_HSD8N

TV Min-Card WLAN Min-Card USB Connector USB Connector NEW CARD FINGERPRINT BLUETOOTH Docking USB card reader or Touch screenC

for EMI & del R268 change 2.2P

+3VS5

SCL1/SDATA1 is 3V/S5 tolerance AMD datasheet define itR648 R649 *2.2K_4 *2.2K_4 SB_SMBCLK1 SB_SMBDATA1

SI-2 modified -- Change lan disable control from SB to EC SB reserveT63 T194 31,35 LAN_DISABLE# T222 27,28 ACZ_SPKR 2,6,7,28,36 PCLK_SMB 2,6,7,28,36 PDAT_SMB T69 T75 35 PM_BATLOW# 26 T72 D3E_SCI# R302 *0_4 R217 *0_4 SATA_IS1 LAN_DISABLE#_SB SB_NWD_CLK_REQ# ACZ_SPKR PCLK_SMB PDAT_SMB SB_SMBCLK1 SB_SMBDATA1 PM_BATLOW# SES_INT

35

RSMRST#

*0_4 RSMRST#

USB 2.0

remove pull hi ( chip internal have pull hi )+3VS5C

R222 R227 +3V

*2.2K_4 *2.2K_4

SB_SCLK2 SB_SDATA2

GPIO

SCL2/SDATA2 is 3V/S5 tolerance AMD datasheet define it

AE18 AD18 AA19 W17 V17 W20 W21 AA18 W18 K1 K2 AA20 Y18 C1 Y19 G5

SATA_IS0#/GPIO10 CLK_REQ3#/SATA_IS1#/GPIO6 SMARTVOLT/SATA_IS2#/GPIO4 CLK_REQ0#/SATA_IS3#/GPIO0 CLK_REQ1#/SATA_IS4#/FANOUT3/GPIO39 CLK_REQ2#/SATA_IS5#/FANIN3/GPIO40 SPKR/GPIO2 SCL0/GPOC0# SDA0/GPOC1# SCL1/GPOC2# SDA1/GPOC3# DDC1_SCL/GPIO9 DDC1_SDA/GPIO8 LLB#/GPIO66 SHUTDOWN#/GPIO5 DDR3_RST#/GEVENT7#

USB_HSD7P USB_HSD7N USB_HSD6P USB_HSD6N USB_HSD5P USB_HSD5N USB_HSD4P USB_HSD4N USB_HSD3P USB_HSD3N USB_HSD2P USB_HSD2N USB_HSD1P USB_HSD1N

D3E_SCI# from Gevent5# change to Gevent7# on PVR276 G4 2 1 *SHORT_ PAD1 +3VS5 R763 2.2K_4 DNBSWON# ACZ_BCLK ACZ_SDOUT ACZ_SDIN0_R ACZ_SDIN1_R T98 T209 ACZ_SDOUT_AUDIO C908B

Carama USB E-SATA and USB Connector USB Connector

4.7K_4

SUS_STAT# SYS_RST#

SI-2 modified Del D353,7 CPU_MEMHOT# 5 PM_THERM# +3VS5 CPU_MEMHOT#_IN R275 *0_4 SMBALERT#_1 R279 *10K/F_4 SB_JTAG_TDO SB_JTAG_TCK SB_JTAG_TDI SB_JTAG_RST# B9 B8 A8 A9 E5 F8 E4 M1 M2 J7 J8 L8 M3 L6 M4 L5 USB_OC6#/IR_TX1/GEVENT6# USB_OC5#/IR_TX0/GPM5# USB_OC4#/IR_RX0/GPM4# USB_OC3#/IR_RX1/GPM3# USB_OC2#/GPM2# USB_OC1#/GPM1# USB_OC0#/GPM0# AZ_BITCLK AZ_SDOUT AZ_SDIN0/GPIO42 AZ_SDIN1/GPIO43 AZ_SDIN2/GPIO44 AZ_SDIN3/GPIO46 AZ_SYNC AZ_RST# AZ_DOCK_RST#/GPM8#

USB_HSD0P USB_HSD0N

USB OC

To AzaliaACZ_SDOUT R644 33_4 27 16 *10P/50V_4

HD AUDIO