Nios II Processor Reference Handbook

Transcript of Nios II Processor Reference Handbook

Nios II Classic Processor Reference Guide

Subscribe

Send Feedback

NII5V12016.06.17

101 Innovation DriveSan Jose, CA 95134www.altera.com

Contents

Introduction........................................................................................................ 1-1Nios II Processor System Basics................................................................................................................. 1-1Getting Started with the Nios II Processor............................................................................................... 1-2Customizing Nios II Processor Designs....................................................................................................1-3Configurable Soft Processor Core Concepts............................................................................................ 1-4

Configurable Soft Processor Core..................................................................................................1-4Flexible Peripheral Set and Address Map..................................................................................... 1-4Automated System Generation...................................................................................................... 1-5

OpenCore Plus Evaluation..........................................................................................................................1-5Document Revision History....................................................................................................................... 1-6

Processor Architecture........................................................................................ 2-1Processor Implementation.......................................................................................................................... 2-2Register File...................................................................................................................................................2-3Arithmetic Logic Unit................................................................................................................................. 2-4

Unimplemented Instructions......................................................................................................... 2-4Custom Instructions........................................................................................................................ 2-5Floating-Point Instructions.............................................................................................................2-5

Reset and Debug Signals........................................................................................................................... 2-10Exception and Interrupt Controllers....................................................................................................... 2-11

Exception Controller..................................................................................................................... 2-11EIC Interface...................................................................................................................................2-11Internal Interrupt Controller........................................................................................................2-12

Memory and I/O Organization................................................................................................................2-12Instruction and Data Buses...........................................................................................................2-14Cache Memory............................................................................................................................... 2-16Tightly-Coupled Memory.............................................................................................................2-17Address Map................................................................................................................................... 2-18Memory Management Unit.......................................................................................................... 2-18Memory Protection Unit...............................................................................................................2-19

JTAG Debug Module................................................................................................................................. 2-20JTAG Target Connection...............................................................................................................2-20Download and Execute Software................................................................................................. 2-21Software Breakpoints..................................................................................................................... 2-21Hardware Breakpoints...................................................................................................................2-21Hardware Triggers..........................................................................................................................2-21Trace Capture..................................................................................................................................2-22

Document Revision History.....................................................................................................................2-23

Programming Model........................................................................................... 3-1Operating Modes..........................................................................................................................................3-1

TOC-2

Altera Corporation

Supervisor Mode.............................................................................................................................. 3-1User Mode......................................................................................................................................... 3-2

Memory Management Unit........................................................................................................................ 3-2Recommended Usage...................................................................................................................... 3-2Memory Management..................................................................................................................... 3-3Address Space and Memory Partitions......................................................................................... 3-4TLB Organization............................................................................................................................ 3-5TLB Lookups.....................................................................................................................................3-7

Memory Protection Unit.............................................................................................................................3-7Memory Regions.............................................................................................................................. 3-8Overlapping Regions....................................................................................................................... 3-9Enabling the MPU............................................................................................................................3-9

Registers.........................................................................................................................................................3-9General-Purpose Registers........................................................................................................... 3-10Control Registers............................................................................................................................3-11Shadow Register Sets..................................................................................................................... 3-30

Working with the MPU.............................................................................................................................3-32MPU Region Read and Write Operations.................................................................................. 3-32MPU Initialization......................................................................................................................... 3-33Debugger Access............................................................................................................................ 3-33

Working with ECC.....................................................................................................................................3-34Enabling ECC................................................................................................................................. 3-34Handling ECC Errors.................................................................................................................... 3-34Injecting ECC Errors..................................................................................................................... 3-34

Exception Processing.................................................................................................................................3-36Terminology....................................................................................................................................3-36Exception Overview.......................................................................................................................3-36Exception Latency..........................................................................................................................3-39Reset Exceptions.............................................................................................................................3-39Break Exceptions............................................................................................................................ 3-40Interrupt Exceptions...................................................................................................................... 3-41Instruction-Related Exceptions....................................................................................................3-44Other Exceptions............................................................................................................................3-49Exception Processing Flow........................................................................................................... 3-49Determining the Cause of Interrupt and Instruction-Related Exceptions.............................3-52Handling Nested Exceptions........................................................................................................ 3-54Handling Nonmaskable Interrupts..............................................................................................3-56Masking and Disabling Exceptions............................................................................................. 3-56

Memory and Peripheral Access................................................................................................................3-58Cache Memory............................................................................................................................... 3-58

Instruction Set Categories.........................................................................................................................3-60Data Transfer Instructions............................................................................................................3-60Arithmetic and Logical Instructions........................................................................................... 3-61Move Instructions.......................................................................................................................... 3-61Comparison Instructions.............................................................................................................. 3-62Shift and Rotate Instructions........................................................................................................3-62Program Control Instructions......................................................................................................3-63Other Control Instructions...........................................................................................................3-64Custom Instructions...................................................................................................................... 3-65

TOC-3

Altera Corporation

No-Operation Instruction............................................................................................................ 3-65Potential Unimplemented Instructions.......................................................................................3-65

Document Revision History.....................................................................................................................3-66

Instantiating the Nios II Processor..................................................................... 4-1Core Nios II Tab........................................................................................................................................... 4-1

Core Selection...................................................................................................................................4-2Multiply and Divide Settings.......................................................................................................... 4-3Reset Vector...................................................................................................................................... 4-3General Exception Vector............................................................................................................... 4-4Memory Management Unit Settings............................................................................................. 4-4Memory Protection Unit Settings.................................................................................................. 4-5

Caches and Memory Interfaces Tab.......................................................................................................... 4-5Instruction Master Settings.............................................................................................................4-6Data Master Settings........................................................................................................................4-7

Advanced Features Tab................................................................................................................................4-7Reset Signals......................................................................................................................................4-8Control Registers..............................................................................................................................4-8Exception Checking......................................................................................................................... 4-9Interrupt Controller Interfaces.....................................................................................................4-10Shadow Register Sets..................................................................................................................... 4-10HardCopy Compatible.................................................................................................................. 4-10ECC..................................................................................................................................................4-11

MMU and MPU Settings Tab...................................................................................................................4-11MMU............................................................................................................................................... 4-12MPU.................................................................................................................................................4-12

JTAG Debug Module Tab..........................................................................................................................4-13Debug Level Settings......................................................................................................................4-14Debug Signals................................................................................................................................. 4-15Break Vector....................................................................................................................................4-15Advanced Debug Settings............................................................................................................. 4-16

Custom Instruction Tab............................................................................................................................ 4-16Altera-Provided Custom Instructions.........................................................................................4-16

The Quartus II IP File................................................................................................................................4-18Document Revision History.....................................................................................................................4-19

Nios II Core Implementation Details................................................................. 5-1Device Family Support................................................................................................................................ 5-3Nios II/f Core................................................................................................................................................5-4

Overview........................................................................................................................................... 5-4Arithmetic Logic Unit..................................................................................................................... 5-4Memory Access.................................................................................................................................5-6Tightly-Coupled Memory............................................................................................................... 5-9Memory Management Unit............................................................................................................ 5-9Memory Protection Unit...............................................................................................................5-10Execution Pipeline......................................................................................................................... 5-10Instruction Performance............................................................................................................... 5-11

TOC-4

Altera Corporation

Exception Handling....................................................................................................................... 5-12ECC..................................................................................................................................................5-13JTAG Debug Module..................................................................................................................... 5-15

Nios II/s Core............................................................................................................................................. 5-15Overview......................................................................................................................................... 5-16Arithmetic Logic Unit................................................................................................................... 5-16Memory Access.............................................................................................................................. 5-17Tightly-Coupled Memory.............................................................................................................5-18Execution Pipeline......................................................................................................................... 5-18Instruction Performance............................................................................................................... 5-19Exception Handling....................................................................................................................... 5-20JTAG Debug Module..................................................................................................................... 5-20

Nios II/e Core............................................................................................................................................. 5-20Overview......................................................................................................................................... 5-21Arithmetic Logic Unit................................................................................................................... 5-21Memory Access.............................................................................................................................. 5-21Instruction Execution Stages........................................................................................................ 5-21Instruction Performance............................................................................................................... 5-22Exception Handling....................................................................................................................... 5-22JTAG Debug Module..................................................................................................................... 5-22

Document Revision History.....................................................................................................................5-23

Nios II Processor Revision History.....................................................................6-1Nios II Versions............................................................................................................................................ 6-1Architecture Revisions.................................................................................................................................6-3Core Revisions.............................................................................................................................................. 6-4

Nios II/f Core....................................................................................................................................6-4Nios II/s Core....................................................................................................................................6-6Nios II/e Core................................................................................................................................... 6-7

JTAG Debug Module Revisions................................................................................................................. 6-8Document Revision History....................................................................................................................... 6-9

Application Binary Interface...............................................................................7-1Data Types.....................................................................................................................................................7-1Memory Alignment..................................................................................................................................... 7-2Register Usage...............................................................................................................................................7-2Stacks............................................................................................................................................................. 7-3

Frame Pointer Elimination............................................................................................................. 7-4Call Saved Registers......................................................................................................................... 7-4Further Examples of Stacks.............................................................................................................7-4Function Prologues.......................................................................................................................... 7-6

Arguments and Return Values................................................................................................................... 7-7Arguments.........................................................................................................................................7-7Return Values....................................................................................................................................7-8

DWARF-2 Definition...................................................................................................................................7-9Object Files....................................................................................................................................................7-9Relocation..................................................................................................................................................... 7-9

TOC-5

Altera Corporation

ABI for Linux Systems...............................................................................................................................7-12Linux Toolchain Relocation Information................................................................................... 7-12Linux Function Calls..................................................................................................................... 7-16Linux Operating System Call Interface....................................................................................... 7-16Linux Process Initialization.......................................................................................................... 7-17Linux Position-Independent Code.............................................................................................. 7-18Linux Program Loading and Dynamic Linking........................................................................ 7-20Linux Conventions.........................................................................................................................7-22Development Environment.......................................................................................................... 7-23

Document Revision History.....................................................................................................................7-23

Instruction Set Reference.................................................................................... 8-1Word Formats...............................................................................................................................................8-1

I-Type.................................................................................................................................................8-1R-Type................................................................................................................................................8-1J-Type.................................................................................................................................................8-2

Instruction Opcodes.................................................................................................................................... 8-2Assembler Pseudo-Instructions................................................................................................................. 8-4Assembler Macros........................................................................................................................................8-5Instruction Set Reference............................................................................................................................ 8-5

add .....................................................................................................................................................8-6addi ....................................................................................................................................................8-8and ...................................................................................................................................................8-10andhi ............................................................................................................................................... 8-10andi ..................................................................................................................................................8-11beq ...................................................................................................................................................8-12bge ................................................................................................................................................... 8-12bgeu..................................................................................................................................................8-13bgt.....................................................................................................................................................8-14bgtu ................................................................................................................................................. 8-14ble .................................................................................................................................................... 8-15bleu ..................................................................................................................................................8-15blt .....................................................................................................................................................8-15bltu................................................................................................................................................... 8-16bne ...................................................................................................................................................8-17br ......................................................................................................................................................8-18break ................................................................................................................................................8-18bret .................................................................................................................................................. 8-19call ................................................................................................................................................... 8-20callr ..................................................................................................................................................8-21cmpeq ............................................................................................................................................. 8-21cmpeqi ............................................................................................................................................ 8-22cmpge ..............................................................................................................................................8-23cmpgei .............................................................................................................................................8-24cmpgeu ........................................................................................................................................... 8-24cmpgeui .......................................................................................................................................... 8-25cmpgt .............................................................................................................................................. 8-26cmpgti ............................................................................................................................................. 8-26

TOC-6

Altera Corporation

cmpgtu ............................................................................................................................................ 8-27cmpgtui ...........................................................................................................................................8-27cmple................................................................................................................................................8-28cmplei ..............................................................................................................................................8-28cmpleu ............................................................................................................................................ 8-29cmpleui ........................................................................................................................................... 8-29cmplt ............................................................................................................................................... 8-30cmplti .............................................................................................................................................. 8-30cmpltu ............................................................................................................................................. 8-31cmpltui ............................................................................................................................................8-32cmpne ............................................................................................................................................. 8-33cmpnei ............................................................................................................................................ 8-33custom ............................................................................................................................................ 8-34div ....................................................................................................................................................8-35divu ................................................................................................................................................. 8-36eret ...................................................................................................................................................8-37flushd .............................................................................................................................................. 8-38flushda ............................................................................................................................................ 8-40flushi ................................................................................................................................................8-41flushp ...............................................................................................................................................8-42initd ................................................................................................................................................. 8-43initda ............................................................................................................................................... 8-44initi .................................................................................................................................................. 8-46jmp .................................................................................................................................................. 8-47jmpi ................................................................................................................................................. 8-47ldb / ldbio ....................................................................................................................................... 8-48ldbu / ldbuio ...................................................................................................................................8-49ldh / ldhio .......................................................................................................................................8-51ldhu / ldhuio .................................................................................................................................. 8-52ldw / ldwio ......................................................................................................................................8-53mov ..................................................................................................................................................8-55movhi .............................................................................................................................................. 8-55movi ................................................................................................................................................ 8-56movia .............................................................................................................................................. 8-56movui .............................................................................................................................................. 8-57mul .................................................................................................................................................. 8-57muli ................................................................................................................................................. 8-59mulxss ............................................................................................................................................. 8-59mulxsu ............................................................................................................................................ 8-60mulxuu ............................................................................................................................................8-61nextpc ..............................................................................................................................................8-62nop .................................................................................................................................................. 8-63nor ................................................................................................................................................... 8-63or ..................................................................................................................................................... 8-64orhi .................................................................................................................................................. 8-64ori .................................................................................................................................................... 8-65rdctl ................................................................................................................................................. 8-66rdprs ................................................................................................................................................ 8-66ret .....................................................................................................................................................8-67

TOC-7

Altera Corporation

rol .................................................................................................................................................... 8-68roli ................................................................................................................................................... 8-68ror ....................................................................................................................................................8-69sll ..................................................................................................................................................... 8-70slli .................................................................................................................................................... 8-70sra .................................................................................................................................................... 8-71srai ................................................................................................................................................... 8-72srl ..................................................................................................................................................... 8-72srli ....................................................................................................................................................8-73stb / stbio l....................................................................................................................................... 8-74sth / sthio ........................................................................................................................................8-75stw / stwio .......................................................................................................................................8-76sub.................................................................................................................................................... 8-78subi .................................................................................................................................................. 8-80sync ................................................................................................................................................. 8-80trap .................................................................................................................................................. 8-81wrctl ................................................................................................................................................ 8-82wrprs ............................................................................................................................................... 8-82xor ................................................................................................................................................... 8-83xorhi ................................................................................................................................................8-84xori .................................................................................................................................................. 8-84

Document Revision History.....................................................................................................................8-85

TOC-8

Altera Corporation

Introduction 12016.06.17

NII5V1 NII51001 Subscribe Send Feedback

This handbook describes the Nios® II Classic processor from a high-level conceptual description to thelow-level details of implementation. The chapters in this handbook describe the Nios II processor architec‐ture, the programming model, and the instruction set.

We have ended development of new Nios II Classic processor features with the Quartus II 14.0 release.New Nios II processor features are implemented only in the Nios II Gen 2 processor core. Although theClassic processor remains supported, we recommend that you use the Gen 2 core for future designs.

This handbook assumes you have a basic familiarity with embedded processor concepts. You do not needto be familiar with any specific Altera technology or with Altera development tools. This handbook limitsdiscussion of hardware implementation details of the processor system. The Nios II processors aredesigned for Altera® FPGA devices, and so this handbook does describe some FPGA implementationconcepts. Your familiarity with FPGA technology provides a deeper understanding of the engineeringtrade-offs related to the design and implementation of the Nios II processor.

This chapter introduces the Altera Nios II embedded processor family and describes the similarities anddifferences between the Nios II processor and traditional embedded processors.

Related InformationLiterature: Nios II ProcessorThis handbook is the primary reference for the Nios II family of embedded processors and is part of alarger collection of documents covering the Nios II processor and its usage that you can find on theLiterature: Nios II Processor Page of the Altera website.

Nios II Processor System BasicsThe Nios II processor is a general-purpose RISC processor core with the following features:

• Full 32-bit instruction set, data path, and address space• 32 general-purpose registers• Optional shadow register sets• 32 interrupt sources• External interrupt controller interface for more interrupt sources• Single-instruction 32 × 32 multiply and divide producing a 32-bit result• Dedicated instructions for computing 64-bit and 128-bit products of multiplication• Optional floating-point instructions for single-precision floating-point operations• Single-instruction barrel shifter

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos aretrademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified astrademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performanceof its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to anyproducts and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of devicespecifications before relying on any published information and before placing orders for products or services.

ISO9001:2008Registered

www.altera.com101 Innovation Drive, San Jose, CA 95134

• Access to a variety of on-chip peripherals, and interfaces to off-chip memories and peripherals• Hardware-assisted debug module enabling processor start, stop, step, and trace under control of the

Nios II software development tools• Optional memory management unit (MMU) to support operating systems that require MMUs• Optional memory protection unit (MPU)• Software development environment based on the GNU C/C++ tool chain and the Nios II Software

Build Tools (SBT) for Eclipse• Integration with Altera’s SignalTap® II Embedded Logic Analyzer, enabling real-time analysis of

instructions and data along with other signals in the FPGA design• Instruction set architecture (ISA) compatible across all Nios II processor systems• Performance up to 250 DMIPS• Optional error correcting code (ECC) support for a subset of Nios II processor internal RAM blocks

A Nios II processor system is equivalent to a microcontroller or “computer on a chip” that includes aprocessor and a combination of peripherals and memory on a single chip. A Nios II processor systemconsists of a Nios II processor core, a set of on-chip peripherals, on-chip memory, and interfaces to off-chip memory, all implemented on a single Altera device. Like a microcontroller family, all Nios IIprocessor systems use a consistent instruction set and programming model.

Getting Started with the Nios II ProcessorThe easiest way to start designing effectively is to use an Altera development kit that includes a ready-made development board and the Nios II Embedded Design Suite (EDS) containing all the softwaredevelopment tools necessary to write Nios II software.

The Nios II EDS includes the following two closely-related software development tool flows:

• The Nios II SBT• The Nios II SBT for Eclipse

Both tools flows are based on the GNU C/C++ compiler. The Nios II SBT for Eclipse™ provides a familiarand established environment for software development. Using the Nios II SBT for Eclipse, you canimmediately begin developing and simulating Nios II software applications.

The Nios II SBT also provides a command line interface.

Using the Nios II hardware reference designs included in an Altera development kit, you can prototype anapplication running on a board before building a custom hardware platform.

1-2 Getting Started with the Nios II ProcessorNII5V1 NII51001

2016.06.17

Altera Corporation Introduction

Send Feedback

Figure 1-1: Example of a Nios II Processor System

Nios IIProcessor Core

SDRAMController

On-Chip ROM

Tristate bridge tooff-chip memory

Syste

m In

terco

nnec

t Fab

ric

JTAG Debug Module

SDRAMMemory

FlashMemory

SRAMMemory

UART

Timer1

Timer2

LCD Display Driver

General-Purpose I/O

Ethernet Interface

CompactFlash Interface

LCD Screen

EthernetMAC/PHY

Compact Flash

Buttons, LEDs, etc.

TXDRXD

JTAG connectionto software debugger

Clock

Rese

t

Data

Inst.

If the prototype system adequately meets design requirements using an Altera-provided reference design,you can copy the reference design and use it without modification in the final hardware platform.Otherwise, you can customize the Nios II processor system until it meets cost or performance require‐ments.

Related InformationAll Development KitsFor a list of available development kits, refer to the All Development Kits page of the Altera website.

Customizing Nios II Processor DesignsIn practice, most FPGA designs implement some extra logic in addition to the processor system. AlteraFPGAs provide flexibility to add features and enhance performance of the Nios II processor system. Youcan also eliminate unnecessary processor features and peripherals to fit the design in a smaller, lower-costdevice.

NII5V1 NII510012016.06.17 Customizing Nios II Processor Designs 1-3

Introduction Altera Corporation

Send Feedback

Because the pins and logic resources in Altera devices are programmable, many customizations arepossible:

• You can rearrange the pins on the chip to simplify the board design. For example, you can moveaddress and data pins for external SDRAM memory to any side of the chip to shorten board traces.

• You can use extra pins and logic resources on the chip for functions unrelated to the processor. Extraresources can provide a few extra gates and registers as glue logic for the board design; or extraresources can implement entire systems. For example, a Nios II processor system consumes only 5% ofa large Altera FPGA, leaving the rest of the chip’s resources available to implement other functions.

• You can use extra pins and logic on the chip to implement additional peripherals for the Nios IIprocessor system. Altera offers a library of peripherals that easily connect to Nios II processor systems.

Configurable Soft Processor Core ConceptsThis section introduces Nios II concepts that are unique or different from other discrete microcontrollers.The concepts described in this section provide a foundation for understanding the rest of the featuresdiscussed in this handbook.

Configurable Soft Processor CoreThe Nios II processor is a configurable soft IP core, as opposed to a fixed, off-the-shelf microcontroller.You can add or remove features on a system-by-system basis to meet performance or price goals. Softmeans the processor core is not fixed in silicon and can be targeted to any Altera FPGA family.

You are not required to create a new Nios II processor configuration for every new design. Altera providesready-made Nios II system designs that you can use as is. If these designs meet your system requirements,there is no need to configure the design further. In addition, you can use the Nios II instruction setsimulator to begin writing and debugging Nios II applications before the final hardware configuration isdetermined.

Flexible Peripheral Set and Address MapA flexible peripheral set is one of the most notable differences between Nios II processor systems and fixedmicrocontrollers. Because the Nios II processor is implemented in programmable logic, you can easilybuild made-to-order Nios II processor systems with the exact peripheral set required for the targetapplications.

Altera provides software constructs to access memory and peripherals generically, independently ofaddress location. Therefore, the flexible peripheral set and address map does not affect applicationdevelopers.

There are two broad classes of peripherals: standard peripherals and custom peripherals.

Standard PeripheralsAltera provides a set of peripherals commonly used in microcontrollers, such as timers, serialcommunication interfaces, general-purpose I/O, SDRAM controllers, and other memory interfaces. Thelist of available peripherals continues to increase as Altera and third-party vendors release newperipherals.

Related InformationEmbedded Peripherals IP User GuideFor information about the Altera-provided cores, refer to the Embedded Peripherals IP User Guide.

1-4 Configurable Soft Processor Core ConceptsNII5V1 NII51001

2016.06.17

Altera Corporation Introduction

Send Feedback

Custom Components

You can also create custom components and integrate them in Nios II processor systems. For perform‐ance-critical systems that spend most CPU cycles executing a specific section of code, it is a commontechnique to create a custom peripheral that implements the same function in hardware.

This approach offers a double performance benefit:

• Hardware implementation is faster than software.• Processor is free to perform other functions in parallel while the custom peripheral operates on data.

Related InformationCreating Qsys ComponentsFor information about creating custom components in Qsys, refer to the Creating Qsys Componentschapter in the Quartus II Handbook, Volume 1.

Custom InstructionsLike custom peripherals, custom instructions allow you to increase system performance by augmentingthe processor with custom hardware. You can achieve significant performance improvements, often on theorder of 10 to 100 times, by implementing performance-critical operations in hardware using custominstruction logic.

The custom logic is integrated into the Nios II processor’s arithmetic logic unit (ALU). Similar to nativeNios II instructions, custom instruction logic can take values from up to two source registers andoptionally write back a result to a destination register.

Because the processor is implemented on reprogrammable Altera FPGAs, software and hardwareengineers can work together to iteratively optimize the hardware and test the results of software runningon hardware.

From the software perspective, custom instructions appear as machine-generated assembly macros or Cfunctions, so programmers do not need to understand assembly language to use custom instructions.

Automated System GenerationAltera’s Qsys system integration tools fully automate the process of configuring processor features andgenerating a hardware design that you program in an Altera device. The Qsys graphical user interface(GUI) enables you to configure Nios II processor systems with any number of peripherals and memoryinterfaces. You can create entire processor systems without performing any schematic or HDL designentry. Qsys can also import HDL design files, providing an easy mechanism to integrate custom logic in aNios II processor system.

After system generation, you can download the design onto a board, and debug software executing on theboard. To the software developer, the processor architecture of the design is set. Software developmentproceeds in the same manner as for traditional, nonconfigurable processors.

OpenCore Plus EvaluationYou can evaluate the Nios II processor without a license. With Altera's free OpenCore Plus evaluationfeature, you can perform the following actions:

NII5V1 NII510012016.06.17 Custom Components 1-5

Introduction Altera Corporation

Send Feedback

• Simulate the behavior of a Nios II processor within your system.• Verify the functionality of your design, as well as evaluate its size and speed quickly and easily.• Generate time-limited device programming files for designs that include Nios II processors.• Program a device and verify your design in hardware.

You only need to purchase a license for the Nios II processor when you are completely satisfied with itsfunctionality and performance, and want to take your design to production.

Related InformationAN 320: OpenCore Plus Evaluation of MegafunctionsFor more information about OpenCore Plus, refer to AN 320: OpenCore Plus Evaluation ofMegafunctions.

Document Revision History

Table 1-1: Document Revision History

Date Version Changes

June 2016 2016.06.17 Updated introduction.

April 2015 2015.04.02 Maintenance release.

February 2014 13.1.0 • Added information on ECC support.• Removed HardCopy information.• Removed references to SOPC Builder.

May 2011 11.0.0 Added references to new Qsys system integration tool.

December 2010 10.1.0 Maintenance release.

July 2010 10.0.0 Maintenance release.

November 2009 9.1.0 • Added external interrupt controller interface information.• Added shadow register set information.

March 2009 9.0.0 Maintenance release.

November 2008 8.1.0 Maintenance release.

May 2008 8.0.0 Added MMU and MPU to bullet list of features.

October 2007 7.2.0 Added OpenCore Plus section.

May 2007 7.1.0 • Added table of contents to Introduction section.• Added Referenced Documents section.

March 2007 7.0.0 Maintenance release.

November 2006 6.1.0 Maintenance release.

1-6 Document Revision HistoryNII5V1 NII51001

2016.06.17

Altera Corporation Introduction

Send Feedback

Date Version Changes

May 2006 6.0.0 • Added single precision floating-point and integration withSignalTap® II logic analyzer to features list.

• Updated performance to 250 DMIPS.

October 2005 5.1.0 Maintenance release.

May 2005 5.0.0 Maintenance release.

September 2004 1.1 Maintenance release.

May 2004 1.0 Initial release.

NII5V1 NII510012016.06.17 Document Revision History 1-7

Introduction Altera Corporation

Send Feedback

Processor Architecture 22016.06.17

NII5V1 NII51002 Subscribe Send Feedback

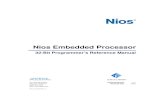

This chapter describes the hardware structure of the Nios II processor, including a discussion of all thefunctional units of the Nios II architecture and the fundamentals of the Nios II processor hardwareimplementation.

The Nios II architecture describes an instruction set architecture (ISA). The ISA in turn necessitates a setof functional units that implement the instructions. A Nios II processor core is a hardware design thatimplements the Nios II instruction set and supports the functional units described in this document. Theprocessor core does not include peripherals or the connection logic to the outside world. It includes onlythe circuits required to implement the Nios II architecture.

The Nios II architecture defines the following functional units:

• Register file• Arithmetic logic unit (ALU)• Interface to custom instruction logic• Exception controller• Internal or external interrupt controller• Instruction bus• Data bus• Memory management unit (MMU)• Memory protection unit (MPU)• Instruction and data cache memories• Tightly-coupled memory interfaces for instructions and data• JTAG debug module

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos aretrademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified astrademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performanceof its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to anyproducts and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of devicespecifications before relying on any published information and before placing orders for products or services.

ISO9001:2008Registered

www.altera.com101 Innovation Drive, San Jose, CA 95134

Figure 2-1: Nios II Processor Core Block Diagram

ExceptionController

InternalInterrupt

Controller

ArithmeticLogic Unit

GeneralPurpose

Registers

Control Registers

Nios II Processor Core

resetclock

JTAGinterface

to softwaredebugger

CustomI/O

Signals

irq[31..0]

JTAGDebug Module

ProgramController

&Address

Generation

CustomInstruction

Logic

Data Bus

Tightly CoupledData Memory

Tightly CoupledData Memory

DataCache

InstructionCache

Instruction Bus

Tightly CoupledInstruction Memory

Tightly CoupledInstruction Memory

cpu_resetrequestcpu_resettaken

MemoryManagement

Unit

Translation Lookaside

Buffer

InstructionRegions

MemoryProtection

Unit

DataRegions

ExternalInterrupt

ControllerInterface

eic_port_data[44..0]eic_port_valid

ShadowRegister

Sets

Required Module

Optional Module

Key

Processor ImplementationThe functional units of the Nios II architecture form the foundation for the Nios II instruction set.However, this does not indicate that any unit is implemented in hardware. The Nios II architecturedescribes an instruction set, not a particular hardware implementation. A functional unit can beimplemented in hardware, emulated in software, or omitted entirely.

A Nios II implementation is a set of design choices embodied by a particular Nios II processor core. Allimplementations support the instruction set defined in the Instruction Set Reference chapter.

Each implementation achieves specific objectives, such as smaller core size or higher performance. Thisflexibility allows the Nios II architecture to adapt to different target applications.

2-2 Processor ImplementationNII5V1 NII51002

2016.06.17

Altera Corporation Processor Architecture

Send Feedback

Implementation variables generally fit one of three trade-off patterns: more or less of a feature; inclusion orexclusion of a feature; hardware implementation or software emulation of a feature. An example of eachtrade-off follows:

• More or less of a feature—For example, to fine-tune performance, you can increase or decrease theamount of instruction cache memory. A larger cache increases execution speed of large programs,while a smaller cache conserves on-chip memory resources.

• Inclusion or exclusion of a feature—For example, to reduce cost, you can choose to omit the JTAGdebug module. This decision conserves on-chip logic and memory resources, but it eliminates theability to use a software debugger to debug applications.

• Hardware implementation or software emulation—For example, in control applications that rarelyperform complex arithmetic, you can choose for the division instruction to be emulated in software.Removing the divide hardware conserves on-chip resources but increases the execution time ofdivision operations.

For information about which Nios II cores supports what features, refer to the Nios II Core ImplementationDetails chapter of the Nios II Processor Reference Handbook.For complete details about user-selectable parameters for the Nios II processor, refer to the Instantiatingthe Nios II Processor chapter of the Nios II Processor Reference Handbook.

Related Information

• Instantiating the Nios II Processor on page 4-1• Instantiating the Nios II Processor• Nios II Core Implementation Details on page 5-1• Nios II Core Implementation Details• Instruction Set Reference on page 8-1• Instruction Set Reference

Register FileThe Nios II architecture supports a flat register file, consisting of thirty-two 32-bit general-purpose integerregisters, and up to thirty-two 32-bit control registers. The architecture supports supervisor and usermodes that allow system code to protect the control registers from errant applications.

The Nios II processor can optionally have one or more shadow register sets. A shadow register set is acomplete set of Nios II general-purpose registers. When shadow register sets are implemented, the CRSfield of the status register indicates which register set is currently in use. An instruction access to ageneral-purpose register uses whichever register set is active.

A typical use of shadow register sets is to accelerate context switching. When shadow register sets areimplemented, the Nios II processor has two special instructions, rdprs and wrprs, for moving databetween register sets. Shadow register sets are typically manipulated by an operating system kernel, andare transparent to application code. A Nios II processor can have up to 63 shadow register sets.

The Nios II architecture allows for the future addition of floating-point registers.

For details about shadow register set implementation and usage, refer to “Registers” and “ExceptionProcessing” in the Programming Model chapter of the Nios II Processor Reference Handbook.

For details about the rdprs and wrprs instructions, refer to the Instruction Set Reference chapter of theNios II Processor Reference Handbook.

NII5V1 NII510022016.06.17 Register File 2-3

Processor Architecture Altera Corporation

Send Feedback

Related Information

• Programming Model on page 3-1• Programming Model• Instruction Set Reference on page 8-1• Instruction Set Reference

Arithmetic Logic UnitThe Nios II ALU operates on data stored in general-purpose registers. ALU operations take one or twoinputs from registers, and store a result back in a register. The ALU supports the data operations describedin the table below. To implement any other operation, software computes the result by performing acombination of the fundamental operations.

Table 2-1: Operations Supported by the Nios II ALU

Category Details

Arithmetic The ALU supports addition, subtraction, multiplication, and division on signed andunsigned operands.

Relational The ALU supports the equal, not-equal, greater-than-or-equal, and less-thanrelational operations (==, != >=, <) on signed and unsigned operands.

Logical The ALU supports AND, OR, NOR, and XOR logical operations.Shift andRotate

The ALU supports shift and rotate operations, and can shift/rotate data by 0 to 31bit positions per instruction. The ALU supports arithmetic shift right and logicalshift right/left. The ALU supports rotate left/right.

Unimplemented InstructionsSome Nios II processor core implementations do not provide hardware to support the entire Nios IIinstruction set. In such a core, instructions without hardware support are known as unimplementedinstructions.

The processor generates an exception whenever it issues an unimplemented instruction so your exceptionhandler can call a routine that emulates the operation in software. Unimplemented instructions do notaffect the programmer’s view of the processor.

For a list of potential unimplemented instructions, refer to the Programming Model chapter of the Nios IIProcessor Reference Handbook.

Related Information

• Programming Model on page 3-1• Programming Model

2-4 Arithmetic Logic UnitNII5V1 NII51002

2016.06.17

Altera Corporation Processor Architecture

Send Feedback

Custom InstructionsThe Nios II architecture supports user-defined custom instructions. The Nios II ALU connects directly tocustom instruction logic, enabling you to implement operations in hardware that are accessed and usedexactly like native instructions.

Refer to "Custom Instruction Tab" in the Instantiating the Nios II Processor chapter of the Nios II ProcessorReference Handbook for additional information.

Related Information

• Instantiating the Nios II Processor on page 4-1• Instantiating the Nios II Processor• Nios II Custom Instruction User Guide

For more information, refer to the Nios II Custom Instruction User Guide.

Floating-Point InstructionsThe Nios II architecture supports single precision floating-point instructions with two components:

• Floating Point Hardware 2—This component supports floating-point instructions as specified by theIEEE Std 754-2008 but with simplified, non-standard rounding modes. The basic set of floating-pointcustom instructions includes single precision floating-point addition, subtraction, multiplication,division, square root, integer to float conversion, float to integer conversion, minimum, maximum,negate, absolute, and comparisons.

• Floating Point Hardware—This component supports floating-point instructions as specified by theIEEE Std 754-1985. The basic set of floating-point custom instructions includes single precisionfloating-point addition, subtraction, and multiplication. Floating-point division is available as anextension to the basic instruction set.

These floating-point instructions are implemented as custom instructions. The Hardware Conformancetable below lists a detailed description of the conformance to the IEEE standards.

NII5V1 NII510022016.06.17 Custom Instructions 2-5

Processor Architecture Altera Corporation

Send Feedback

Table 2-2: Hardware Conformance with IEEE 754-1985 and IEEE 754-2008 Floating-Point Standard

Feature Floating-Point HardwareImplementation with IEEE 754-

1985

Floating-Point Hardware 2Implementation with IEEE 754-

2008

Operations

Addition/subtraction Implemented ImplementedMultiplication Implemented ImplementedDivision Optional ImplementedSquare root Not implemented, this

operation is implemented insoftware.

Implemented

Integer to float/float tointeger

Not implemented, thisoperation is implemented insoftware.

Implemented

Minimum/maximum Not implemented, thisoperation is implemented insoftware.

Implemented

Negate/absolute Not implemented, thisoperation is implemented insoftware.

Implemented

Comparisons Not implemented, thisoperation is implemented insoftware.

Implemented

Precision

Single Implemented ImplementedDouble Not implemented. Double

precision operations areimplemented in software.

Not implemented. Doubleprecision operations areimplemented in software.

Exceptionconditions

Invalid operation Result is Not a Number (NaN) Result is Not a Number(NaN)

Division by zero Result is ±infinity Result is ±infinityOverflow Result is ±infinity Result is ±infinityInexact Result is a normal number Result is a normal numberUnderflow Result is ±0 Result is ±0

Rounding Modes

Round to nearest Implemented Implemented (roundTiesTo‐Away mode)

Round toward zero Not implemented Implemented (truncationmode)

Round toward +infinity Not implemented Not implementedRound toward –infinity Not implemented Not implemented

2-6 Floating-Point InstructionsNII5V1 NII51002

2016.06.17

Altera Corporation Processor Architecture

Send Feedback

Feature Floating-Point HardwareImplementation with IEEE 754-

1985

Floating-Point Hardware 2Implementation with IEEE 754-

2008

NaN

Quiet Implemented No distinction is madebetween signaling and quietNaNs as input operands. Aresult that produces a NaNmay produce either asignaling or quiet NaN.

Signaling Not implemented

Subnormal(denormalized)numbers

Subnormal operands aretreated as zero. The floating-point custom instructions donot generate subnormalnumbers.

• The comparison,minimum, maximum,negate, and absoluteoperations supportsubnormal numbers.

• The add, subtract,multiply, divide, squareroot, and float to integeroperations do NOTsupport subnormalnumbers. Subnormaloperands are treated assigned zero. The floating-point custom instruc‐tions do not generatesubnormal numbers.(1)

• The integer to floatoperation cannot createsubnormal numbers.

Softwareexceptions

Not implemented. IEEE 754-1985 exception conditions aredetected and handled asdescribed elsewhere in thistable.

Not implemented. IEEE754-2008 exceptionconditions are detected andhandled as describedelsewhere in this table.(1)

Status flags Not implemented. IEEE 754-1985 exception conditions aredetected and handled asdescribed elsewhere in thistable.

Not implemented. IEEE754-2008 exceptionconditions are detected andhandled as describedelsewhere in this table.(1)

Note: The Floating Point Hardware 2 component also supports faithful rounding, which is not an IEEE754-defined rounding mode. Faithful rounding rounds results to either the upper or lower nearestsingle-precision numbers. Therefore, the result produced is one of two possible values and thechoice between the two is not defined. The maximum error of faithful rounding is 1 unit in the lastplace (ulp). Errors may not be evenly distributed.

(1) This operation is not fully compliant with IEEE 754-2008.

NII5V1 NII510022016.06.17 Floating-Point Instructions 2-7

Processor Architecture Altera Corporation

Send Feedback

Related InformationNios II Custom Instruction User GuideFor more information about using floating-point custom instructions in software, refer to the Nios IICustom Instruction User Guide.

Floating Point Custom Instruction 2 ComponentYou can add floating-point custom instructions to any Nios II processor design. The floating-pointdivision hardware requires more resources than the other instructions. The Floating Point Hardware 2component supports the following single-precision floating-point operations:

• Add• Subtract• Multiply• Divide• Square root• Comparison• Integer conversion• Minimum• Maximum• Negate• Absolute

Other floating-point operations (including double-precision operations) are implemented with softwareemulation. The component requires the following device resources:

• ~2,500 4-input LEs• 9 x 9 bit multipliers• 3x M9K memories

In the following table, a and b are assumed to be single-precision floating-point values.

Table 2-3: Floating Point Custom Instruction 2 Operation Summary

Operation(2) N(3) Cycles Result Subnormal Rounding GCCInference

fdivs 255 16 a ÷ b Flush to 0 Nearest a / bfsubs 254 5 a – b Flush to 0 Faithful a – bfadds 253 5 a + b Flush to 0 Faithful a + bfmuls 252 4 a x b Flush to 0 Faithful a * bfsqrts 251 8 a Flush to 0 Faithful sqrtf()(4)

(2) These names match the names of the corresponding GCC command-line options except for round, whichGCC does not support.

(3) Specifies the 8 bit fixed custom instruction for the operation.(4) Nios II GCC version 4.7.3 is not able to reliably replace calls to newlib floating-point functions with the

equivalent custom instruction even though it has -mcustom-<operation> command-line options andpragma support for these operations. Instead, the custom instruction must be invoked directly using theGCC __builtin_custom_* facility. The Floating Point Custom Instruction 2 component includes a Cheader file that provides the required #define macros to invoke the custom instruction directly.

2-8 Floating Point Custom Instruction 2 ComponentNII5V1 NII51002

2016.06.17

Altera Corporation Processor Architecture

Send Feedback

Operation(2) N(3) Cycles Result Subnormal Rounding GCCInference

floatis 250 4 int_to_float(a) Notapplicable

Notapplicable

Casting

fixsi 249 2 float_to_int(a) Flush to 0 Truncation Castinground 248 2 float_to_int(a) Flush to 0 Nearest lroundf()(

4)

Reserved 234 to 247 Undefined Undefinedfmins 233 1 (a < b) ? a : b Supported None fminf()(4)

fmaxs 232 1 (a < b) ? b : a Supported None fmaxf()(4)

fcmplts 231 1 (a < b) ? 1 : 0 Supported None a < bfcmples 230 1 (a ≤ b) ? 1 : 0 Supported None a <= bfcmpgts 229 1 (a > b) ? 1 : 0 Supported None a > bfcmpges 228 1 (a ≥ b) ? 1 : 0 Supported None a >= bfcmpeqs 227 1 (a = b) ? 1 : 0 Supported None a == bfcmpnes 226 1 (a ≠ b) ? 1 : 0 Supported None a != bfnegs 225 1 -a Supported None -afabss 224 1 |a| Supported None fabsf()

The cycles column specifies the number of cycles required to execute the instruction. A combinatorialcustom instruction takes 1 cycle. A multi-cycle custom instruction requires at least 2 cycles. An N-cyclemulti-cycle custom instruction has N - 2 register stages inside the custom instruction because the Nios IIprocessor registers the result from the custom instruction and allows another cycle for g wire delays in thesource operand bypass multiplexers. The number of cycles does not include the extra cycles (maximum of2) that an instruction following the multi-cycle custom instruction is stalled by the Nios II/f if the instruc‐tion uses the result within 2 cycles. These extra cycles occur because multi-cycle instructions are late resultinstructions

In Qsys, the Floating Point Hardware 2 component is under Embedded Processors on the ComponentLibrary tab.

The Nios II Software Build Tools (SBT) include software support for the Floating Point Custom Instruc‐tion 2 component. When the Floating Point Custom Instruction 2 component is present in hardware, theNios II compiler compiles the software codes to use the custom instructions for floating point operations.