MOSFET

-

Upload

vitthal-talawar -

Category

Documents

-

view

101 -

download

0

Transcript of MOSFET

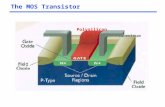

2004 Sergio Franco Ch. 3 - MOSFETs Page 1 ofMOS FIELD-EFFECT TRANSISTORS2004 Sergio FrancoSan Francisco State University(Updated February 9, 2005)No part of these notes may be reproduced, stored, transmitted, or distributed in any form or by any means, electronicor in photocopy form, without the prior written permission by the author. 2004 Sergio Franco.1.Device Structure2.The Threshold Voltage3.The Channels Characteristics4.The i-v Characteristics of MOSFETsThe age of semiconductor electronics begun when the triode function (a controlled current source) wasimplemented on a piece of semiconductor material.This occurred in 1947 with the invention of thebipolar junction transistor (BJT), the first working realization of the semiconductor triode concept.However, neither is the BJT the only transistor type possible, nor was it the first transistor to beconceived.In fact, as early as 1925, Julius Lilienfeld patented a device of the type nowadays known asthe field-effect transistor (FET).However, because of fabrication difficulties at the time, he could neverget it to work.It took another 35 years or so before Dawon Kahng and John Atalla of Bell Laboratoriesdemonstrated, in 1960, the first FET of the so called metal-oxide-semiconductor (MOS) type, orMOSFET for short.The closest MOSFET counterpart of the vacuum-tube triode is what is nowadays known as the n-channel depletion-type MOSFET (n-channel DMOSFET).Briefly stated, a DMOSFET consists of a thinlayer of n-type material called the channel, which forms a parallel-plate capacitor with an electrode calledthe gate.One end of the channel, called the source, acts as a copious source of free electrons, which aredesigned to flow to the opposite end of the channel, aptly called the drain.The roles of source and drainare similar to those of emitter and collector in the BJT, or cathode and plate in the triode.The role of thegate, similar to that of the base in the BJT or the grid in the triode, is to modulate the channels conduct-ivity and thus control the current flow from source to drain.Specifically, driving the gate voltagenegative will induce a positive charge in the channel, at the expense of a reduction in the concentration offree electrons there.For a sufficiently negative gate voltage, the channel will be depleted of free electronsand current flow will cease altogether.By a hydraulic analogy, FET behavior can be likened to a gardenhose being squeezed for the purpose of controlling water flow, or even shutting it off completely.Following the successful demonstration of the first MOSFET, the new technology was put to useespecially in those applications in which the advantages of smaller size and lower power consumption ofthe MOSFET made it competitive with its BJT counterpart.The first battery-powered electroniccalculators and wristwatches made use precisely of this new technology.Also, a new digital integrated-circuit (IC) family known as complementary MOS (or CMOS for short) was introduced by RCA as a low-power alternative to the existing IC bipolar families of the TTL and ECL types.In 1971 Intel used MOStechnology to develop the first microprocessor.Since then, IC electronics has advanced exponentiallyand has penetrated virtually every aspect of modern life.This impressive growth has been governed byMoores law, roughly stating that thanks to continued advances in IC fabrication, the number of devicesthat can be integrated on a given chip area doubles every approximately 18 months.Originally 2004 Sergio Franco Ch. 3 - MOSFETs Page 2 offormulated in 1965, this law still holds to this day, though it has been observed that technology is boundto approach physical limits that will eventually lead to the demise of this law.Over the years, the MOSFET has overtaken its BJT predecessor especially in high-density ICselectronics, thanks to the aforementioned MOSFET advantages of smaller size and lower powerconsumption.Nonetheless, there are applications such as high-performance analog electronics, in whichthe BJT continues to be the preferred transistor type.To exploit the advantages of both BJTs andMOSFETs, the two device types are sometimes fabricated simultaneously on the same chip.Theresulting technology, aptly called biCMOS technology, provides even greater design opportunities thanthe all-BJT or all-MOSFET technologies individually.Also, contemporary ICs often combine digital aswell as analog functions on the same chip, this being the reason for the name mixed-signal or also mixed-mode ICs.There is no question that microelectronics is one of the most exciting, challenging, and rapidlyevolving fields of human endeavor.The beginner may feel overwhelmed by all this, and rightly so.But,as we embark upon the study of todays dominant processes and devices, we will try to focus on generalprinciples that transcend the particular technological milieu of the moment and that we can apply tounderstand new processes and devices as they become available and commercially mature.Focus ongeneral principles, combined with continuing education, is a necessity for the young engineer aiming atestablishing and maintaining a satisfying career in a seemingly ever-changing field.This chapter begins with a study of the physical structure of the MOSFET, the underlyingsemiconductor principles, and the devices electrical characteristics.The devices under scrutiny are of theso-called long-channel type (channel lengths > 1 m).Their behavior conforms fairly well to theoreticalprediction, so they are easier to model and the beginner will find them easier to grasp.However, thedevices available in todays ever shrinking IC processes are of the short-channel type (channel lengths offractions of 1 m).At such smaller sizes, a number of higher-order effects arise, particularly carriervelocity saturation, which may cause significant departure from long-channel behavior.Aptly calledshort-channel effects, they require more complex formalism and sophisticated models as the price forproviding more realistic results.These advanced models, while realizable in computer simulation, are toocomplicated for hand analysis.We shall nevertheless continue to rely on the formalism and models oflong-channel devices to gain a quick if only approximate feel for device behavior, and then turn tocomputer simulation for more accurate results.Next, we investigate the FET in its two most important applications, namely, as an amplifier inanalog electronics, and as a switch in digital electronics.Basic single-transistor amplifier configurationsare covered in detail, along with a variety of circuit examples.The amplifiers investigated are of the so-called discrete type, because they can be built using discrete transistors, resistors, and capacitors.(In thisrespect, a very convenient device to experiment with in the lab is the CD4007 CMOS Transistor Array.)Though nowadays MOSFET amplifiers are implemented in IC form, the motivation for studying discretedesigns is primarily pedagogical as discrete circuits are somewhat easier to grasp, and yet they revealimportant aspects that apply to IC implementations as well.Once we master the basics of discrete design,we will be in a better position to tackle the more sophisticated techniques of IC amplifier design as weproceed.The chapter concludes with a detailed analysis of the CMOS inverter/amplifier as a simple yetimportant IC building block that demonstrates the unique advantages of CMOS technology both in theanalog and digital domains.Basic CMOS logic gates are also addressed. 2004 Sergio Franco Ch. 3 - MOSFETs Page 3 of1.Device StructureFigure 1 shows, in simplified form, the structure of the n-channel, metal-oxide-semiconductor (MOS)field-effect transistor (FET), or nMOSFET for short.The device is fabricated through a complexsequence of steps involving pattern definition, oxidation, diffusion, ion implantation, material depositionand material removal, on a wafer of lightly-doped p-type silicon (p) called the body or also the bulk ofthe nMOSFET.The wafer is also called the substrate because it provides physical support for the deviceunder consideration as well as all other devices of the same integrated circuit (IC).Starting out with a polished wafer, the fabrication of an nMOSFET consists of the followingprincipal steps:The first step is the thermal growth of a thin (tox) insulating layer of silicon oxide (SiO2) on thesurface of the substrate.Next, the gate electrode is created by growing over the oxide a layer of heavily-doped n-type silicon(n+).Being extremely rich in free electrons, this electrode acts for all practical purposes like a metal.The resulting metal-oxide-semiconductor (MOS) structure is the reason for the name of the device.Next, ion implantation is used to create two heavily-doped n-type regions (n+) at each side of the gate.Finally, two metal depositions form the source and drain electrodes.The region of the body just below the oxide is called the channel region.Its length and width aredenoted as L and W, respectively.In current VLSI technology, L and W can be as small as fractions of amicrometer (1 m = 106 m = 104 cm), while the oxide thickness tox can be as low as ten nanometers (1nm = 109 m = 107 cm = 10 ).We identify two basic ingredients in a MOSFET:The channel region extending between the source and drain regions, andThe parallel-plate capacitor formed by the gate and the channel region.Briefly stated, the principle at the basis of the MOSFET is to utilize this gate-body capacitance to controlthe channel-region conductance.Since the path extending from the source to the drain regions includestwo back-to-back pn junctions (the body-source and the body-drain junctions), this path normally exhibitsvery high resistance to current flow (typically ~1012 ).However, by raising potential of the gateelectrode to a suitable value, we can create favorable conditions for free electrons to exist in the channelregion, and thus form a continuous conductive path, or channel, from source to drain, along whichelectrons can flow and produce current.To investigate device behavior, we need to address two issues:What is the threshold voltage Vt to which we need to raise the gate potential relative to the bulk toform a channel and thus turn on the device?Once the device has been turned on, what are the i-v characteristics of its channel?Fig. 1 Basic physical structure of the nMOSFET. 2004 Sergio Franco Ch. 3 - MOSFETs Page 4 ofBoth issues will be addressed further down.Complementary MOSFETsThe dominant IC technology today utilizes the nMOSFET as well as its dual (or complementary) device,the pMOSFET.Aptly called complementary MOS (or CMOS) technology, it requires that both devicetypes be fabricated on the same substrate.A pMOSFET is obtained by negating the doping types of thebody, source, and drain regions of an nMOSFET, so that the body is now n, and the source and drainregions are p+.To allow for the coexistence of the two devices on a common substrate, the pMOSFET isplaced inside a local lightly doped n-type (n) substrate, also called well or tub, which is formed by aseparate diffusion into the existing p wafer prior to the fabrication of the transistors themselves.The structure is depicted in cross-sectional form in Fig. 2, where subscripts n and p identify theterminals of the nMOSFET and the pMOSFET, respectively.The nMOSFET, located left of center, issimilar to that of Fig. 1, except that the connection to its body (Bn) is not at the bottom, as shown in thesimplified rendition of Fig. 1, but at the top.This is mandated by the planar-IC requirement that allinterconnections be made at the top of the wafer.The pMOSFET, located right of center, is placed insideits own well (n), and connection to the well (Bp) is at the top, right.To ensure good-quality ohmiccontacts, the metal connections to the bulks are implemented thorough heavily doped regions, as shown.Figure 2 illustrates also another important aspect of ICs, namely, the need for adjacent devices tobe electrically isolated from each other.This constraint is met by growing, prior to fabrication of theactual transistors, a ring of SiO2 insulator material, also called field oxide, around each transistorsintended site.Indeed, each transistor must be kept electrically isolated not only from its neighboringdevices, but also from its own body!The p-type body of the nMOSFET forms pn junctions with then-type source and drain regions, so in this case body isolation is achieved by anchoring Bn to the mostnegative voltage (MNV) in the circuit.This will keep both junctions reverse biased, and therefore incutoff, under all possible circuit conditions.Likewise, the n-type well of the pMOSFET forms npjunctions with the p-type source and drain regions, so anchoring Bp to the most positive voltage (MPV) inthe circuit will keep both junctions in cutoff under all possible circuit conditions.For instance, in the caseof a digital CMOS circuit powered between 5 V and ground, Bn is connected to ground, and Bp isconnected to +5 V.These connections are made internally to the IC by the manufacturer.Fig. 2 Cross-sectional view of CMOS transistors. 2004 Sergio Franco Ch. 3 - MOSFETs Page 5 of2.The Threshold VoltageTo investigate the process of channel formation in an nMOSFET, we focus on its gate-oxide-bulkstructure, which forms a parallel-plate capacitor, albeit one with plates of different materials.Though inearlier MOSFETs the gate electrode was made of metal, such as aluminum, nowadays the gate isfabricated using n+ silicon, this being the reason why modern processes is also referred to as silicon-gateprocesses.Since the n+ silicon film is grown over amorphous oxide, it consists of sub-micrometer-sizedcrystallites, rather than a single crystal, and it is thus referred to a polysilicon.Regardless, n+ polysiliconis very rich in free electrons, just like a metal, and is used not only to create the gate electrode, but also tointerconnect different devices in an IC.The reason for making the gate electrode of polysilicon is that thesubsequent ion implantation creating the source and drain regions will inherently guarantee a high degreeof alignment among the different regions.In particular, as the ions diffuse downward into the body, theyalso diffuse sideways a bit, resulting in a small amount of overlap between the edges of the gate and thoseof the source and drain regions.As we proceed, we shall appreciate how this slight overlap, clearlyshown in both pictures above, is critical to the proper functioning of the MOSFET.We now wish to investigate the effect of an external bias upon the type of charges as well as theirdistributions in the body region just below the oxide layer.Since no current flows through the insulatingoxide layer, the only means for the gate to effect the properties of the channel region is via the electricfield inside the oxide.Hence, the designation field-effect transistor (FET).The Gate-Body CapacitorFigure 3 shows a section of the gate-oxide-body structure of Fig. 1, but rotated counterclockwise by 90.As mentioned in connection with Fig. 2, the function of the p+ region is to ensure a good-quality ohmiccontact between the p bulk and the metal connection, so it will play no role in our analysis.The well-known formula for parallel-plate capacitance gives, in the present case, C = ox(WL)/tox, where W and Lare the channel-regions width and length depicted in Fig. 1, ox is the permittivity of the oxide layer, andtox is its thickness.To make analysis independent of the particular device size, it is convenient to workwith the capacitance per unit area,oxoxoxCt= (1) (a)(b)Fig. 3 - Gate-body capacitor (a) at 0-V bias, and (b) biased at 0 to eliminate the space-charge layers. 2004 Sergio Franco Ch. 3 - MOSFETs Page 6 ofGiven that silicon oxide has ox = 345 fF/cm, a fabrication process with, say, tox = 10 nm gives Cox = 345nF/cm2, or3.45 fF/(m)2, as it is frequently expressed.The gate-oxide-bulk structure is reminiscent of the familiar pn junction, except that the n and pmaterials are now separated by an insulator layer that prevents direct current flow.However, if anexternal conducting path is established, for instance by shorting G and B with a wire as in Fig. 3a,electrons will diffuse from the electron-rich n+ gate, through the wire, to the electron-starved p bulk,leaving behind a layer of immobile positive donor ions in the gate.Once in the bulk, these electronsrecombine with holes there, leading in turn to the formation of a layer of immobile negative acceptor ionsin the bulk.Being attracted to each other, the two layers will be concentrated near the gate-oxide andsilicon-oxide interfaces, respectively.Just as in the case of the pn junction, the creation of these space-charge layers results in an electric field from the gate, through the oxide, to the bulk, and an equilibriumcondition is reached whereby this field will oppose any further diffusion of electrons.Associated withthis field is a built-in potential 0 across the gate-bulk structure, 0 = n p, wherelnip TAnVN = (2a)is the equilibrium electrostatic potential, also called Fermi potential, of the bulk, andlnDn TiNVn = (2b)is the equilibrium electrostatic potential, or Fermi potential of the gate.Here, VT = kT/q is the thermalvoltage (VT 26 mV at T = 300 K), NA and ND are the doping densities in the bulk and gate materials, andni is the intrinsic electron-hole concentration of silicon (ni 1.451010/cm3).Since both NA and ND aregreater than ni, we have p < 0 and n > 0.Moreover, since NA and ND appear in the argument of thelogarithmic function, p and n are not overy sensitive to variations in the doping doses.An ordinary capacitance with its plates shorted together will be in the discharged state.However,if the plates are of dissimilar materials, as in the present case, we have Q 0 even though VGB = 0!If wewant to drive Q to zero, we need to apply a voltage VGB of equal magnitude but opposite polarity as 0, orVGB = 0 = p n < 0 (see Fig. 3b).This value of VGB is also called the flatband voltage because of itseffect on the energy bands of the bulk material.We shall use this voltage as the reference voltage for ouranalysis to follow.Example 1Assuming NA = 1016/cm3 and ND = 1020/cm3, find the electrostatic potentials as well as the value of VGBneeded to eliminate the space-charge layers.SolutionFrom Eq. (2),10161.45 100.026ln10p= =0.35 V2010100.026ln1.45 10n = = +0.59 VTo achieve charge neutrality in the gate and bulk, the gate must be biased more negative than the body byVGB = 0 = 0.35 0.59 = 0.94 V.RemarkWere the gate-bulk a regular np junction, with VGB = 0.94 V it would be forward-biased quite heavily, 2004 Sergio Franco Ch. 3 - MOSFETs Page 7 ofthus conducting a large forward current from the p-bulk to the n-gate.In the present case, however, nocurrent flows because of the oxide insulator separating the two, giving further credence to the name FET.InversionLet us now gradually increase VGB, starting at VGB = 0 (or VGB = 0.94 V in our example).The effect ofthis increase is to re-establish space charge-layers on both sides of the oxide, uncovering positive chargein the gate and negative charge in the bulk.We are particularly interested in the situation in the bulk, sowe will ignore that in the gate, keeping in mind that the charge in the gate is always of equal magnitudebut opposite polarity as the charge in the bulk.The situation in the bulk is depicted in Fig. 4, where wehave chosen the origin of the x-axis to coincide with the oxide-bulk interface, a surface that will play animportant role in our analysis.Initially, the negative charge in the bulk results from the negative acceptorions there: the holes are simply pushed away from the oxide-bulk interface, leaving behind the boundions.The resulting space-charge layer is also referred to as a depletion layer because it is devoid of holes.However, as we increase VGB from 0, not only does the depletion layer in the bulk widen, but also thesurface potential (0) increases.When (0) changes from negative to positive, the bulk near the surfaceFig. 4 The situation in an nMOSFETjust before the onset of strong inversion. 2004 Sergio Franco Ch. 3 - MOSFETs Page 8 ofis said to undergo inversion because it turns from p-type to n-type, at least electrostatically speaking.Forthis reason, the bulk region near the surface is called inversion layer.With reference to Fig. 4, we observe that the formation of the space-charge layers results in thecreation of an electric field E(x).The field strength as a function of x is readily visualized by counting thefield lines, each of which starts on a positive ion in the gate and ends on a negative ion in the bulk.Weare interested in the lines in the bulk, which is maximum at the oxide-bulk interface (x = 0), and decreaseslinearly with x to finally drop to zero at the edge of the depletion layer (x = xp).We can readily find arelationship between the maximum strength Em and the layers width xp using Gauss theorem.In a one-dimensional case such as ours, this theorem is expressed as dE/dx = /si, where is the charge density inthe depletion layer ( = qNA), and si is silicons permittivity (si = 1.04 pF/cm).By inspection, we havedE/dx = Em/xp = qNA/si, soA pmsiqNxE= (3)Electric field and potential are in turn related as E = d/dx.Rewriting as d= Edx and integratingboth sides from x = 0 to x = xp, we get 0 0( )p px xd Ex dx = The term on the left is simply the difference p (0), while the term on the right is the just area of thetriangle under the E curve, or (xpEm), so(0)2m ppEx = Using Eq. (3) to eliminate Em, we obtain an expression for the depletion-layer width as a function of thesurface potential (0),2(0)sip pAxqN ( = Onset of Strong InversionWe are interested in the situation at which the surface potential attains the value (0) = p (or+0.35 V in our example), for then the electron concentration n in the inversion layer becomes equal to thehole concentration p in the bulk, or n = NA (= 1016/cm3 in our example).This situation is said to mark theonset of strong inversion.Using subscript 0 to mark this onset, we now wish to find the gate-body biasVGB0 required to bring about this onset itself.To this end, we first substitute (0) = p to find thedepletion-layer width at the onset of strong inversion022( )sip pAxqN = (4)Next, we observe that the unit-area charge in the bulk depletion-layer is Qb0 = qNAxp0.Using Eq. (4),02 2( )b A si pQ qN = (5) 2004 Sergio Franco Ch. 3 - MOSFETs Page 9 ofThis negative bulk charge is matched by a positive charge of equal magnitude in the gate.By thecapacitance law, the voltage required to sustain this charge situation is Vox = Qb0/Cox.Finally, the gate-to-body voltage drop required to bring about the onset of strong inversion is, by KVL, VGB0 = 0 + 2(p)+ Vox, or00 02bGB poxQVC = (6)In words: to bring about the onset of strong inversion, we need to increase VGB, starting from thereference level 0, first by the term 2(p) to raise the surface potential (0) from p, through zero, top, and then by the term Qb0/Cox to sustain the unit-area charge Qb0 in the bulk depletion-layer.Example 2Assuming the doping densities of Example 1, along with tox = 25 nm, find the values of all relevantphysical quantities at the onset of strong inversion.SolutionThe unit-area capacitance isFig. 5 Situation at the onset of strong inversion. 2004 Sergio Franco Ch. 3 - MOSFETs Page 10 of156345 101382.5 10oxC= = nF/cm2At the onset of strong inversion, the depletion-layer width is120 19 162 1.04 102(0.35) 3011.602 10 10px = = nmThe corresponding electric field intensity is19 16 60 121.602 10 10 30.1 1046.41.04 10mE = = kV/cmThe unit-area charge in the bulk depletion-layer is19 16 1204 1.602 10 10 1.04 10 (0.35) 48.3bQ = = nC/cm2Finally, the required gate-body voltage drop is, by Eq. (6),048.30.94 2( 0.35)138GBV= = 0.94 + 0.70 + 0.35 = +0.11 VOnce strong inversion is reached, the surface potential (0) and, hence, the depletion-layer widthxp, will change very little with the applied voltage VGB because (0) depends on VGB only logarithmically.Any increase VGB above VGB0 will essentially be accompanied by an increase Qn CoxVGB in theelectron charge of the inversion layer.These electrons are supplied by the n+ source region (hence thereason for its name), where they exist in abundant supply.In fact, in order for these electrons to beenticed into the inversion layer, the gate must slightly overlap the source region to allow for the fringeelectric field to attract electrons from the source to the channel.As mentioned, the advantage of thesilicon-gate process is that it is a self-aligning process.Example 3Assuming the data of Example 2, find the change Qn brought about by a 1-V increase VGB in stronginversion.Compare with the depletion-layer charge Qb0.SolutionWe have Qn CoxVGB = (138 nF/cm2)(1 V) = 138 nC/cm2, indicating that the inversion-layer charge (Qn( can be significantly greater than the depletion-layer charge (Qb0( (= 48.3 nC/cm2in our example), even though the inversion layer is much thinner than the depletion layer.The Threshold Voltage Vt0We now wish to apply the above findings to the full-fledged MOSFET, starting from the situation at theonset of strong inversion depicted in Fig. 6 for both MOSFET types.Note the presence of the inversionlayer immediately below the oxide-bulk surface, along with the depletion layer extending not only belowthe inversion layer, but also around the source and drain regions, as they form pn junctions with the body.The threshold voltage Vt is defined as the gate-source voltage vGS needed to bring about the onset ofstrong inversion in the channel region.For the case of an nMOSFET with body and source at the samepotential (ground, in Fig. 6), the threshold voltage takes on the general form 2004 Sergio Franco Ch. 3 - MOSFETs Page 11 of00 02b ox it pox ox oxQ Q QVC C C = (7)The first three terms are simply those of Eq. (6).The next term, involving the unit-area charge Qox,accounts for the presence of dangling bonds in the bulk right at the interface, as well as positive ions thatget trapped in the oxide right near the oxide-bulk interface during fabrication.The first four terms formwhat is known as the native threshold of the nMOSFET.The last term, involving the unit-area charge Qi,accounts for impurities that the manufacturer introduces deliberately in the bulk, right at the oxide-bulkinterface, to adjust Vt0 to the desired value.For p-type impurities, we have Qi < 0, and for n-type impur-ities, we have Qi > 0.For obvious reasons, the native threshold is also called the undoped threshold.Example 4Assuming the data of Example 2, along with a surface state density Nox = 21011 positive ions/cm2,(a) Find the native threshold of the nMOSFET.(b) Find the implant type and dosage Ni needed for Vt0 = +1.0 V.(c) Find the implant type and dosage Ni needed for Vt0 = 1.0 V.Solution(a) We have Qox = qNox = 1.60210-1921011 = 32 nC/cm2.So, using the result of Example 2,0320.11138tV= = 0.122 V(b) To raise Vt0 = from its native value of 0.122 V to +1.0 V, we need a p-type implant, such asboron, which will contribute negative ions in the bulk near the surface.Imposing1991.602 101.0 0.122 0.122 0.122138 10i i iox oxQ qN NC C + = = = +gives Ni = 9.661011 p-type ions/cm2.(c) To lower Vt0 from its native value of 0.122 V to 1.0 V, we need an n-type implant, such asphosphorus, which will contribute positive ions in the bulk near the surface.Imposing(a) (b)Fig. 6 -The onset of strong inversion in (a) the nMOSFET and (b) the pMOSFET. 2004 Sergio Franco Ch. 3 - MOSFETs Page 12 of1991.602 101.0 0.122 0.122 0.122138 10i i iox oxQ qN NC C = = = gives Ni = 7.561011 n-type ions/cm2.We now make some important observations about nMOSFETs and pMOSFETs:An nMOSFET with Vt0 > 0 is said to be normally offbecause with vGS = 0 there is no channel.Weneed to raise VGS above Vt0 in order to create a channel or, equivalently, to enhance the channel-regionconductivity.This type of device is also referred to as enhancement nMOSFET.The higher the (p-type) implant dosage, the more positive the value of Vt0.The circuit symbol for this device, showninFig. 7a, uses a broken line to signify a normally nonconductive channel.An nMOSFET with Vt0 < 0 is said to be normally on because with vGS = 0 there is already a channelpresent.We need to lower vGS below Vt0 in order to eliminate the channel or, equivalently, to depletethe channel region of electrons.This type of device is also referred to as depletion nMOSFET.Thehigher the (n-type) implant dosage, the more negative the value of Vt0. The circuit symbol for thisdevice, shownin Fig. 7b, uses a continuousline to signify a normally conductive channel.A pMOSFET with Vt0 < 0 is said to be normally off because with vGS = 0 there is no channel.Weneed to lower vGS below Vt0 in order to create a channel.The circuit symbol of this device, also calledenhancement pMOSFET, is shown in Fig. 7c.A pMOSFET with Vt0 > 0 is said to be normally on because with vGS = 0 there is already a channel,and if we want to deplete it of holes, we need to raise vGS above Vt0.The circuit symbol of thisdevice, also called depletion pMOSFET, is shown in Fig 7d.The preferred mode of operation of a MOSFET is with the body tied to the source, resulting in athree-terminal device.This is the case, for instance, of discrete devices.Figure 8 shows the simplifiedMOSFET symbols most commonly used for this type of connection.To avoid the awkward broken lines,the enhancement-types are given solid lines.To signify that the channels of the depletion types arealready present, thicker lines are used.The Body Effect and the Threshold Voltage VtWhen multiple devices share the same substrate, the common body of nMOSFETs must be tied to themost negative voltage (MNV) to avoid inadvertently turning on any of the body-source or body-drain pn(a)(b)(c) (d)Fig. 7 Full-fledged circuit symbols for the four MOSFET types. 2004 Sergio Franco Ch. 3 - MOSFETs Page 13 ofjunctions.Likewise, the common body of pMOSFETs must be tied to the most positive voltage (MPV).It is therefore possible for the source of an nMOSFET to find itself at a higher voltage than the body, orVS > VB.Likewise, we can have VS < VB for a pMOSFET.We wish to investigate the effect of body-biason the threshold voltage of an nMOSFET.Denoting the source-body voltage of an nMOSFET as VSB (VSB 0), we can simply recycle ourprevious findings by replacing [2(p)] with [2(p) + VSB] in Eq. (5).The result is2 ( 2 )b A si SB pQ qN V = +where we are using the absolute value of p (p, < 0) to reduce the possibility of confusion.Clearly, theincrease in the depletion-region charge Qb comes at the expense of a simultaneous decrease in theinversion-layer charge Qn.To return the channel to its former state, vGS will have to be suitably increased.To find out by how much, we rewrite Eq. (7) as0 0 00 0 02 2b ox i b ox i b b b bt p p tox ox ox ox ox ox ox oxQ Q Q Q Q Q Q Q Q QV VC C C C C C C C = = = We can concisely express the threshold voltage in the insightful form02 2t t SB p pV V V (= + + ( (8)where Vt0 is the zero-body-bias value of Vt as given in Eq. (7), and2A sioxqNC = (9)Fig. 8 Simplified circuit symbols for the four MOSFET types. 2004 Sergio Franco Ch. 3 - MOSFETs Page 14 ofis called the body-effect parameter.Its value, in V1/2, is typically on the order of a fraction of 1 V1/2.Example 5(a) For the enhancement nMOSFET of Example 4(b), find Vt at VSB = 1 V, and at VSB = 5 V.(b) For the depletion nMOSFET of Example 4(c), find Vt at VSB = 1 V, and at VSB = 5 V.Solution19 16 1292 1.602 10 10 1.04 100.418138 10 = = V1/2(a) For the enhancement nMOSFET we haveVt(VSB = 1 V) = ( )1.0 0.418 1 0.7 0.7 1.0 0.195 1.195 + + = + =V.Vt(VSB = 5 V) = ( )1.0 0.418 5 0.7 0.7 1.0 0.648 1.648 + + = + =V.(b) For the depletion nMOSFET we haveVt(VSB = 1 V) = ( )1.0 0.418 1 0.7 0.7 1.0 0.195 0.805 + + = + = V.Vt(VSB = 5 V) = ( )1.0 0.418 5 0.7 0.7 1.0 0.648 0.352 + + = + = V.The example indicates that the effect of body bias is to shift the threshold voltage of annMOSFET in the positive direction, regardless of whether it is a depletion or enhancement type.For apMOSFET, the shift is in the negative direction.The dependence of Vt upon the body bias is referred toas the body effect, and the body itself is sometimes referred to as back gate because it influences theinversion layer like the gate, if in the opposite direction.Exercise 1Show that for a polysilicon-gate technology, the first two terms in the threshold voltage of an nMOSFETcan be expressed concisely as (0 2p) = VT ln (NA/ND). 2004 Sergio Franco Ch. 3 - MOSFETs Page 15 of3.The Channels CharacteristicsWe are now ready to investigate the i-v characteristics of the n-channel, anticipating that our understand-ing of the p-channel will follow easily once we have mastered the n-channel.Figure 9 shows thesequence of situations an n-channel goes through as we gradually increase vDS starting out with vDS 0.Once the MOSFET is biased in strong inversion, its channel can be viewed as a resistor of length L, widthW, and thickness proportional to the overdrive voltage, which is defined as the amount by which the gate-source voltage exceeds the threshold voltage,VOV = VGS Vt(10)For instance, in the device of Example 3, every volt of overdrive induces an electron charge of 138nC/cm2 in the channel, so the greater the overdrive, the more conductive the channel will be.If we nowapply a voltage vDS > 0 to the drain, electrons will drift from the source, through the channel, to the drain,like in an ordinary resistor (hence the designation ohmic for this region of operation), thus producingcurrent.But, electrons are negative, so the current iD at the drain terminal will flow into the device, asshown.The source and drain designations reflect the fact that mobile charges (electrons in nMOSFETS,holes in pMOSFETs) are sourced to the channel at one end, and drained from the channel at the other.The Triode RegionIf we now increase vDS further, an interesting effect occurs, namely, the channel becomes tapered, asdepicted in Fig. 9b.This stems from the fact that while the overdrive voltage is VGS Vt at the sourceend, it reduces to (VGS vDS) Vt at the drain end, indicating a thinner channel there.For instance, let Vt= 1 V, VGS = 5 V, and vDS = 2 V.Then, the overdrive at the source end is 5 1 = 4V, but that at the drainend is only (5 2) 1 = 2 V.In this example, the channel at the drain end is only half as thick as at thesource end.With a reduction in channel thickness, we expect an increase in the channels dynamicresistance.To investigate quantitatively, refer to Fig. 10, where we imagine that we have sliced the channellike a loaf of bread, and we focus on the slice of width dy located at a distance y from the source.Thevoltage at each slice varies from 0 V at the leftmost slice to vDS at the rightmost slice, so the voltage v(y)at our particular slice will lie somewhere in between, or 0 v(y) vDS.Now, the gate strip immediatelyabove our slice forms a capacitance dC = CoxWdy with the channel itself, so the charge packet dQninduced in the channel is, by the capacitance law,dQn = dC[VGS v(y) Vt] = CoxWdy[VGS v(y) Vt](This charge is negative because it consists of electrons.)The voltage drop vDS across the channelproduces an electric field E inside the channel, oriented from drain to source.This field, in turn, causesthe negative charge packet dQn to drift toward the drain, thus producing the current iD.By definition,[ ( ) ]nD ox GS tdQ dyi CW V vy Vdt dt= = where dy/dt represents the velocity with which dQn drifts toward the drain.This velocity is proportionalto the electric field, or dy/dt = nE(y), where n is the electron mobility.(The negative sign stems fromthe fact that electrons drift against the electric field.)But, electric field and potential are related as E(y) =dv(y)dy, so dy/dt = ndv(y)/dy.Substituting in the above equations gives 2004 Sergio Franco Ch. 3 - MOSFETs Page 16 ofFig. 9 Illustrating the different regions of operation of an nMOSFET.(a) Ohmic region(b) Triode region(c) Pinchoff (EOS)(d) Saturation region 2004 Sergio Franco Ch. 3 - MOSFETs Page 17 of( )[ ( ) ]D n ox GS tdvyi CW V vy Vdy = Multiplying both sides by dy and integrating from y = 0, where v(y) = 0, to y = L, where v(y) = vDS, we get 0 0[ ( ) ] ( )DSL vD n ox GS ti dy CW V vy Vdvy = The left side integrates to iDL, and the right side integrates to 212( )GS t DS DSv V v v .This allows us toexpress iD in the following insightful form21( )2D GS t DS DSi k V V v v (= ( (11)where the quantity'Wk kL= (12)is called the device transconductance parameter.This is simply a scale factor, in A/V2, indicating howmuch current a device will draw for a given set of VGS, Vt, ans vDS values.The designer can tailor thevalue of k to meet given needs by suitably specifying the devices dimensions W and L; hence, the reasonfor using the qualifier device.The quantity'n oxn oxoxk Ct = = (13)is called the process transconductance parameter, in A/V2.Being common to all devices, it is unique ofthe particular fabrication process; hence, the reason for using the qualifier process.Figure 11 shows thethe plot of iD versus vDS for a given overdrive voltage VOV.Fig. 10 Detailed illustration of the triode-region operation. 2004 Sergio Franco Ch. 3 - MOSFETs Page 18 ofWe observe that near the origin, where vDS is small enough to render the quadratic term negligiblein Eq. (11), the iDvDS characteristic approaches, for a given gate-source drive VGS, a straight line, or( )D GS t DSi k V Vv (14a)For this reason, the region corresponding to small values of vDS is called the linear region.Rewriting Eq.(14a) in the form of Ohms law as1D DSDSi vr= (14b)confirms that the channel acts as a resistor, this being the reason why this region is also referred to as theohmic region.The channel resistance rDS is controlled by the overdrive VOV as1 1( )'DSGS tOVrWk V Vk VL= =(15)This resistance depends also on the W/L ratio, also called the aspect ratio, indicating that by proper choiceof this ratio, the IC designer can set this resistance to virtually any value for a given overdrive VOV.Example 6Assuming n = 600 cm2/Vs, Cox = 83 nF/cm2, and Vt = 1.0 V,(a) Specify the W/L ratio so that rDS = 1 k for VGS = 5 V.(b) Calculate rDS for VGS = 4 V, 3 V, 2 V, 1 V, 0 V.Solution(a) By Eq. (13), 9' 600 83 10 50 k= A/V2.Using Eq. (15) to impose3611050 10 ( / )(5 1) WL= we get W/L = 5.Consequently, k = (50 A/V2)5 = 250 A/V2.Fig. 11 The complete iDvDS characteristic for a given overdrive voltage VOV = VGS Vt > 0.Note thatVDS(EOS) = VOV 2004 Sergio Franco Ch. 3 - MOSFETs Page 19 of(b) By Eq. (15), for VGS = 4 V, we getrDS = 61250 10 (4 1) = 1.333 k.Likewise, for VGS = 3 V we find rDS = 2 k, and for VGS = 3 V, we find rDS = = 4 k.For VGS 1 V, theMOSFET is in cutoff, and rDS = .As we keep increasing vDS, the channel becomes progressively thinner at the drain end, and thequadratic term becomes more and more significant in Eq. (11).Consequently, the slope of the curvedecreases, indicating a corresponding increase in the dynamic resistance of the channel.This region ofoperation is called the triode region by analogy with vacuum tubes, which exhibit similar characteristics.We also observe in Fig. 8 that the depletion layer associated with the body-drain junction widens as wekeep increasing vDS.The Pinchoff PointOnce vDS achieves the special valueVDS(EOS) = VGS Vt = VOV(16)the channel thickness at the drain end reduces to zero, as depicted in Fig. 8c, and the corresponding pointon the iDvDS curve is referred to as the pinchoff point.The current at this point is readily found bysubstituting vDS = VGS Vt in Eq. (11).The result gives2(EOS)( )2D GS tkI V V = (17)This can also be expressed as 2 2(EOS) (EOS)( / 2) ( / 2)D OVI k V k V = = .As we shall see next, this point marks thebeginning, or edge, of the saturation region (EOS).The Saturation RegionIf we raise vDS above the critical value VDS(EOS), the voltage at the pinchoff point continues to remain atVDS(EOS), and the excess difference vDS VDS(EOS) is dropped across a narrow depletion layer of width Lbetween the pinchoff point and the edge of the drain.As depicted in Fig. 8d, the pinchoff point movesslightly away from the drain, in effect shortening the channel by a small amount L.This effect, aptlyreferred to as channel-length modulation, is investigated by replacing L with L L in Eq. (12),'Wk kL L= This can be rewritten as( ) ' ' 1 ' 1(1 / )DSW W L Wk k k k vL L L L L L | |= + + | \ .(18)where we have conformed to the established practice in the literature to assume that the fractional changeL/L (L/L Vt, the device is onand in saturation, because vDS = vGS implies vDS > VGS Vt, the condition for an nMOSFETs operation insaturation.Consequently, when on, the device is governed by Eq. (19), but with vDS = vGS.The result isthe curve of Fig. 13, which reveals a tendency by a diode-connected MOSFET to favor current flow inone direction (drain-to-source for an nMOSFET, source-to-drain for a pMOSFET) while inhibiting it inthe opposite direction.Hence the name for this mode of operation.At this juncture it must be pointed out that the MOSFETs transition from off to on at thethreshold Vt is not abrupt, but rather a gradual process.In fact, the channel already starts to conduct for arange of vGS values less than, if close to, Vt.Over this range, aptly called the subthreshold region, it turnsout that iD increases exponentially with vGS.The choice of Vt as the value of vGS responsible for the onsetof strong inversion is primarily a matter of mathematical convenience and mental bookkeeping.The slope of the curve at a particular point VGS is denoted as gm and is called the transconductanceGSVGSDmvig= (21)Its units are A/V, or more likely A/V in micropower devices.Differentiating Eq. (19) but with = 0 forsimplicity, and suitably manipulating, we find three different forms for calculating transconductance,2m Dg kI = (22a)( )m GS t OVg k V V kV = = (22b)20.5( )D DmGS t OVI IgV V V= =(22c)Though the three forms are equivalent, each provides different insight.The first form indicates that gmVt = 1.0 VW = 2 mL = 1 mk = 50 A/V2 = 0.05V-1Fig. 12 - Diode-connected enhancement nMOSFET. 2004 Sergio Franco Ch. 3 - MOSFETs Page 22 ofincreases with the square root of ID.By contrast, in a bipolar junction transistor (BJT), gm is linearlyproportional to the collector current IC, or gm = IC/VT, where VT = 26 mV is the thermal voltage.Also, thesecond form indicates that gm is proportional to the overdrive voltage VOV = VGS Vt.Example 7Assuming the nMOSFET data of Fig. 12, but with = 0 to simplify the calculations,(a) Find VGS for ID = 1 mA.Compare with Fig. 13, and comment.(b) Find gm at that point, and compare with the gm of a bipolar junction transistor (BJT) operatingat the same current level.(c) Find W/L to raise the gm of the FET to the same value as that of the BJT.SolutionBy Eq. (12), k = 5010-6(2/1) = 100 A/V2.(a) Using Eq. (19) with = 0, we get 110-3 = (10010-6)(VGS 1.0)2, or VGS = 5.472 V.This is higher than the value (5 V) predicted by Fig. 13 because we have assumed = 0.This gives anidea about the error incurred by ignoring .(b) By Eq. (22a), 6 32 2 100 10 10 0.447m Dg kI = = =mA/V.By contrast, at 1 mA a BJTgives gm 1/26 = 38.5 mA/V.(c) Since gm is linearly proportional tok , and thus to/ WL , we impose a simple proportion,/ / 2/1 38.5/ 0.447 WL =which gives W/L 14,800, an outlandish number.This example illustrates a notorious feature ofMOSFETs compared to BJTs, namely, their generally much lower gm values.Indeed, if we use Eq. (22c),we get gm = ID/[(5.472 1)/2] = ID/(2,236 mV), which compares quite unfavorably with the BJT relationgm = IC/(26 mV).The Complete i-v CharacteristicsIn Fig. 10 we have illustrated the behavior of the channel as we walk it through the different situations ofFig. 8, but for only a single fixed value of VGS (VGS > Vt).To get the complete picture, we need to displaythe characteristics for different values of VGS.The PSpice circuit of Fig. 14 displays the iD-vDS character-istics with vGS stepped in 0.5-V increments.The result is the family of curves of Fig. 15, with respect toFig. 13- i-v Characteristic of a diode-connected enhancement nMOSFET. 2004 Sergio Franco Ch. 3 - MOSFETs Page 23 ofwhich we make the following observations:For VGS < Vt (VGS < 1.0 V in our example), the device gives iD = 0 and is thus in cutoff (CO).Itsterminals draw only leakage currents, which are negligible in most practical situations.For VGS > Vt, the device is on, either in the triode region if vDS < (VGS Vt), or in the saturation regionif vDS > (VGS Vt).Either region requires a separate equation for finding iD, namely,vDS < (VGS Vt) Triode region21( )2D GS t DS DSi k V V v v (= ( vDS > (VGS Vt) Satur.n region2( ) (1 )2D GS t DSki V V v = +The locus of points for which vDS = VGS Vt = VOV provides the borderline between the two regionsSince the abscissas are spaced evenly while the ordinates are spaced quadratically, this locus is aparabola.In fact, one can readily see that this locus is simply the i-v curve of Fig. 13, but shiftedFig. 15 Complete i-v characteristics of an enhancement nMOSFET, and its regions of operation.Fig. 14 PSpice circuit to display the complete i-v characteristics of an nMOSFET.Vt = 1.0 VW = 2 mL = 1 mk = 50 A/V2 = 0.05V-1 2004 Sergio Franco Ch. 3 - MOSFETs Page 24 ofto the left by Vt.The saturation-region curves, when extrapolated towards the left, converge to a common point locatedat 1/ on the vDS axis.This is shown in the compressed rendition of Fig. 16.Also called the Earlyvoltage VA by analogy with a similar behavior on the part of BJTs, where this term is used, thisvoltage is simply VA = 1/.Typically, VA is on the order of 10 to 100 V.In our example, VA = 1/0.05= 20 V, so the intercept is located at vDS = VA = 20 V.As a rule, the shorter the channel, the lowerthe value of VA.This is expressed by saying that VA scales with L.The Depletion nMOSFETThe i-v characteristics of the depletion-type nMOSFET are similar to those of its enhancement-typecounterpart, except that the depletion device is already on for vGS = 0 V.This is depicted in Fig. 17,whose curves were obtained with the PSpice circuits of Figs. 12 and 14, but with Vt changed to 1.0 V.The curve of Fig. 17a is similar to that of Fig. 13, except that it is shifted to the left because Vt is nownegative.We can either turn the device further on by raising vGS above 0 V, or turn it gradually off bylowering vGS below 0 V, until it shuts off completely once vGS reaches Vt (1.0 V in our example).Theeffect of sweeping vGS can be appreciated also from Fig. 17b, where we note that the curve correspond-Fig. 17 The i-v curves of the depletion nMOSFET.Fig. 16 Effect of channel-length modulation on the i-v chacteristics. 2004 Sergio Franco Ch. 3 - MOSFETs Page 25 ofing to vGS = 0 V is somewhere in the middle.The locus of the pinchoff points is still vDS = VGS Vt(= VGS + 1.0 V in our example.)A particularly interesting application arises when the gate and source of a depletion-typenMOSFET are tied together as in Fig. 18a, thus resulting in a two-terminal device with VGS = 0.Thecorresponding curve in Fig. 18b indicates current-source behavior, at least as long as the device isoperated in saturation.Such a device can be used to bias other devices.Example 8Assuming the data of Fig. 12 but with Vt = 1.0 V for the MOSFET of Fig. 18a, find:(a) The range of voltages over which it exhibits current-source behavior(b) The current at the edge of saturation.(c) The output resistance ro.(d) The value of W/L needed to raise the current at the edge of saturation to 0.5 mA.Solution(a) The saturation region occurs for v > V(EOS) = VOV = 0 Vt = 0 (1.0) = 1.0 V.(b) I(EOS) = (k/2)(0 Vt)2(1 + V(EOS)) = (100/2)(1)(1 + 0.051) = 52.5 A.(c) ro = 1/I = 1/(0.0552.510-6) = 381 k.(d) W/L = (2/1)(500/52.5) 19.The pMOSFET and Comparison with the nMOSFET.The voltage-current relationships developed for the nMOSFET can be extended to the pMOSFET,provided we reverse all current directions and all voltage polarities.The two devices are compared inFig. 19, where voltage is likened to height, so higher voltages are at the top and lower voltages at thebottom.Following is a summary of similarities and differences between the two devices.(Whennecessary, subscript n and p are used to distinguish between the devices.)The current iD flows into the drain of the nMOSFET, but out of the drain of a pMOSFET.In a p-channel, iD consists of holes flowing from higher potential (source) to lower potential (drain).In an n-channel, iD consists of electrons flowing from lower potential (source) to higher potential(drain).In both devices, the source and drain regions are interchangeable.The source will always be the(a) (b)Fig. 18 The depletion nMOSFET as a current source. 2004 Sergio Franco Ch. 3 - MOSFETs Page 26 ofregion at lower potential in an nMOSFET, and that at higher potential in a pMOSFET.To turn on an n channel, the gate voltage vG must be raised above the source voltage vS by at least Vtn,or vGS > Vtn.The overdrive voltage is VOV = VGS Vtn.To turn on a p channel, the gate voltage vG must be lowered below the source voltage vS by at leastVtp.In the case of enhancement-types, which are more popular than depletion types, the turn-oncondition is less confusingly expressed as vSG > (Vtp.The overdrive voltage is VOV = VSG (Vtp.If vDS is large enough to satisfy vDS > VOV, then the n channel is operating in saturation,2( ) (1 )2nD GS tn n DSki V V v = +for vDS > VOV(23a)If vSD is large enough to satisfy vSD > VOV, then the p channel is operating in saturation,2( ) (1 )2pD SG tp p SDki V V v = +for vSD > VOV(23b)If vDS is small enough to satisfy vDS < VOV, then the n channel is operating in the triode region,21( )2D n GS tn DS DSi k V V v v (= ( for vDS < VOV(24a)If vSD is small enough to satisfy vSD < VOV, then the p channel is operating in the triode region,21( )2D p SG tp SD SDi k V V v v (= ( for vSD < VOV(24b)The device transconducance parameters for the nMOSFET and the pMOSFET are, respectively,nn nnWk kL = (25a)Fig. 19 Comparing voltage polarities, current directions, voltage levels, and voltage ranges for theenhancement nMOSFETS and pMOSFETs. 2004 Sergio Franco Ch. 3 - MOSFETs Page 27 ofpp ppWk kL = (25b)The process transconducance parameters for the nMOSFET and the pMOSFET are, respectively,n oxnoxkt = (26a)p oxpoxkt = (26b)To avoid the inadvertent turn-on of the internal pn junctions, the bodies must be biased so that VSB > 0for the nMOSFET, and VBS > 0 for the pMOSFET.Body bias in the nMOSFET shifts Vtn in the positive direction as02 2tn tn n SB p pV V V (= + + ( (27a)Body bias in the pMOSFET shifts Vtp in the negative direction as02 2tp tp p BS n nV V V (= + (27b)In general, the parameters Vtn0, Vtp0, n, p, n, and p are found experimentally via suitable measurements.As we know, the transconductance parameters of Eqs. (26) are proportional to the mobilities (nor p) of the charges intervening in the main current in the device.This is not surprising, as MOSFETcurrent is of the drift type.When studying BJTs, in the previous chapter, we have encountered a similarparameter, namely, the saturation current Is, which instead is proportional to the diffusivity (Dn or Dp) ofthe charges responsible for the main current in the device.This is so because BJT current is of thediffusion type.For a given doping density, electron mobility and diffusivity are two to three times higherthan hole mobility and diffusivity, respectively.For these reasons, n-channel FETS are preferred over p-channel types, and npn BJTs are preferred over pnp types.Large-Signal Circuit Models in the Saturation RegionFigures 20 and 21 show the circuit models of the nMOSFET and the pMOSFET operating in saturation.Also called large-signal models (to distinguish them from the small-signal models to be introduced later,)they are used primarily in dc calculations.Since the gate is the plate of a capacitor, the G-S (or input)port appears as an open circuit, at least at dc.Consequently, at dc we have iG = 0, indicating that iS = iD.Fig. 20 Large-signal model for the saturated nMOSFET. 2004 Sergio Franco Ch. 3 - MOSFETs Page 28 ofThe D-S (or output) port is modeled with its Norton equivalent consisting of a dependent current sourcecalculated at the edge of saturation, and an output resistance to model the slight increase of iD with vDS (orvSD).To simplify our hand calculations in the course of dc analysis, we shall often ignore the outputresistance, which is equivalent to assuming = 0.Also, for the enhancement pMOSFET, we shallexpress the dependent-source value in the form (kp/2)(VSG |Vtp|)2, more closely resembling that of thenMOSFET.Fig. 21 Large-signal model for the saturated pMOSFET.