MOS Only Negative Resistances

description

Transcript of MOS Only Negative Resistances

-

AbstractIn this paper, a number of tunable grounded

negative resistor circuits are presented. These new negative resistors exhibit important features such as simplicity, independent tunability and wide frequency range. One of the introduced negative resistor circuits is simulated using TSMC 0.18m process parameters and compared to a couple of other negative resistors in the literature.

KeywordsMOS, resistance simulation, negative resistor, tunable resistor, active resistor.

I. INTRODUCTION ECENTLY, there has been a growing interest in the realization of active resistors, both positive and negative, appropriate for on-chip fabrication. Not only positive-

valued tunable resistors but also negative-valued resistors are increasingly being needed as a key element for the implementation of filters, oscillators, amplifiers, mixers, artificial neural networks and control systems [1-3].

Negative resistor implementations started with the discovery of tunnel diode and continued with more and more improved circuits in the literature [4-8]. Negative resistors were mostly preferred as negative resistance loads (NRL) within these filter implementations for the compensation of parasitic resistances. In the following years, a number of floating and grounded resistance circuits have been introduced and utilized in RF bandpass filter applications [9-13]. In the last few years new techniques have been proposed for the implementation of traditional cross-coupled transistor pairs forming negative resistance [14-17]. In most of the reported topologies in the literature coupling of negative resistance to the main circuit appears as a problem, especially for floating negative resistors. As the negative loads are designed within the circuits, their bias currents and other parameters inevitably affect the main circuit parameters and additional adjustment may be needed. A number of examples concerning this issue can bee seen in [8,9,13,14]. As a classical approach for implementing a negative resistor, cross-coupled transistor pairs are arranged in grounded topology in [14] and main drawback here is the reusage of the current between negative resistance load and active inductor, which affects the circuit parameters. Isolation between the negative resistance load and the main circuit is important with the fact that parasitic input capacitance and biasing issues directly change the behavior of the main circuit. This need is fulfilled in [15] by applying ac coupling for the separation of

Manuscript received May 5, 2011 A. Sunca is MS student at the Dept. of Electrical & Electronics Engg

Bogazici University Istanbul/TURKEY (e-mail: [email protected] ) O. Cicekoglu and G.Dundar are with the Dept. of Electrical &

Electronics Engg Bogazici University Istanbul/TURKEY (e-mail: [email protected], [email protected] )

the negative resistance load, which is a slight modification of the negative resistor topology used in [14].

In this paper, we present a number of grounded negative resistor circuits, all having different equations of resistance and these circuits are to be ac coupled to the main circuit. Different from the topology in [15], proposed negative resistors are easier to bias and tune. In addition they have less number of transistors including bias circuitry. Minimum dimensions can be used for the transistors to keep the power consumption and input parasitic capacitance low. One of the proposed negative resistor circuits is examined and compared to that of a grounded negative resistor in [8] and floating negative resistor in [7] by using the simulation results obtained in [18]. In addition, a general comparison is made regarding the usage of the proposed negative resistors among other proposed negative resistor circuits in the literature.

II. CIRCUIT PRINCIPLE Negative resistors are well-investigated in the aspects of

large and small signal characteristics including noise, stability and bandwidth by [18]. Although negative resistors are potentially unstable, their usage for compensation of parasitic resistances makes them stable in higher level circuits.

Twelve negative resistance simulators are shown in Table III. Each pair of them realizes the same input resistance as shown in the table. Note that they are topologically related in pairs.

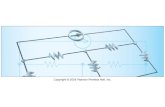

The gate-source capacitance of the MOS transistors may introduce additional poles and zeros to the input impedance function that may deteriorate the functionality of the circuit. To illustrate this we examined the negative resistance simulator (b) in Table III considering the gate-source capacitances and drain-source conductances as a source of the non-ideality effect. The circuit is repeated in Fig.1 for convenience. Its non-ideal input impedance is given as:

( )( ) ( )

1 2 3 1 2 3 1 2 32

1 2 3 1 2 1 3 1 3 2 2 2 3 2 1 3 1 1 2 3 1

m m m o o oIN

m m m o o o o o m o o o o

g g g g g g s C C CZ

g g g g g g g g s g C g C g C g C g C sC C C+ + + + + + + +

=

+ + + + + + + + + + (1)

where gmi is the transconductance, Ci is the parasitic gate-source capacitance of Mi and goi is the drain-source conductance of Mi. Neglecting drain-source conductances, resistance at low frequencies is given as:

2m1m

3m2m1meq gg

gggR ++= (2)

Note that the input impedance equation has a second order denominator and it has a zero at:

321

3o2o1o3m2m1mz CCC

gggggg++

+++++= (3)

which implies one condition for desired operation as < z.

MOS Only Simulated Grounded Negative Resistors Abdullah Sunca, Oguzhan Cicekoglu, and Gunhan Dundar

R

978-1-4577-1411-5/11/$26.00 2011 IEEE TSP 2011328

-

Fig.1. Proposed negative resistor

Complete schematic of the negative resistor circuit is shown in Fig.2. Resistance can be tuned changing gm1 after adjusting gm2 and gm3.

M2

M1Vb

M3 Vc

ZIN

M4Va

M5Vd

VDD VDD VDD

Fig.2. Complete negative resistor circuit

III. SIMULATION RESULTS

Negative resistor behavior is investigated through frequency range and phase response. Magnitude and phase of the input impedance of the proposed negative resistor circuit is shown Fig.3.

In contrast to that of a grounded negative resistor in [8], frequency range in which the pure resistor behavior is observed (-180 degrees phase shift) shows a better transition. Table I shows a comparison about frequency and phase relations between these two negative resistors. Other large and small signal parameters for [8] and [7] are compared in Table II. It is seen that proposed negative resistor circuit serves a more appropriate solution concerning frequency response and loading effects. For tuning possibilities, negative resistor in [8] is the best although its operation is limited up to 4 MHz.

(a)

(b) Fig.3. (a) Magnitude of input impedance of the negative resistor, (b) phase of input impedance of the negative resistor

TABLE I

COMPARISON OF FREQUENCY AND PHASE RELATIONS

Design (for -10K)

Phase angle (degrees) at specified frequency 100 kHz 500 kHz 16 MHz 300 MHz 1GHz

[8] -180 -180 -155 -70 -60 This work -180 -180 -180 -172 -150

TABLE II

COMPARISON OF LARGE & SMALL SIGNAL PARAMETERS

Performance [8] [7] This work Technology 0.5 1.2 0.18 Power Supply 1.5 V 3 V 1.5 V Tuning Range -8K to -250K -8K to -11K -2K to -11K Power Consumption

0.37mW (R=-20K)

0.96mW (R=-10K)

0.42mW (R=-10K)

Constant Resistance Range 0~4 MHz 0~300 MHz 0~900 MHz

VDD VDDVDD

J1

J2

Mag

nitu

de(a

bs)

Frequency (Hz)

Phas

e (d

egre

es)

Frequency (Hz)

Vb=0.9V

Vb=1.2V

Vb=0.95V

Vb=1.3V

Vb=1.5V

Vb=0.9V

Vb=0.95V

Vb=1.2V

Vb=1.5V

Vb=1.3V

329

-

TABLE III

PROPOSED CIRCUITS

CIRCUITS Type1 Type2 EQUIVALENT RESISTANCE

(a) M2

M1

M3

M2

M1

M3

2m1m

3meq gg

gR =

(b)

M2

M1

M3

M2

M1

M3

2m1m

3m2m1meq gg

gggR

++=

(c) M2

M3

M1

M3

M2

M1

3m2m

1meq gg

gR =

(d) M2

M3

M1

M3

M2

M1

3m2m1m2m3m1m

3meq gggggg

gR

+=

VDD VDD VDD

Va

Va

Va

Vb

Va

Vb

Va

Va

Va

Va

VDD VDD VDD VDD VDD

VDD VDD VDD

VDD VDD VDD VDD

ZIN

ZIN ZIN

ZIN

ZIN

ZIN

ZIN

ZIN

330

-

CIRCUITS Type1 Type2 EQUIVALENT RESISTANCE

(e) M2

M1

M3

M4

M2

M1

M3

M4

4m3m2m1m

3meq gggg

gR

+=

(f)

M2

M1

M3

M2

M3

M1

3m1m3m2m2m1m

2m1meq gggggg

ggR

++

+=

IV. CONCLUSIONS In this work a number of MOS negative resistor circuits

are introduced. Large and small signal characteristics and frequency response comparisons show that these new resistors can be utilized in many applications requiring resistance compensation. These resistor circuits are competitive among other implementations in the literature due to the advantages in tunability, frequency range, simplicity, capacitive loading and biasing. In addition, these circuits can be accepted as multi-purpose negative resistor blocks and they are potential candidates to be utilized in many implementations in communication systems.

REFERENCES [1] S. Lee, W. Lee, and K. Chung, A highly linear voltage controlled

resistor for neural chip, IEEE international conference on systems, man, and cybernetics, pp. 18516, 1998.

[2] S. Tantry, T. Yoneyama, and H. Asai, Two floating resistor circuits and their applications to synaptic weights in analog neural networks, IEEE international symposium on circuits and systems, pp. 5647, 2001.

[3] H. Song and J. Harris, A CMOS neural oscillator using negative resistance, Proceedings of IEEE international symposium on circuits and systems, pp.1525, 2003.

[4] W.Surakamponton, CMOS Floating Voltage-Controlled Negative Resistor, Electronics Letters, vol.28, pp.1457-1459, 1992.

[5] F. Yang, P. Loumeau, P. Senn, Novel Output Stage for DC Gain Enhancement of OPAMP and OTA, Electronics Letters,Vol. 29, No. 11, May 1993.

[6] R. Raut, A CMOS Building Block for Analogue VLSI Systems, Int. J. Electronics, Vol. 80, No. 1, pages 77-98, 1996.

[7] R. Raut, Wideband CMOS Transconductor for Analog VLSI Systems, IEEE Trans. on Circuits and Systems 2: Analog and Digital Signal Processing, Vol. 43, No. 11, Nov 1996.

[8] S. Szczepanski, J. Jakusz, R. Schaumann, A Linear Fully Balanced

CMOS OTA for VHF Filtering Applications, IEEETans. On Circuits and Systems: Analog and Digital SignalProcessing, Vol. 44, No. 3, Mar 1997.

[9] Y. Wu, M. Ismail, H. Olsson, A novel CMOS fully differential inductorless RF bandpass filter, Proc. IEEE ISCAS, vol. 4, pp. 149-152, 2000.

[10] N. Tadic, A Floating, Negative-Resistance Voltage-Controlled Resistor, IEEE Instrumentation and Measurement Technology Conference, Budapest, Hungary, May 2001.

[11] T. Oura, T. Yoneyama, S. Tantry, H. Asai, A CMOS Floating Resistor Circuit Having Both Positive and Negative Resistance Values, IEICE Trans. Fundamentals, Vol. E85-A, No. 2, Feb 2002.

[12] T. Oura, T. Toneyama, S. Tantry, and H. Asai, A threshold voltage independent floating resistor circuit exhibiting both positive and negative resistance values, IEEE international symposium on circuits and systems, pp. 73942, 2002.

[13] Y. Wu, X. Ding, M. Ismail, H. Olsson, RF bandpass filter design based CMOS active inductors, IEEE Transactions on Circuits and Systems II, vol.50, NO.12, pp. 942-949, 2003.

[14] V.Stornelli, G.Ferri, G.Leuzzi, A.De Marcellis, A tunable 0.5-1.3 GHz CMOS 2nd Order Bandpass Filter with 50ohm Input-Output Impedance Matching IEEE International Symposium on Circuits and Systems, ISCAS 2006 Proceedings, May 2006.

[15] C. Andriesei and L. Goras, On the Tuning Possibilities of an RF Bandpass Filter with Simulated Inductor, International Semiconductor Conference, CAS 2007, vol. 2, pp. 489492, Romania, 2007.

[16] C. Andriesei, L. Goras, F. Temcamani, Negative resistance based tuning of an RF bandpass filter, 4th European Conference on Circuits and Systems for Communications, ECCSC 2008, pp.83-86, 10-11 July 2008.

[17] W.Petchmaneelumka, P.Julsereewong, V.Riewruja, Positive/Negative Floating Resistor Using OTAs, International Conference on Control, Automation and Systems 2008 Oct. 14-17, COEX, Seoul, Korea, 2008

[18] V. Patel, R. Raut, A study on CMOS negative resistance circuits Electrical and Computer Engineering, 2008. CCECE 2008. Canadian Conference, pp.001283-001288, 4-7 May 2008.

[19] F.Yuan, CMOS Active Inductors and Transformers, Principle, Inplementation and Applications, Springer, 2008.

Va

Vb Va

Vb

Va

Vb

Va

Vb

VDD VDD

VDD VDD

VDD

VDD

ZIN

ZIN

ZIN

ZIN

331

/ColorImageDict > /JPEG2000ColorACSImageDict > /JPEG2000ColorImageDict > /AntiAliasGrayImages false /CropGrayImages true /GrayImageMinResolution 200 /GrayImageMinResolutionPolicy /OK /DownsampleGrayImages true /GrayImageDownsampleType /Bicubic /GrayImageResolution 300 /GrayImageDepth -1 /GrayImageMinDownsampleDepth 2 /GrayImageDownsampleThreshold 2.00333 /EncodeGrayImages true /GrayImageFilter /DCTEncode /AutoFilterGrayImages true /GrayImageAutoFilterStrategy /JPEG /GrayACSImageDict > /GrayImageDict > /JPEG2000GrayACSImageDict > /JPEG2000GrayImageDict > /AntiAliasMonoImages false /CropMonoImages true /MonoImageMinResolution 400 /MonoImageMinResolutionPolicy /OK /DownsampleMonoImages true /MonoImageDownsampleType /Bicubic /MonoImageResolution 600 /MonoImageDepth -1 /MonoImageDownsampleThreshold 1.00167 /EncodeMonoImages true /MonoImageFilter /CCITTFaxEncode /MonoImageDict > /AllowPSXObjects false /CheckCompliance [ /None ] /PDFX1aCheck false /PDFX3Check false /PDFXCompliantPDFOnly false /PDFXNoTrimBoxError true /PDFXTrimBoxToMediaBoxOffset [ 0.00000 0.00000 0.00000 0.00000 ] /PDFXSetBleedBoxToMediaBox true /PDFXBleedBoxToTrimBoxOffset [ 0.00000 0.00000 0.00000 0.00000 ] /PDFXOutputIntentProfile (None) /PDFXOutputConditionIdentifier () /PDFXOutputCondition () /PDFXRegistryName () /PDFXTrapped /False

/CreateJDFFile false /Description > /Namespace [ (Adobe) (Common) (1.0) ] /OtherNamespaces [ > /FormElements false /GenerateStructure false /IncludeBookmarks false /IncludeHyperlinks false /IncludeInteractive false /IncludeLayers false /IncludeProfiles true /MultimediaHandling /UseObjectSettings /Namespace [ (Adobe) (CreativeSuite) (2.0) ] /PDFXOutputIntentProfileSelector /NA /PreserveEditing false /UntaggedCMYKHandling /UseDocumentProfile /UntaggedRGBHandling /UseDocumentProfile /UseDocumentBleed false >> ]>> setdistillerparams> setpagedevice

![Comparative Study of Negative Capacitance Field-Effect ... · electric capacitance C FE to underlying MOS capacitance C MOS in NCFET [19]. However, the effect of matching between](https://static.fdocuments.net/doc/165x107/5f2e8a45d14522559a0e5b52/comparative-study-of-negative-capacitance-field-effect-electric-capacitance.jpg)