Efremova_2014_Toxicity of Graphene Shells, Graphene Oxide, And Graphene

MOBILITY AND SATURATION VELOCITY IN GRAPHENE ON …

Transcript of MOBILITY AND SATURATION VELOCITY IN GRAPHENE ON …

MOBILITY AND SATURATION VELOCITY IN GRAPHENE ON SILICON DIOXIDE

BY

VINCENT E. DORGAN

THESIS

Submitted in partial fulfillment of the requirements

for the degree of Master of Science in Electrical and Computer Engineering

in the Graduate College of the

University of Illinois at Urbana-Champaign, 2010

Urbana, Illinois

Adviser:

Assistant Professor Eric Pop

ii

ABSTRACT

Transport properties of exfoliated graphene samples on SiO2 are examined from four-

probe electrical measurements combined with electrical and thermal modeling. Data are analyzed

with practical models including gated carriers, thermal generation, “puddle” charge, and Joule

heating. Graphene mobility is characterized as a function of carrier density at temperatures from

300 to 500 K. In addition, electron drift velocity is obtained at high electric fields up to 2 V/μm,

at both 80 K and 300 K. Mobility displays a peak vs. carrier density and decreases with rising

temperature above 300 K. The drift velocity approaches saturation at fields >1 V/μm, shows an

inverse dependence on carrier density (~n-1/2

), and decreases slightly with temperature. Satura-

tion velocity is >3×107 cm/s at low carrier density, and remains greater than in Si up to 1.2×10

13

cm-2

density. Transport appears primarily limited by the SiO2 substrate, but results suggest in-

trinsic graphene saturation velocity could be more than twice that observed here.

iii

To my grandparents for their constant support of my education

iv

ACKNOWLEDGMENTS

I would like to thank my adviser, Professor Eric Pop, for allowing me join his research

group, and more importantly, for his support and guidance during this research project. I am also

grateful for many fruitful discussions with my fellow research group members: Myung-Ho Bae,

David Estrada, Albert Liao, Austin Lyons, Zhun-Yong Ong, Balaji Ramasubramanian, Feng

Xiong, and Josh Wood. I would especially like to thank Myung-Ho Bae and David Estrada for

the training and assistance they have provided me. I acknowledge insightful discussions with

Professors Suman Datta, Michael Fuhrer, and Emanuel Tutuc. I would like to thank the Micro

and Nanotechnology Laboratory staff for their technical support. Lastly, I thank my family for

their loving support and for always helping me achieve my academic goals. This work was sup-

ported in part by the Nanoelectronics Research Initiative (NRI) through the Midwest Institute for

Nanoelectronics Discovery (MIND), the Office of Naval Research (ONR), and the National

Science Foundation (NSF).

v

TABLE OF CONTENTS

CHAPTER 1: INTRODUCTION ................................................................................................... 1

1.1 Power Dissipation and Performance Issues of Integrated-Circuit Technology .................... 1

1.2 Graphene ............................................................................................................................... 2

1.3 Figures and Table .................................................................................................................. 5

1.4 References ............................................................................................................................. 9

CHAPTER 2: FABRICATION AND MEASUREMENT ........................................................... 11

2.1 Device Fabrication .............................................................................................................. 11

2.2 Measurements and Characterization ................................................................................... 12

2.3 Figures ................................................................................................................................ 15

2.4 References ........................................................................................................................... 17

CHAPTER 3: GRAPHENE CHARGE DENSITY MODEL AND MOBILITY

EXTRACTION ............................................................................................................................. 18

3.1 Charge Density Model for GFETs ...................................................................................... 18

3.2 Low-Field Mobility in Graphene at High Temperatures .................................................... 21

3.3 Figures ................................................................................................................................ 23

3.4 References ........................................................................................................................... 26

CHAPTER 4: SATURATION VELOCITY IN GRAPHENE ON SILICON DIOXIDE ............ 27

4.1 High-Field Simulations and Measurements ........................................................................ 27

4.2 High-Field Drift Velocity in Graphene on SiO2 ................................................................. 28

4.3 Figures ................................................................................................................................ 31

4.4 References ........................................................................................................................... 34

CHAPTER 5: CONCLUSION AND FUTURE WORK .............................................................. 35

5.1 Summary ............................................................................................................................. 35

5.2 Future Work ........................................................................................................................ 35

5.3 Figure .................................................................................................................................. 37

5.4 References ........................................................................................................................... 38

APPENDIX A: PROCEDURE FOR FABRICATING GFETS ON SILICON DIOXIDE .......... 39

A.1 Substrate Preparation ......................................................................................................... 39

A.2 Mechanical Exfoliation of Graphite ................................................................................... 39

A.3 Identify Monolayer Graphene ............................................................................................ 39

A.4 Pattern E-beam Markers .................................................................................................... 39

A.5 Pattern and Deposit Metal Electrodes ................................................................................ 40

A.6 Pattern and Etch Graphene Channel .................................................................................. 40

1

CHAPTER 1: INTRODUCTION

1.1 Power Dissipation and Performance Issues of Integrated-Circuit Technology

Current integrated-circuit (IC) technology is driven by the silicon transistor, or more im-

portantly, the ability to increasingly scale down the transistor size in order to enhance the per-

formance of an individual transistor while also increasing the total number of transistors for a

given area. However, as feature sizes of silicon transistors approach the nanometer scale, transis-

tor performance no longer scales in proportion with device dimensions, particularly channel

length. The trends of power supply voltage, VDD, and threshold voltage, VT, for transistors with

shorter channel lengths exemplify this issue, such that VDD no longer scales proportionally with

channel length, L, and VT no longer scales proportionally with VDD [1]. This occurs due to a tra-

deoff between circuit speed versus leakage current when adjusting VDD and VT, where scaling

down the threshold voltage may improve switching speed but will also cause an exponential in-

crease in the “off” current.

The inability to scale down VDD proportionally with L causes a problem with respect to

power dissipation. The static power of a transistor circuit may be defined by its leakage current

and supply voltage where PSTATIC = ILEAK VDD. The dynamic or switching power of a transistor

circuit is given by PDYN = CVDD2f, where C is the circuit’s total equivalent capacitance charged

and discharged in a clock cycle and f is the clock frequency. Both the static and dynamic power

increase with increasing VDD, thus VDD not scaling with L has resulted in the power density of

processors to increase exponentially over time, as shown in Fig. 1.1. Therefore, future scaling is

limited by the rate at which heat can be removed from the circuit [2]. Furthermore, the increasing

use of IC technology has made reducing power dissipation in integrated electronics essential, as

the U.S. information technology infrastructure uses up to 10% of national electricity today, a fig-

2

ure that may triple by 2025 [3]. In addition, PCs in corporate offices are responsible for CO2

emissions equivalent to that of approximately 5 million cars. Based on simple estimates, even a

2x more energy-efficient transistor would lower nation-wide power use by over 10 GW. Thus,

developing low-power nanoscale devices will affect energy consumption by society as a whole,

and has great environmental implications as well.

1.2 Graphene

1.2.1 Basic Physics of Graphene

Graphene is a two-dimensional (2D) crystal of carbon atoms arranged in a hexagonal

structure. It is the fundamental building block of graphitic materials, and thus is important in de-

termining the electronic properties of other carbon allotropes such as graphite (3D stack of gra-

phene sheets), carbon nanotubes (1D rolled up graphene cylinder), and fullerenes (0D molecules

of wrapped-up graphene with the introduction of pentagons). These carbon structures along with

graphene are shown in Figs. 1.2a-d. Each carbon atom in the hexagonal structure of graphene is

bonded to its nearest neighbor by a strong covalent sp2 bond. The resulting carbon-carbon dis-

tance is given by aC-C = 1.42 Å [4]. Each atom also shares a π bond with its three nearest neigh-

bors, which results in a band of filled π orbitals (valence band) and a band of empty π* orbitals

(conduction band).

The honeycomb lattice of graphene and its reciprocal unit cell, or Brillouin zone, is

shown in Figs. 1.2e and 1.2f respectively. Because the lattice structure is made of two interpene-

trating triangular lattices, the K and K´ points of the Brillouin zone, known as the Dirac points,

are not equivalent since they cannot be connected by the unit vectors of the reciprocal lattice.

Thus, there is a valley degeneracy of two in graphene, which later shows up when calculating the

density of states. The electronic band structure of graphene is shown in Fig. 1.3. From the dia-

3

gram, we see that the Dirac point (K or K´) is where the valence and conduction bands meet. Al-

so, the bands are symmetrical around the Dirac point with a linear dispersion relation described

by E = ℏvFk, where vF ≈ 108 cm/s is the Fermi velocity, ℏ = h/2π is the reduced Planck constant,

and k is the 2D momentum. The symmetry of the conduction and valence bands around the Dirac

point indicates that electrons and holes should have equal mobilities, unlike in typical semicon-

ductors like Si, Ge, or GaAs where mobilities are asymmetric, with hole mobility being particu-

larly low.

1.2.1 Graphene-Based Devices

The excellent electrical and thermal properties of graphene hold great promise for appli-

cations in future IC technology [5]. The interesting properties of graphene arise from its two-

dimensional honeycomb lattice of carbon atoms that causes charge carriers to behave as massless

Dirac fermions [6, 7]. Early measurements suggested graphene has high intrinsic mobility

(~40,000 cm2V

-1s

-1) [8] and high thermal conductivity (~600 Wm

-1K

-1) [9], both significantly

greater than in Si and other typical semiconductors (Table 1.1). Thus, graphene has attracted

much attention for its potential IC applications, especially for rf applications. A graphene transis-

tor fabricated from graphene epitaxially formed on a SiC wafer has demonstrated a cutoff fre-

quency as high as 100 GHz (Fig. 1.4) [10].

The absence of a bandgap in graphene results in typical graphene transistors having too

low of ION/IOFF to be used for digital logic [11]. However, by fabricating graphene channels with

very small widths, known as graphene nanoribbons (GNRs), the electron wave vector becomes

quantized in the y direction (where y points in the direction of the narrow constriction with width

W). This quantization changes the dispersion relation so that E(n,kx) = ± ℏvF[kx2+(nπ/W)

2]1/2

where the upper (lower) sign corresponds to the conduction (valence) band and ky = nπ/W where

4

n is an index of the 1D subbands [12]. GNRs with a width of ~15 nm have been shown to pro-

duce energy gaps of ~200 meV (Fig. 1.5) [13]. Therefore, the future possibility of incorporating

graphene into digital logic circuits still remains.

Because of the potential of graphene for use in future IC technology, an accurate under-

standing of carrier statistics and transport properties is necessary for device applications. Despite

many measurements at low fields and low temperatures [14-16], surprisingly little data exists on

the electrical properties of graphene at practical temperatures (T ≥ 300 K) and high electric fields

(F ≥ 1 V/μm) required by modern transistors. In this study, we investigate this range, while de-

veloping a new model for the carrier density including the proper electrostatics and self-heating

at high fields [17, 18]. Applying this model to low-field four-probe conductivity measurements,

we extract graphene mobility as a function of carrier density for temperatures from 300 to 500 K.

By including self-heating effects [17], we extend the charge density model to high-field mea-

surements and calculate electron drift velocities as saturation is approached.

5

1.3 Figures and Table

Figure 1.1: Power density vs. time for computer processors manufactured by

AMD, Intel, and Power PC over the past two decades [19]. The exponential trend

in power density, although flattened by the introduction of multi-core CPUs, is a

limiting factor for the future scaling of IC technology.

Figure 1.2: Allotropes of carbon include (a) graphene, (b) graphite, (c) carbon

nanotubes, and (d) fullerenes. (e) The hexagonal lattice of graphene consists of

two interpenetrating triangular lattices. (f) Brillouin zone with Dirac points lo-

cated at K and K´ [4].

1

10

100

1990 1994 1998 2002 2006 2010

AMD

Intel

Power PC

CP

U P

ow

er D

ensi

ty (

W/c

m2)

Year

Pentium 4(2005)

Core 2 Duo(2006) Atom

(2008)

(a) (b)

(c) (d)

(f )(e)

6

Figure 1.3: Band structure of graphene showing six Dirac (K and K’) points and

a linear dispersion relationship around them [4].

Figure 1.4: Measured small-signal current gain |h21| (the ratio of small-signal

drain and gate currents) as a function of frequency for a 240-nm-gate (diamonds)

and a 550-nm-gate (triangles) graphene field-effect transistor at a drain bias of 2.5

V. Cutoff frequencies were 53 and 100 GHz for the 550-nm and 240-nm devices

respectively [10].

Dirac

Cone

K

K

M

Γ

7

Figure 1.5: Energy gap, Eg, as a function of graphene nanoribbon width, W, for

size GNR device sets [13]. The introduction of a bandgap into graphene-based

devices provides the possibility of using graphene in digital logic circuits.

8

Table 1.1: Electron and hole mobility values and thermal conductivity values for undoped Si,

Ge, and GaAs at room temperature [20] compared to those of intrinsic graphene on SiO2 at room

temperature [8, 9].

Property Symbol Units Si Ge GaAs Graphene

(intrinsic on SiO2)

Electron Mobility μe cm2V-1s-1 1417 3900 8800 ~40,000

Hole Mobility μh cm2V-1s-1 471 1900 400 ~40,000

Thermal Conductivity κ Wm-1K-1 141 61 46 ~600

9

1.4 References

[1] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices, Second ed. Cambridge:

Cambridge University Press, 2009.

[2] V. V. Zhirnov et al., "Limits to binary logic switch scaling - A Gedanken model,"

Proceedings of the IEEE, vol. 91, pp. 1934-1939, 2003.

[3] EPA Report on Server and Data Center Energy Efficiency. Available:

http://www.energystar.gov/index.cfm?c=prod_development.server_efficiency_study,

2007.

[4] A. H. Castro Neto et al., "The electronic properties of graphene," Reviews of Modern

Physics, vol. 81, pp. 109-54, 2009.

[5] A. K. Geim, "Graphene: Status and Prospects," Science, vol. 324, pp. 1530-1534, 2009.

[6] K. S. Novoselov et al., "Two-dimensional gas of massless Dirac fermions in graphene,"

Nature, vol. 438, pp. 197-200, 2005.

[7] Y. B. Zhang et al., "Experimental observation of the quantum Hall effect and Berry's

phase in graphene," Nature, vol. 438, pp. 201-204, 2005.

[8] J. H. Chen et al., "Intrinsic and extrinsic performance limits of graphene devices on

SiO2," Nature Nanotechnology, vol. 3, pp. 206-209, 2008.

[9] J. H. Seol et al., "Two-dimensional phonon transport in supported graphene," Science,

vol. 328, pp. 213-216, 2010.

[10] Y. M. Lin et al., "100-GHz transistors from wafer-scale epitaxial graphene," Science, vol.

327, pp. 662-662, 2010.

[11] P. Avouris et al., "Carbon-based electronics," Nature Nanotechnology, vol. 2, pp. 605-

615, 2007.

[12] T. Fang et al., "Carrier statistics and quantum capacitance of graphene sheets and

ribbons," Applied Physics Letters, vol. 91, p. 092109, 2007.

[13] M. Y. Han et al., "Energy band-gap engineering of graphene nanoribbons," Physical

Review Letters, vol. 98, p. 206805, 2007.

[14] S. V. Morozov et al., "Giant intrinsic carrier mobilities in graphene and its bilayer,"

Physical Review Letters, vol. 100, p. 016602, 2008.

[15] Y. W. Tan et al., "Measurement of scattering rate and minimum conductivity in

graphene," Physical Review Letters, vol. 99, p. 246803, 2007.

10

[16] C. Jang et al., "Tuning the effective fine structure constant in graphene: Opposing effects

of dielectric screening on short- and long-range potential scattering," Physical Review

Letters, vol. 101, p. 146805, 2008.

[17] M.-H. Bae et al., "Infrared microscopy of Joule heating in graphene field effect

transistors," presented at the 9th IEEE Conf. Nanotechnology, Genoa, Italy, 2009.

[18] M.-H. Bae et al., "Imaging, simulation, and electrostatic control of power dissipation in

graphene devices," Nano Letters, DOI: 10.1021/nl1011596, 2010.

[19] E. Pop, "Energy dissipation and transport in nanoscale devices," Nano Research, vol. 3,

pp. 147-169, 2010.

[20] R. S. Muller and T. I. Kamins, Device Electronics for Integrated Circuits, Third ed. New

York, NY: John Wiley & Sons, 2003.

11

CHAPTER 2: FABRICATION AND MEASUREMENT

2.1 Device Fabrication

The devices used in this study are graphene field effect transistors (GFETs). These devic-

es are back-gated, as opposed to a typical top-gated MOSFET, such that the active graphene

channel lies on top of the insulating dielectric (SiO2), which is grown on the Si substrate. The

typical back-gate structure is shown in Fig. 2.1b.

The first step is to thermally grow SiO2 on a highly doped (n++) Si substrate. The sub-

strate is highly doped so that it can serve as the contact for the back gate. The thickness of the

oxide tox is chosen to be either 90 or 300 nm, because due to interference effects for these oxide

thicknesses, it is possible to view an atomic layer of graphene under an optical microscope [1].

The device discussed here has tox = 300 nm. The next step is to anneal the substrate in a chemical

vapor deposition (CVD) furnace at 400 ºC for at least 20 minutes in Ar/H2 [2].

2.1.1 Mechanical Exfoliation of Graphene

Graphene is deposited onto the SiO2 via mechanical exfoliation of natural graphite [3].

This process involves placing a graphite flake onto adhesive tape and then folding the tape over,

thus sandwiching the graphite between two sticky sides. The tape is slowly pulled apart in order

to smoothly cleave the graphite. After repeating this cleaving step ~10 times, the cleaved gra-

phite sample that is stuck to the adhesive tape is placed on the SiO2. Tweezers are used to gently

press out any air between the tape and substrate. The tape is then slowly peeled off. Another an-

neal step is performed in order to remove the adhesive residue [2]. The sample is then placed un-

der an optical microscope, such that monolayer graphene flakes may be identified by the trained

eye (Fig. 2.1a). The size of these flakes may vary but typical devices are made from flakes with

dimensions on the order of microns.

12

2.1.2 Fabricating GFETs from Graphene Flakes

After identifying a suitable graphene flake and patterning markers using electron beam

(e-bream) lithography, contacts are deposited. A bilayer e-beam resist of 495PMMA A2 and

950PMMA A4 (MichroChem) is used instead of a monolayer resist because the 495PMMA A2

bottom layer has a higher etch rate of the two, and thus undercutting will occur when the sample

is placed in the lift-off solution. After metal deposition, this undercutting provides for an easier

metal lift-off. E-beam lithography is used once again to define the area of the contacts. Because

of its success as a contact for carbon nanotubes, the metal of choice for contacting graphene is

palladium (Pd) [4, 5]. Unfortunately, Pd does not stick to SiO2 so a thin sticking layer of Cr is

deposited beforehand, resulting in Cr/Pd (0.5/40 nm) electrodes.

The last fabrication step is to define the graphene channel. Graphene flakes are found in

random geometries, so it is preferable to pattern them into rectangular shapes for simpler charac-

terization of their electrical properties. Therefore, an additional e-beam step followed by a short

oxygen plasma etch (75 W, 100 mtorr, and 15 s) is used to define the graphene channel [6].

2.2 Measurements and Characterization

2.2.1 Raman Spectroscopy of Monolayer Graphene

After device fabrication, Raman spectroscopy is used to confirm that the graphene flake

is indeed monolayer graphene. The Raman 2D peak of monolayer graphene exhibits a single Lo-

rentzian line shape [7]. In this study, Raman spectra were obtained using a Renishaw Raman

spectrometer with a 633 nm laser excitation (power at the object: 10 mW) and a 50× in-air objec-

tive. Figure 2.2 shows the Raman spectrum obtained from the fabricated graphene device shown

in Fig. 2.1b. The single Lorentzian fit to the 2D peak in Fig. S1 confirms that this sample is mo-

nolayer graphene, as does the approximate ratio (1:2) of the G to 2D peaks.

13

2.2.2 Electrical Characterization of GFETs

Electrical measurements on graphene devices are obtained using four electrical probes

and a sample chuck, all in ~10-5

torr vacuum. The four-probe geometry is used in order to isolate

the measured resistance of the graphene channel from the resistance of the graphene-metal con-

tacts. Although we use “invasive” probes that stretch across the entire width of the device, these

inner voltage probes are much narrower (~300 nm) than the graphene dimensions (W = 7 μm, L

= 4 μm for the sample of interest). This means that the electron-hole asymmetry observed in

measurements [8], which originates from the pinning of the charge density below the metal and

the formation of p-p or p-n junctions, is significantly reduced.

The first test is a low-field conductivity vs. back-gate (σ vs. VG0) voltage measurement.

The graphene conductivity, given by σ = (L/W)I14/V23, is determined by sourcing current (I14 = 5

μA) through the outer electrodes while measuring the voltage (V23) across the inner electrodes.

The sample chuck applies a voltage to the Si back gate that shifts the graphene Fermi level. By

shifting the Fermi level, the carrier density, and thus the graphene conductance, is modulated.

The back-gate voltage VG that causes the Fermi level to be positioned at the crossing point of the

“X” bands in graphene is known as the Dirac voltage, called V0 here. If the Fermi level is at the

Dirac point, where the density of states is zero, then a minimum should occur in the number of

free carriers. Thus, the Dirac voltage is experimentally determined by the minimum conductivity

point. When applying a positive VG0, where VG0 = VG–V0, the Fermi level is shifted into the con-

duction band and charge transport is dominated by electrons. On the other hand, when applying a

negative VG0, the Fermi level is shifted into the valence band and charge transport is dominated

by holes. A typical σ vs. VG0 plot at room temperature is shown in Fig. 2.3. These low-field mea-

surements were performed for temperatures from 300 to 500 K. As will be discussed later, the

14

data from these measurements is used to determine the electron and hole mobility in graphene as

a function of charge density and temperature.

The second electrical test in this study was a high-field measurement, such that VG0 was

fixed while a high bias was applied to the outer electrodes. The current (I14) passing though the

entire device and the voltage (V23) across the inner electrodes are measured. The high-field tests

were conducted at background temperatures of 80 K and 300 K. These measurements are used to

extract a relationship between the electron drift velocity and the electric field applied across the

channel and also to determine dependence of the saturation velocity on charge density and tem-

perature (see Chapter 4 for more details on high-field measurements and results).

15

2.3 Figures

Figure 2.1: (a) Optical image of graphene on 300 nm of SiO2. (b) Scanning elec-

tron microscope (SEM) image of graphene sample with W = 7 μm and L = 4 μm

connected to Cr/Pd electrodes with four-probe geometry (graphene colorized for

clarity). Current flows between pads 1-4 and voltage is measured across pads 2-3.

The thermal resistance network used to calculate the average temperature rise un-

der high bias is shown on the left.

Figure 2.2: Raman spectrum showing the G and 2D bands of monolayer gra-

phene. A single Lorentzian (red dashed) is fitted to the 2D peak, as characteristic

of monolayer graphene.

(b)

W

L

SiO2

Si (gate)

R B

R ox

R Si

T

T0

tox

12

3

4

(a)

2650 28500

500

1000

1500

2000

2500

Raman Shift (cm-1)

Inte

nsit

y (

arb

. unit

s)

1450 16500

500

1000

1500

2000

2500

Raman Shift (cm-1)

Inte

nsit

y (

arb

. unit

s)

1450 16500

500

1000

1500

2000

2500

Raman Shift (cm-1)

Inte

nsit

y (

arb

. unit

s) 2D

G

16

Figure 2.3: Low-field conductivity vs. back-gate voltage, VG0 = VG–V0, at 300 K.

V0 is the so-called Dirac voltage and corresponds to the Fermi level positioned at

the crossing point of the “X” bands in graphene. VG0 > 0 corresponds to the elec-

tron-doped regime and VG0 < 0 corresponds to the hole-doped regime.

-40 -20 0 20 400

1

2

VG-V

0 (V)

(

mS)

-40 -20 0 20 400

1

2

3

VG0

(V) (

mS)

EF

EF

17

2.4 References

[1] P. Blake et al., "Making graphene visible," Applied Physics Letters, vol. 91, p. 063124,

2007.

[2] M. Ishigami et al., "Atomic structure of graphene on SiO2," Nano Letters, vol. 7, pp.

1643-1648, 2007.

[3] A. K. Geim and P. Kim "Carbon wonderland," Scientific American, vol. 298, pp. 90-97,

2008.

[4] Y. Zhang and H. J. Dai, "Formation of metal nanowires on suspended single-walled

carbon nanotubes," Applied Physics Letters, vol. 77, pp. 3015-3017, 2000.

[5] D. Mann et al., "Ballistic transport in metallic nanotubes with reliable Pd ohmic

contacts," Nano Letters, vol. 3, pp. 1541-1544, 2003.

[6] B. Ozyilmaz et al., "Electronic transport in locally gated graphene nanoconstrictions,"

Applied Physics Letters, vol. 91, p. 192107, 2007.

[7] L. M. Malard et al., "Probing the electronic structure of bilayer graphene by Raman

scattering," Physical Review B, vol. 76, p. 201401, 2007.

[8] B. Huard et al., "Evidence of the role of contacts on the observed electron-hole

asymmetry in graphene," Physical Review B, vol. 78, p. 121402, 2008.

18

CHAPTER 3: GRAPHENE CHARGE DENSITY MODEL AND MOBILITY

EXTRACTION

3.1 Charge Density Model for GFETs

3.1.1 Graphene Carrier Statistics

To obtain mobility and drift velocity from conductivity measurements, we model the car-

rier density including gate-induced (ncv), thermally generated (nth) carriers, electrostatic spatial

inhomogeneity (n*) and self-heating at high fields. Previous mobility estimates using only ncv

could lead to unphysically high mobility (μ → ∞) near the Dirac voltage (VG = V0) at the mini-

mum conductivity point.

First, we note the gate voltage imposes a charge balance relationship as

0 /cv ox Gn p n C V q (3.1)

where Cox = ϵox/tox is the capacitance per unit area (quantum capacitance may be neglected here

[1, 2]), ϵox is the dielectric constant of SiO2, q is the elementary charge, and VG0 = VG–V0 is the

gate voltage referenced to the minimum conductivity point. Next, the density of states around the

Dirac point, where the dispersion relation is E = ℏvFk, may be given by

Ev

ggE

F

vs

22

)(

(3.2)

where gs = 2 and gv = 2 are the spin degeneracy and valley degeneracy respectively. It is impor-

tant to note that due to the linear dispersion relation in graphene, the density of states increases

linearly with energy, opposed to ρ ~ E1/2

in typical semiconductors like Si. By following [1], we

define an average Fermi level EF such that η = EF/kBT is set by a combination of thermal genera-

tion and gating as

)(2

, 1

2

F

B

v

Tkpn

(3.3)

19

where the upper (lower) sign corresponds to electrons (holes), vF ≈ 108 cm/s is the Fermi veloci-

ty, and j(η) is the Fermi-Dirac integral with j = 1. The mass-action law is given by [1]

1 12

2

1 0thpn n

(3.4)

where nth = (π/6)(kBT/ℏvF)2 is the thermal carrier density and 1(0) = π

2/12.

3.1.2 Modeling Spatial Charge Inhomogeneity

Next, we account for the spatial charge (“puddle”) inhomogeneity of graphene due to

substrate impurities [3-5]. The surface potential can be approximated [2] as a periodic step func-

tion ±Δ (Fig. 3.1) which implies that electron and hole puddles are equal in size near VG = V0.

We relate the potential step to the measured width of the minimum conductivity plateau [6],

which is given by the residual carrier puddle density (n*) due to charged impurities in the SiO2

(nimp). As discussed below, we find n* ≈ 0.297nimp ≈ 2.63×10

11 cm

-2, i.e. a surface potential varia-

tion Δ ≈ 59 meV. This is similar to a previous study (~54 meV) [2], and to scanning tunneling

microscopy results (~77 meV) [5]. The surface potential inhomogeneity is equivalent to a Dirac

voltage variation ΔV0 = qn*/Cox ≈ 3.66 V.

3.1.3 Extracting Impurity Density

The charged impurity density at the SiO2 surface is determined based on the approach

discussed in [7] and given by nimp = BCox|dσ/dVG0|-1

where B = 5×1015

cm-2

is a constant deter-

mined by the screened Coulomb potential in the random phase approximation (RPA) [8] and

dσ/dVG0 is the slope of the low-field conductivity σ = (L/W)(I14/V23). The slope is determined by

a linear fit to σ over a ΔVG0 = 2 V interval around the maximum of |dσ/dVG0| as shown in Fig.

3.2. The value of nimp used here is based on a conductivity measurement at 80 K, where mobility

is limited by Coulomb scattering [9]. From Eq. (10) of [6], we determine n*

≈ 0.297nimp ≈

20

2.63×1011

cm-2

in our sample (averaged over the electron- and hole-doped regimes), where n* is

the residual carrier puddle density representing the width of the minimum conductivity plateau.

From n*, we obtain Δ ≈ ℏvF(πn

*)1/2

≈ 59 meV and ΔV0 ≈ qn*/Cox ≈ 3.66 V in order to model the

spatially inhomogeneous electrostatic potential as given above.

3.1.4 Explicit Expression of Graphene Charge Density

The total carrier density is determined by averaging Eqs. (3.1) and (3.4) for the regions of

±Δ, which can be solved numerically but does not yield an explicit expression. In order to simpl-

ify this, we note that at low charge density (η → 0) the factor 1(η)1(-η)/12(0) in Eq. (3.4) ap-

proaches unity. At large |VG0| the gate-induced charge dominates, i.e. ncv ≫ nth when η ≫ 1. Fi-

nally, we add a correction for the spatial charge inhomogeneity by noting that when this is taken

into account the minimum carrier density is given by n0 = [(n*/2)

2 + nth

2]1/2

. This results from av-

eraging the regions of ±ΔV0 near the Dirac point. Solving Eqs. (3.1) and (3.4) above with these

approximations results in an explicit expression for the concentration of electrons and holes:

2

0

2 42

1, nnnpn cvcv (3.5)

where the lower (upper) sign corresponds to electrons (holes). Equation (3.5) can be readily used

in graphene device simulations, and is similar to a previous empirical formula [10]. Moreover,

we note it properly reduces to the familiar n = CoxVG0/q at high gate voltage, and n = n0 (intrinsic

puddle regime) at gate voltages near V0. Figure 3.3 displays the role of thermal and “puddle” cor-

rections to the carrier density at 300 K and 500 K. These are particularly important near VG0 = 0

V, when the total charge density relevant in transport (n+p) approaches a constant despite the

charge neutrality condition imposed by the gate (n–p = 0). At higher temperatures (kBT ≫ Δ) the

spatial potential variation becomes less important due to thermal smearing and higher nth.

21

3.2 Low-Field Mobility in Graphene at High Temperatures

3.2.1 Electron Mobility

Using the above, we obtain the mobility by measuring conductivity σ = (L/W)I14/V23 as a

function of VG0 at low fields (~2 mV/μm). Mobility vs. carrier density is extracted as μ =

σ/q(p+n) in Fig. 3.4a at various temperatures and VG0 > 0 (n > p), i.e. electron majority carriers

(the hole mobility and additional discussion is given below). Hall mobility measurements yield

identical results over the carrier density regime discussed here (n > 6×1011

cm-2

) as shown in

[11]. The mobility first increases, peaks at ~4500 cm2/V∙s and n ~ 2×10

12 cm

-2 (at 300 K), then

decreases with carrier density. This suggests Coulomb scattering plays a role at low density, and

phonon scattering at higher densities [2]. Mobility decreases with rising T > 300 K for all carrier

densities (Fig. 3.4b). This was also noted in [2], albeit in a lower temperature range.

3.2.2 Hole Mobility and Uncertainty

As for the mobility in the electron-doped regime, the mobility for the hole-doped regime

(VG0 < 0) is obtained and shown in Fig. 3.5a. Given the symmetric energy bands in graphene, the

hole mobility here is similar to the electron mobility from Fig. 3.4a. Only one discrepancy exists

for the 300 K data set, which does not show the typical mobility peak vs. carrier density as in all

other measurements. This is most likely due to the calculated hole density underestimating the

actual value in the device, probably due to a spatial inhomogeneity of the “puddle” regime that is

not accurately predicted by the simple ±ΔV0 potential model. We note the mobility shape recov-

ers at higher temperatures (350-500 K), as thermal smearing washes out such inhomogeneities.

To understand additional uncertainty associated with this method, it is noted in [6] that

for the extracted nimp the predicted plateau width is expected to be correct within a factor of two.

This leads to uncertainty in determining ΔV0, and thus uncertainty in the charge density and ex-

22

tracted mobility values. However, this uncertainty is only notable around the Dirac point, where

the potential ripple contributes to the total carrier density. This limits the “confidence region” in

Figs. 3.4a and 3.5a, with charge density shown only > 0.85×1012

cm-2

. In Fig. 3.5b we estimate

the mobility uncertainty at lower charge densities around the Dirac point, such that the upper and

lower bounds result from a potential ripple of ΔV0/2 and 2ΔV0 respectively.

23

3.3 Figures

Figure 3.1: The spatial inhomogeneity of the electrostatic potential in graphene,

which results in electron and hole “puddles,” is modeled as a periodic step func-

tion with a ripple amplitude of Δ (peak-to-peak height of 2Δ) [2]. For the sample

discussed in this study, Δ ≈ 59 meV.

Figure 3.2: Conductivity vs. back-gate voltage at 80 K. The red dashed lines cor-

respond to linear fits to the 2 V interval around the maximums in |dσ/dVG0|. The

slopes of these lines are used to calculate nimp in accordance with [7].

2650 28500

500

1000

1500

2000

2500

Raman Shift (cm-1)

Inte

nsit

y (

arb

. unit

s)

1450 16500

500

1000

1500

2000

2500

Raman Shift (cm-1)

Inte

nsit

y (

arb

. unit

s)

1450 16500

500

1000

1500

2000

2500

Raman Shift (cm-1)

Inte

nsit

y (

arb

. unit

s)

2D

G

(a)

-20 -10 0 10 200

0.5

1

1.5

2

VG0

(V)

(

mS

)

T0 = 80 K

linear fit regions

( ΔVG = 2 V)

(b)

24

Figure 3.3: Calculated carrier density vs. gate voltage at 300 K (blue) and 500 K

(red) in electron-doped regime (n > p). Solid lines include contribution from elec-

trostatic inhomogeneity n* and thermal carriers nth (both relevant at 300 K), dotted

lines include only nth (dominant at 500 K). Black dashed line shows only contri-

bution from gating, ncv.

Figure 3.4: (a) Mobility vs. carrier density in the electron-doped regime (VG0 > 0,

n > p), obtained from conductivity measurements at T = 300–500 K, in 50 K in-

tervals. The qualitative dependence on charge density is similar to that found in

carbon nanotubes [12]. (b) Mobility vs. temperature at n = 2×1012

(top), 3.5×1012

(middle), and 5×1012

cm-2

(bottom).

0 5 10 150

0.3

0.6

0.9

1.2

VG0

(V)

n+

p (

10

12 c

m-2

)

(b)

gate only

+n0

300 K

+n0

500 K

300 400 5002500

3000

3500

4000

4500

5000

T (K)

(

cm

2/Vs

)

1 2 3 4 5 62500

3000

3500

4000

4500

5000

n + p (1012 cm-2)

(

cm

2/Vs

)

(b)n = 2x1012 cm-2(a)

300 K

500 K

3.5x1012 cm-2

5x1012 cm-2

25

Figure 3.5: (a) Low-field hole mobility vs. carrier density, extracted from four-

probe conductivity measurements taken at T = 300–500 K, in 50 K intervals. (b)

Detail of mobility at 300 K around the Dirac point, with error bars accounting for

the uncertainty in ΔV0 (error > 15% for |n–p| < 4.5×1011

cm-2

).

1 2 3 42500

3000

3500

4000

4500

5000

n+p (1012 cm-2)

(

cm

2/V

s)

300 K

500 K

-0.4 -0.2 0 0.2 0.40

2000

4000

6000

8000

10000

n-p (1012 cm-2)

(

cm

2/V

s)

300 Kμ

p(c

m2/V

∙s)

(a) (b)

26

3.4 References

[1] T. Fang et al., "Carrier statistics and quantum capacitance of graphene sheets and

ribbons," Applied Physics Letters, vol. 91, p. 092109, 2007.

[2] W. J. Zhu et al., "Carrier scattering, mobilities, and electrostatic potential in monolayer,

bilayer, and trilayer graphene," Physical Review B, vol. 80, p. 235402, 2009.

[3] J. Martin et al., "Observation of electron-hole puddles in graphene using a scanning

single-electron transistor," Nature Physics, vol. 4, pp. 144-148, 2008.

[4] Y. Zhang et al., "Origin of spatial charge inhomogeneity in graphene," Nature Physics,

vol. 5, p. 722, 2009.

[5] A. Deshpande et al., "Spatially resolved spectroscopy of monolayer graphene on SiO2,"

Physical Review B, vol. 79, p. 205411, 2009.

[6] S. Adam et al., "A self-consistent theory for graphene transport," Proceedings of the

National Academy of Sciences of the United States of America, vol. 104, pp. 18392-

18397, 2007.

[7] J. H. Chen et al., "Charged-impurity scattering in graphene," Nature Physics, vol. 4, pp.

377-381, 2008.

[8] E. H. Hwang et al., "Carrier transport in two-dimensional graphene layers," Physical

Review Letters, vol. 98, p. 186806, 2007.

[9] J. H. Chen et al., "Intrinsic and extrinsic performance limits of graphene devices on

SiO2," Nature Nanotechnology, vol. 3, pp. 206-209, 2008.

[10] I. Meric et al., "Current saturation in zero-bandgap, topgated graphene field-effect

transistors," Nature Nanotechnology, vol. 3, pp. 654-659, 2008.

[11] L. A. Ponomarenko et al., "Effect of a High-κ Environment on Charge Carrier Mobility

in Graphene," Physical Review Letters, vol. 102, p. 206603, 2009.

[12] Y. Zhao et al., "Multiband Mobility in Semiconducting Carbon Nanotubes," IEEE

Electron Device Letters, vol. 30, p. 1078, 2009.

27

CHAPTER 4: SATURATION VELOCITY IN GRAPHENE ON SILICON DIOXIDE

4.1 High-Field Simulations and Measurements

4.1.1 Thermal Model

High-field drift velocity measurements pose challenges due to Joule heating and non-

uniform potential (and carrier density) along the channel. To account for self-heating we calcu-

late the average device temperature via its thermal resistance Rth (Fig. 2.1b) [1]:

0 B ox SiT T T P R R R (4.1)

where P = I14V23, RB = 1/(hA), Rox = tox/(κoxA), and RSi ≈ 1/(2κSiA1/2

) with A = LW the area of the

channel, h ≈ 108 Wm

-2K

-1 the thermal conductance of the graphene-SiO2 boundary [2], κox and

κSi the thermal conductivities of SiO2 and of the doped Si wafer. The thermal resistance Rth de-

pends on temperature through κox and κSi . These can be written as κox = ln(Tox0.52

) –1.687 and κSi

=2.4×104/T0 by simple fitting to the experimental data in [3] and [4] respectively. Based on the

thermal resistance model, we estimate the average oxide temperature as Tox = (T0+T)/2 and the

temperature of the silicon substrate as the background temperature T0. This allows a simple itera-

tive method for calculating the graphene temperature rise (ΔT) during measurements.

At 300 K for our geometry Rth ≈ 104 K/W, or ~2.8×10

-7 m

2K/W per unit of device area.

Of this, the thermal resistance of the 300 nm SiO2 (Rox) accounts for ~84%, the spreading ther-

mal resistance into the Si wafer (RSi) ~12% and the thermal resistance of the graphene-SiO2

boundary (RB) ~4%. We note that the role of the latter two will be more pronounced for smaller

devices on thinner oxides. The thermal model in Eq. (4.1) can be used when the sample dimen-

28

sions are much greater than the SiO2 thickness (W, L ≫ tox) but much less than the Si wafer

thickness [1].

4.1.2 Electrostatics in the High-Field Regime

To minimize charge non-uniformity along the channel at high fields [5, 6] we bias the

device at high |VG| (generally restricting our samples to average carrier density >2×1012

cm-2

) and

avoid ambipolar transport (VGS–V0 and VGD–V0 must have same sign) [7]. We confirm this with

finite-element simulations [5, 6]. During high-field measurements, the carrier density and tem-

perature can vary across the device [5, 6]. We follow [6] to fully model this regime as shown in

Fig. 4.1. Based on these simulation results, we confirm that it is valid to assume a constant (aver-

age) electric field and relatively uniform charge density across the active region of the device

between the inner electrodes, if the biasing scheme mentioned above is followed. The average

carrier density in the channel is simply given by the average of the densities at electrodes 2 and 3

(as labeled in Fig. 2.1b), while the average field is F = (V2-V3)/L.

4.2 High-Field Drift Velocity in Graphene on SiO2

4.2.1 Velocity-Field Relationship

The drift velocity is v = I14/(Wqn) where n is the average charge density between termin-

als 2 and 3, and the background temperature is set to T0 = 80 K and 300 K. Due to self-heating (T

= T0 + ΔT), the former enables measurements of saturation velocity (vsat) close to room tempera-

ture and the latter above room temperature. Figures 4.3a and 4.3b show the velocity-field rela-

tionship at the two background temperatures, indicating saturation tendency at fields F > 1

V/μm. The drift velocity is fit by

0

1/

0

( )

1m

m

sat

Fv F

F v

(4.2)

29

where μ0 is the low-field mobility and the parameter m = 2 provides the best fit for all carrier

densities and temperatures. To limit the role of self-heating, data was only fit up to ΔT ~ 200 K

(solid symbols). Sample heating much beyond T ~ 200 K can also lead to unreproducible

behavior (e.g. V0 shift) due to thermal stress. We checked that low-field I–VG characteristics

were reproducible after each high bias measurement to ensure no sample degradation due to high

field stress.

4.2.2 Saturation Velocity

Figure 4.3c shows extracted drift velocity vs. electron density (symbols) at F = 2 V/μm,

for the two background temperatures. To interpret the experimental high-field velocity, we com-

pare it with an analytic model (dashed lines). This model approximates the high-field distribution

with the two half-disks shown in the Fig. 4.3c side panel, suggested by previous simulations [8,

9]. This assumes vsat is limited by inelastic scattering with optical phonons (OP) and leads to the

expression:

2

,0 2

2( , ) 1

4

OP OPsat OP

F

v nnvn

(4.3)

where ℏωOP is the OP energy. In the limit of low carrier density this reduces to a constant, vmax =

(2/π)vF ≈ 6.3×107 cm/s (six times higher than vsat in Si) and at high carrier density it scales as vsat

= (2/π)ωOP/(πn)1/2

, dependent both on the OP energy and the carrier density. Equation (4.3) is

valid at carrier densities n > (ωOP/vF)2/(2π) ≈ 9.4×10

11 cm

-2 for ℏωOP = 160 meV and 1.1×10

11

cm-2

for ℏωOP = 55 meV, well within the range of the experiments here.

We consider the limit of two dominant phonon mechanisms in Fig. 4.3c, ħωOP = 55 meV

(dashed, SiO2 substrate OP [10]) and ħωOP = 160 meV (dotted, graphene OP [11]). The model

limited by SiO2 phonons slightly underestimates vsat, while the model with graphene OPs signifi-

30

cantly overestimates the measured vsat. This suggests that both phonons play a role in limiting the

saturation velocity, but that substrate phonons are dominant for graphene on SiO2. (We note that

for device simulations the fit can be optimized using an intermediate value ℏωOP = 78 meV.)

Nevertheless, vsat is greater than in Si for charge densities n < 1.2×1013

cm-2

and more than twice

that of Si at n < 4×1012

cm-2

. With only the graphene OP (ℏωOP = 160 meV) the model suggests

an upper limit for the “maximum” vsat that could be expected in graphene. This intrinsic vsat

could be more than twice as high as that measured here on SiO2 and from two to six times higher

than in Si for the charge density range considered here.

Finally, we note the data suggest a temperature dependence of vsat which has not yet been

included. To understand this, we recall the OP scattering rate is proportional to (NOP + 1), where

NOP = 1/[exp(ħωOP/kBT)–1] is the phonon occupation [12]. This suggests a temperature depen-

dence qualitatively similar to that in Si [13]

,0( , , )

1

sat

sat OP

OP

vv n T

N

(4.4)

where vsat,0 is defined above. This model yields a ~20% change in vsat between T = 280 K and

500 K if the SiO2 phonon is dominant, and a ~2% change if the graphene OP is dominant. The

data in Fig. 4.3c show much closer agreement with the former, once again indicating the strong

effect of the SiO2 in limiting graphene transport.

31

4.3 Figures

Figure 4.1: Using the finite-element simulations discussed in [6], we plot (a)

electron density n, (b) channel potential Vx, (c) electric field F, and (d) tempera-

ture increase ΔT across the length of the device for back-gate voltages of VG0 = 30

V (red), 50 V (green), and 70 V (blue). The simple assumptions of relatively uni-

form charge density and constant electric field (main text) are acceptable if ambi-

polar transport is avoided, and high-field measurements are done at average

charge densities >2×1012

cm-2

. In addition, we note that high-field non-

uniformities may still occur at the outer electrodes (1 and 4) but not in the rele-

vant channel portion between the inner electrodes (2 and 3).

-6 -4 -2 0 2 4 60

2

4

6

x 1012

n (

cm

-2)

-6 -4 -2 0 2 4 6

-15

-10

-5

0

VX (

V)

-6 -4 -2 0 2 4 60

0.5

1

1.5

FX (

V/

m)

-6 -4 -2 0 2 4 60

100

200

X (m)

T

(K

)

-6 -4 -2 0 2 4 60

2

4

6

x 1012

n (

cm

-2)

-6 -4 -2 0 2 4 6

-15

-10

-5

0

VX (

V)

-6 -4 -2 0 2 4 60

0.5

1

1.5

FX (

V/

m)

-6 -4 -2 0 2 4 60

100

200

X (m)

T

(K

)

-6 -4 -2 0 2 4 60

2

4

6

x 1012

n (

cm

-2)

-6 -4 -2 0 2 4 6

-15

-10

-5

0

VX (

V)

-6 -4 -2 0 2 4 60

0.5

1

1.5

FX (

V/

m)

-6 -4 -2 0 2 4 60

100

200

X (m)

T

(K

)

-6 -4 -2 0 2 4 60

2

4

6

x 1012

n (

cm

-2)

-6 -4 -2 0 2 4 6

-15

-10

-5

0V

X (

V)

-6 -4 -2 0 2 4 60

0.5

1

1.5

FX (

V/

m)

-6 -4 -2 0 2 4 60

100

200

X (m)

T

(K

)

1

32

4

L = 4 μm

VG0 = 30 V

VG0 = 50 V

VG0 = 70 V

= inner probes

where V23 is measured

(b)

(a)

(c)

(d)

32

Figure 4.2: Original 4-probe I-V data corresponding to high-field drift velocity

measurements in Fig. 4.3. (a) Data at 80 K, (b) at 300 K background temperature.

All I-V curves were verified to be repeatable, as were subsequent low-field I-VG

sweeps (not shown) re-taken between each high-field I-V. The #1-4 electrode

layout is as labeled in Fig. 2.1b and Fig. 4.1.

0 2 4 6 8 100

2

4

6

V23

(V)I 1

4 (

mA

)

0 1 2 3 40

2

4

6

V23

(V)

I 14 (

mA

)

(b)

(a)

33

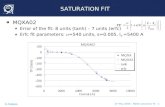

Figure 4.3: Electron saturation velocity vs. carrier density. (a) Background tem-

perature T0 = 80 K with VG0 = 10.5–60.5 V, and (b) T0 = 300 K with VG0 = 23.5–

73.5 V (in 10 V steps from top to bottom). Squares (data), lines (empirical fits),

open squares have ΔT > 200 K from Joule heating and were not used for fit.

Changing fitting criteria to ΔT = 200 ± 100 K results in <8% error. (c) Saturation

velocity vs. electron density at F = 2 V/μm. Side panel shows carrier distribution

assumed for analytic model. Dashed lines show Eq. (6) with ℏωOP = 55 meV

(SiO2) and 160 meV (graphene). The latter also suggests the maximum intrinsic

vsat that could be achieved. Electron vsat for Si and Ge are shown for comparison

[13, 14].

0 3 6 9 12 150

1

2

3

4

x 107

n (1012 cm-2)

vsat (

10

7 c

m/s

)

0 0.5 1 1.5 20

1

2

3

x 107

F (V/m)

v (

10

7 c

m/s

)

0 0.5 1 1.5 20

1

2

3

x 107

F (V/m)

v (

10

7 c

m/s

)

(b)(a)

(c)

ωOP/vF

kx

ky

(a)

T = 300 K + ΔTT = 80 K + ΔT

vsat,Si

vsat,Ge

(b)

34

4.4 References

[1] E. Pop, "Energy dissipation and transport in nanoscale devices," Nano Research, vol. 3,

pp. 147-169, 2010.

[2] Z. Chen et al., "Thermal contact resistance between graphene and silicon dioxide,"

Applied Physics Letters, vol. 95, p. 161910, 2009.

[3] S. M. Lee and D. G. Cahill, "Heat transport in thin dielectric films," Journal of Applied

Physics, vol. 81, pp. 2590-2595, 1997.

[4] M. Asheghi et al., "Thermal conduction in doped single-crystal silicon films," Journal of

Applied Physics, vol. 91, pp. 5079-5088, 2002.

[5] M.-H. Bae et al., "Infrared microscopy of joule heating in graphene field effect

Transistors," presented at the 9th IEEE Conf. Nanotechnology, Genoa, Italy, 2009.

[6] M.-H. Bae et al., "Imaging, simulation, and electrostatic control of power dissipation in

graphene devices," Nano Letters, DOI: 10.1021/nl1011596, 2010.

[7] I. Meric et al., "Current saturation in zero-bandgap, topgated graphene field-effect

transistors," Nature Nanotechnology, vol. 3, pp. 654-659, 2008.

[8] A. Barreiro et al., "Transport properties of graphene in the high-current limit," Physical

Review Letters, vol. 103, p. 076601, 2009.

[9] J. Chauhan and J. Guo, "High-field transport and velocity saturation in graphene,"

Applied Physics Letters, vol. 95, p. 023120, 2009.

[10] M. V. Fischetti et al., "Effective electron mobility in Si inversion layers in metal-oxide-

semiconductor systems with a high-kappa insulator: The role of remote phonon

scattering," Journal of Applied Physics, vol. 90, pp. 4587-4608, 2001.

[11] K. M. Borysenko et al., "First-principles analysis of electron-phonon interactions in

graphene," Physical Review B, vol. 81, p. 121412, 2010.

[12] Y. Zhao et al., "Multiband mobility in semiconducting carbon nanotubes," IEEE Electron

Device Letters, vol. 30, p. 1078, 2009.

[13] C. Jacoboni et al., "A review of some charge transport properties of silicon," Solid-State

Electronics, vol. 20, pp. 77-89, 1977.

[14] R. Quay et al., "A temperature dependent model for the saturation velocity in

semiconductor materials," Materials Science in Semiconductor Processing, vol. 3, pp.

149-155, 2000.

35

CHAPTER 5: CONCLUSION AND FUTURE WORK

5.1 Summary

In summary, we have combined our carrier density model with four-probe conductivity

measurements to extract the low-field mobility and high-field drift velocity in graphene. This

work falls in the T > 300 K and high field F > 1 V/μm regime, where little experimental data ex-

ists. The carrier density model presented here provides explicit expressions for determining the

charge concentration in graphene while accounting for electrostatics and temperature effects. The

low-field data shows that mobility tends to decrease as the temperature increases above 300 K.

As a function of carrier density, mobility increases at low densities due to the dominance of im-

purity scattering. Mobility peaks at a carrier density of ~2×1012

cm-2

(at room temperature), and

then at higher densities, mobility decreases as phonon scattering becomes dominant. When under

high bias, the extracted electron drift velocities approach saturation at fields greater than ~1

V/μm. The high-field velocity shows a strong inverse dependence on carrier density (~n-1/2

but is

more than twice that of Si below 3×1012

cm-2

) and a weak dependence on temperature. Overall,

this study provides extremely relevant information about the electrical properties of graphene.

Both data and models point to the role of the SiO2 substrate in limiting graphene transport. The

models presented are simple yet physical and can be used in device simulations, or to character-

ize graphene on other substrates near room temperature and at high fields.

5.2 Future Work

Because this study has shown that SiO2 plays a dominant role in limiting transport in gra-

phene-based devices fabricated on SiO2, it is important to study transport properties in devices

fabricated on other substrates (e.g. HfO2 or Al2O3). It has been shown that both exfoliated gra-

phene flakes and graphene films grown via CVD (discussed below) can be transferred to arbi-

36

trary substrates [1-3]. Therefore, it is possible to fabricate graphene transistors on various sub-

strates and perform the same electrical measurements as before in order to extract mobility and

saturation velocity as functions of charge density and temperature. These studies will determine

for each substrate whether the limiting mechanisms for graphene transport are due to intrinsic

effects inherent to graphene itself or due to extrinsic effects induced by the substrate. Further-

more, this work will help determine the optimal substrate material for graphene transistors.

In addition to characterizing graphene on other substrates, the characterization of gra-

phene grown by CVD is also relevant. In order for graphene to be implemented into modern in-

tegrated circuit technology, graphene must be synthesized on a large scale. One method of ob-

taining graphene at the wafer-scale is to grow graphene via CVD onto thin foils of metal such as

Cu [4] or Ni [5]. The growth of monolayer graphene on both Cu and Ni has been demonstrated,

where the regions of single layer growth are identified by Raman spectroscopy. A Raman spec-

trum of monolayer graphene grown on a Cu foil transferred onto a SiO2 substrate is shown in

Fig. 5.1. One important aspect to note is the presence of the D peak, which is typically not ob-

served in high quality exfoliated samples. The D peak is induced by disorder, indicating that gra-

phene films grown on Cu are of lower quality than exfoliated graphene flakes [6]. Studying the

electrical properties of these films is necessary for a comparison between transport in CVD gra-

phene and exfoliated graphene. As mentioned above, CVD graphene may be transferred to arbi-

trary substrates such that a comparison of transport in CVD graphene for various substrates may

be performed as well. In conclusion, graphene has shown great promise for applications in IC

technology but more research, such as the work discussed here, is necessary in order to make

graphene a practical option for use in future nanoscale electronics.

37

5.3 Figure

Figure 5.1: Raman spectrum showing the D, G, and 2D bands of monolayer gra-

phene grown on Cu foil and transferred onto a SiO2 substrate. The presence of the

D peak indicates that there is disorder in the sample.

1500 2000 25000

2000

4000

6000

8000

Raman Shift (cm-1)

Inte

nsit

y (

arb

. unit

s)

G

2D

D

38

5.4 References

[1] A. Reina et al., "Transferring and identification of single- and few-layer graphene on

arbitrary substrates," Journal of Physical Chemistry C, vol. 112, pp. 17741-17744, 2008.

[2] A. Reina et al., "Large area, few-layer graphene films on arbitrary substrates by chemical

vapor deposition," Nano Letters, vol. 9, pp. 30-35, 2009.

[3] X. S. Li et al., "Transfer of large-area graphene films for high-performance transparent

conductive electrodes," Nano Letters, vol. 9, pp. 4359-4363, 2009.

[4] X. S. Li et al., "Large-area synthesis of high-quality and uniform graphene films on

copper foils," Science, vol. 324, pp. 1312-1314, 2009.

[5] K. S. Kim et al., "Large-scale pattern growth of graphene films for stretchable transparent

electrodes," Nature, vol. 457, pp. 706-710, 2009.

[6] L. M. Malard et al., "Raman spectroscopy in graphene," Physics Reports-Review Section

of Physics Letters, vol. 473, pp. 51-87, 2009.

39

APPENDIX A: PROCEDURE FOR FABRICATING GFETS ON SILICON DIOXIDE

A.1 Substrate Preparation

1. Acquire substrate with ~90 nm or ~300 nm of SiO2 thermally grown on highly doped Si.

2. Ultrasonicate substrate for 5 min in acetone and then ultrasonicate substrate for 5 min in

isopropanol and then N2 dry.

3. After inserting sample into Atomate carbon nanotube chemical vapor deposition cham-

ber, flow argon and hydrogen gases and check for a leak in the system.

4. Heat up the furnace to 400 °C under argon flow (500 sccm).

5. Anneal sample under argon flow (500 sccm) and hydrogen flow (500 sccm) at 400 °C for

at least 20 min.

6. Cool sample down under argon flow (200 sccm).

A.2 Mechanical Exfoliation of Graphite

1. Place graphite flake onto adhesive tape.

2. Fold over tape and then slowly pull apart in order to smoothly cleave graphite.

3. Repeat steps 2 and 3 (~10 times) until the cleaved graphite appears mostly gray without

vacancies.

4. Bake substrate at 200 °C for 2 min to help remove any moisture.

5. Gently place adhesive tape with cleaved graphite onto substrate.

6. Press out any air for 5 min using the handle of a pair of tweezers.

7. Very slowly peel off tape. This should take 4-5 min.

8. Repeat steps 3-6 from section A.1 in order to remove any adhesive residue. Anneal time

should be at least 60 min in this case.

A.3 Identify Monolayer Graphene

1. View sample under microscope with white light and search for graphene flakes. Mono-

layer graphene flakes will be the most transparent while bilayer and few-layer graphene

flakes will be darker and less transparent.

2. Measure distance of the graphene flake from the closest corner of the substrate. Remem-

ber to scratch a specific corner of the substrate with a diamond scribe in order to later

identify the orientation.

A.4 Pattern E-beam Markers

1. Spin on 495PMMA A2 at 3500 rpm for 30 s.

2. Bake at 180 °C for 5 min and then place on cooling block for 2 min.

3. Spin on 950PMMA A4 at 6000 rpm for 30 s.

4. Bake at 180 °C for 5 min and then place on cooling block for 2 min.

5. Use Raith E-Line to pattern markers (high voltage = 10 kV, aperture size = 30 μm, dose =

160 μC/cm2, current ≈ 0.2 nA).

6. Develop PMMA for 20 s in 1:3 methyl isobutyl ketone (MIBK) to isopropanol.

7. Rinse for 30 s in IPA and then N2 dry.

8. Check under microscope that development was successful. Repeat steps 6 and 7 if under-

developed.

40

A.5 Pattern and Deposit Metal Electrodes

1. Take pictures of sample with markers and then design electrode pattern using ACAD.

2. Spin on e-beam resist (steps 1-4 of Section A.4).

3. Use Raith E-Line to pattern inner electrodes (high voltage = 30 kV, aperture size = 20

μm, dose = 320 μC/cm2, current ≈ 0.14 nA).

4. Use Raith E-Line to pattern outer electrodes (high voltage = 10 kV, aperture size = 120

μm, dose = 130 μC/cm2, current ≈ 6.25 nA).

5. Develop PMMA (steps 6-8 of Section A.4).

6. Place sample in CHA evaporator with Cr and Pd sources.

7. Deposit 0.5 nm of Cr as a sticking layer.

8. Deposit 40 nm of Pd at a rate of ~1-2 Å/s.

9. Remove sample from CHA and place in PMMA lift-off solution of 1:1 methanol to me-

thylene chloride for ~20-30 min.

10. If metal has not lifted off then use a pipet to gently bubble the solution until the metal has

lifted off.

11. Rinse in IPA and N2 dry.

A.6 Pattern and Etch Graphene Channel

1. Spin on e-beam resist (steps 1-4 of Section A.4).

2. Use Raith E-Line to pattern graphene channel, i.e. area around designed geometry to be

etched away (high voltage = 30 kV, aperture size = 20 μm, dose = 320 μC/cm2, current ~

0.14 nA).

3. Develop PMMA (steps 6-8 of Section A.4).

4. Place sample in PlasmaLab RIE.

5. Etch graphene with oxygen plasma (rf power = 75 W, throttle pressure = 100 mtorr, oxy-

gen flow rate = 20 sccm, and etching time ≈ 15 s).

6. Remove sample from PlasmaLab RIE and place in PMMA lift-off solution of 1:1 metha-

nol to methylene chloride for ~20-30 min.

7. Rinse in IPA and N2 dry.