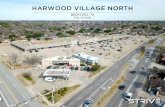

Mike Harwood

-

Upload

praveen-andrew -

Category

Documents

-

view

224 -

download

0

Transcript of Mike Harwood

-

7/28/2019 Mike Harwood

1/26

Mixed Signal Design

byMike Harwood

Distinguished Member of Technical Staff

Texas Instruments LimitedNorthampton, UK

-

7/28/2019 Mike Harwood

2/26

Agenda

What is mixed signal design? Why do we need mixed signal design?

Components available for mixed signal design

Conflicts in technology choice

Simulation challenges Ideal design flow/issues

Typical design turbulence/issues

Layout aspects - things to do and avoid

Debug techniques Conclusions

-

7/28/2019 Mike Harwood

3/26

What is Mixed Signal Design?

Altavista: Mixed signal design 3648 hitsWhat is mixed signal design? 0 hits

Mixed signal designs have both analogue and digital

subsections combined. Overall operation of the systemrelies on both functionality of each section, andinteroperation between the analogue/digital subsections.

-

7/28/2019 Mike Harwood

4/26

Example of a Mixed Signal Design

Memory SERDES

LaserDriverCustomLogicDSPADC

PLLDivideratioClock

N

~analogueInput

-

7/28/2019 Mike Harwood

5/26

Why do we need Mixed Signal Designs?

Lower cost (fewer devices, footprint, pcb area)

Allows complexity not feasible with isolated analogue/digital

sub-systems

Allows approaches not possible with separated solutions.

-

7/28/2019 Mike Harwood

6/26

Components Available

PMOS/ BiPolars Resistors CAPSNMOS

Digital CMOS Yes Vertical NWELL/Poly? MOS/Metal

CMOS+ Yes Vertical NWELL/Poly MOS/Metal/Poly?

BiPolar No Yes Poly Metal N+/Metal/Poly?

BiCMOS Yes Yes Poly Poly/Metal/MOS

-

7/28/2019 Mike Harwood

7/26

Conflicts in Technology Choice

Digital Requirements Process Type

Digital CMOS+ BiPolar BiCMOSCMOS

1. High speed Good Good V Good Good2. High levels of Integration V Good V Good V Poor Fair

3. Low Cost V Good Good Poor Fair4. Low Power V Good V Good V Poor Fair

Analogue Requirements

1. High speed and low I/p cap Fair Fair V Good Good2. High accuracy/low offsets Fair/Poor Fair/Poor V Good Good3. Low Cost Fair Fair V Good Good4. Analogue component availability Fair Good Good V Good5. Low power Poor Poor V Good Good

-

7/28/2019 Mike Harwood

8/26

Conflicts in Technology Choice

There is no universal solution.

Choice depends on how much analogue/digital and anyshowstopping requirements.

At TI the trend is towards the cmos+ choice and user ofclever techniques to solve analogue accuracy/offset problems.

The cmos+ solution is the most cost effective solution if largenumbers of gates need to be integrated.

-

7/28/2019 Mike Harwood

9/26

Simulation ChallengesMain Simulation Areas Architectural analysis:- MATLAB/SIMULINK

analogue sections: high accuracy needed for relatively small circuits. E.g. SPICE orSPECTRE

Digital sections:- high speed (many clock cycles) need simulating for largecircuits. E.g. MODELSIM, NC_VERILOG, VSS

Top level simulations:- Needs to support both of the above criteria. Mixed mode simulatorshave been available for 10+ years. TimeMill/PowrMill are often used.

Other Simulation areas Substrate analysis/crosstalk:- Software exists to characterise and simulate parasitic interactions.

Parasitic extraction:- Layout resistances, inductances, capacitances can be added toto simulations to improve accuracy (+ reduce speed).

Electromigration/IR drop:- Software can accurately predict localised problem areas.

Note New software is available on a weekly basis.

-

7/28/2019 Mike Harwood

10/26

Ideal Design Flow

AnalogueSchematic

Capture

AnalogueSimulation

Verilog/VHDLDesign

DigitalSims

Synthesis TopLevel

Top LevelSim (mixed)

STA etc

Layout(Custom and

P&R)

B.A

Checks

Go

Custom DigitalDesign

DigitalSims

Gate levelSims

-

7/28/2019 Mike Harwood

11/26

Issues with Ideal Design Flow

Computing power/time for top level simulation is normallyprohibitive.

TI is currently having success with this flow for smallmixed signal designs.

-

7/28/2019 Mike Harwood

12/26

Typical Design Turbulence

Analogueschematics

AnalogueSim

AnalogueLayout

Selectiveback

annotation

SelectiveBA sim

Characterisationanalogue models

Analogue

complete

Verilog/VHDL

DigitalSim (RTL)

CustomDig

GateLevelsim

Synthesis Top levelrepresentation

Top levelSim/STA

DigitalLayout

B.A

Checks + GO

Combineanalogue/digital

-

7/28/2019 Mike Harwood

13/26

Issues with the Design Turbulence

Accuracy of characterised analogue blocks (analogue models). Non-linear, non-simple effects cause problems unlessthoroughly characterised.

Noise injection (substrate + supplies) not easily modelled.

Asynchronous real world events not readily modelled.

Electromigration/ESD issues often need considering outsidethe normal design flow.

Normally the design flow needs refinement depending on theamount and relative proportions of analogue/digital circuitry.

Overall

-

7/28/2019 Mike Harwood

14/26

Layout Aspects

It is very difficult to simulate non-intentionalinteractions between analogue and digital sections,

Guardringing (if appropriate) can give a degree of noiseisolation between analogue and digital sections.

However, this is not the whole story.

-

7/28/2019 Mike Harwood

15/26

Tball layout plot

Example Layouts

-

7/28/2019 Mike Harwood

16/26

Things to do

Keep analogue/digital supplies separate.

Keep analogue circuitry differential where possible.

Design analogue circuits to rely on device matching ratherthan absolute parameters.

Analyse guardrings wrt process and use if applicable.

Simulate in as much detail as possible.

-

7/28/2019 Mike Harwood

17/26

Things to avoid

Large current switching i/os close to analogue circuitry.

Routing high speed digital lines close to analogue referencesignals.

Differential ground noise.

Matching small or well separated devices.

Forgetting Ohms law!!!

-

7/28/2019 Mike Harwood

18/26

Things we should have avoided

-

7/28/2019 Mike Harwood

19/26

Things we should have avoided

-

7/28/2019 Mike Harwood

20/26

Things we should have avoided

-

7/28/2019 Mike Harwood

21/26

Things we should have avoided

-

7/28/2019 Mike Harwood

22/26

Things we should have avoided

-

7/28/2019 Mike Harwood

23/26

Things we should have avoided

-

7/28/2019 Mike Harwood

24/26

Things we should have avoided

-

7/28/2019 Mike Harwood

25/26

Debug techniques mainly analogue

Board level measurement at device pins.- Nature of digital problems can usually be identified this way.- Digital constraints can be tightened normally allowing correlation.- analogue problems can be identified at device pins.

Focussed Ion beams can be used to cut and modify metal connections

to investigate circuit configurations, e.g. FEI, Schlumberger.

Backside diagnostic probing can be used to investigate flip-chip designs.

Electron beam measurements e.g IDS5000 can be used to measuresignals without loading them. Signal resolution is restrictive for

analogue work.

-

7/28/2019 Mike Harwood

26/26

Conclusion

Mixed signal design is good fun.

Mixed signal design breaks all the software known to mankind.

There is often not a right answer only a slightly less wrong answer.

If it cant go wrong it will go wrong.

The lab is for keeping us out of the pubs on winter evenings.