Metallization of Submicron Features in High-End Semiconductor Devices by Copper Electroplating Uziel...

-

Upload

jazmine-hawkins -

Category

Documents

-

view

223 -

download

0

Transcript of Metallization of Submicron Features in High-End Semiconductor Devices by Copper Electroplating Uziel...

- Slide 1

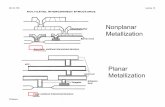

Metallization of Submicron Features in High-End Semiconductor Devices by Copper Electroplating Uziel Landau Department of Chemical Engineering Case Western Reserve University Cleveland, OH 44106 [email protected] Presented at ENERGIZER 2/4/05 Slide 2 High-Tech: CVD, PVD deposition of semiconductors Drugs development CatalysisLow-Tech: Oil refining Electrical machinery Steel manufacturing Underlying science is well-established: Electroplating (some aspects) Technology precedes the science empiricism Slide 3 Outline Overview of Copper Interconnect Metallization Rationale for this work Analyzing the additives effects* Experimental Investigations Modeling of Additives Transport + Adsorption Simulation of the via-fill process Scaling Issues & Wafer-scale Conclusions Slide 4 Slide 5 Recent Microprocessors 70 Million transistors/processor ~ 70 Million transistors/processor ~ 300 Million interconnects/processor ~ 200 Processors/200 mm wafer Metallized Wafer Slide 6 To reduce t - Lower resistivity () Lower dielectric constant (K) t = R C Device Speed vs. Size Time Constant Interconnect resistance R Smaller line size Longer Time delay GATE INTERCONNECT DEVICE GATE VIA TRENCH r SiO 2 Al2.65 cm Cu1.68 cm Ag1.59 cm J. Dahm and K. Monnig, Sematech, AMC 1998 Conf. Proceedings, pp. 3-15. smaller Slide 7 Interconnect Cross-section Moving from Al to Cu Interconnects Al InterconnectsCu Interconnects Transistor Gate Slide 8 Copper Interconnect Metallization Etch Via SiN Etch stop Insulator (SiO 2 ) Routes for copper metallization: PVD (0.05-0.1 /min) CVD (0.2 /min) Electroless plating (0.2 /min) Electroplating (1 /min) DUAL DAMSCENE Etch Trench PVD barrier Copper seed Electrodeposited copper After CMP Introduced by IBM (Andricacos, Uzoh, Dukovic, Horkans, Deligianni) - 1998 Slide 9 Advantages of Copper Metallization Higher conductivity Reduced time delay Higher current density at lower power Scalability finer lines at lower levels Improved EM performance Fewer steps Dual Damascene Process Fewer defects Less equipment, space Lower cost Faster processing Less costly equipment Environmentally benign Introduced by IBM (Andricacos, Uzoh, Dukovic, Horkans, Deligianni) - 1998Introduced by IBM (Andricacos, Uzoh, Dukovic, Horkans, Deligianni) - 1998 Commercially implemented ( IBM, Intel, Motorola/AMD, TI,) - 2001Commercially implemented ( IBM, Intel, Motorola/AMD, TI,) - 2001 Slide 10 Issues in Copper Metallization Attitude- Extending wet chemistry to dry semiconductor processing Extending wet chemistry to dry semiconductor processing Doubting the ability of plating to meet the challenge Doubting the ability of plating to meet the challenge Meeting unparalleled requirements of purity and precision Meeting unparalleled requirements of purity and precisionTechnical- Via scale: Via scale: Bottom up fill Bottom up fill Seed layer in aggressive geometries ( One-dimensional Unsteady-State Model Transport Model for a Via with Sloping Reactive Sidewalls : Diffusional Flux IN OUT Adsorption > 0 < 0 Diffusion IN = Diffusion OUT + Adsorption + Accumulation Diffusion = Adsorption = Effect of varying radius stronger on transport Slide 79 One-dimensional Unsteady-state Model Surface Coverage at the via bottom ( PEG ) Time t (s) SLOWER Transport FASTER Transport = -1.1 o = 0 o = 10 o Slide 80 Quantitative Modeling of Via-Fill Time Scales t 10 st > 10 s Transport-kinetics time scale Additives Interaction time scale SHORTLONG PEG SPS Slide 81 Transport Kinetics Time Scale PEG SPS Generation of differential plating kinetics between the via top and bottom initiation of superfill. Copper deposition preferentially occurs at the via bottom. t 10 s SHORT Slide 82 additives distributionRequires additives distribution kineticsEffect of additives surface coverage on the kinetics NUMERICAL APPROACHNUMERICAL APPROACH Solution of the Nernst-Planck Equations or a simplified case (Laplaces Equation) Time stepping moving boundary SEMI-QUANTITATIVE APPROACHSEMI-QUANTITATIVE APPROACH Neglect concentration variations inside the via Move electrode boundaries on the basis of local kinetics using Faradays law Simulation of Via-Fill Slide 83 Simulation of Deposit Propagation Variable kinetics + Moving boundaries 2 =0 2 C =0 i = f ( ) Passivated kinetics (PEG->SPS) Accelerated kinetics (SPS) Variable kinetics [Partially passivated, f(t)] Virtual electrode; Outer edge of diffusion layer C Slide 84 Numerical Simulation of Via-Fill Variable Kinetics* * U. Landau, E. Malyshev, R. Akolkar and S. Chivilikhin, AIChE Proceedings (2003). Cell-Design Simulations MOVING BOUNDARIES Fill Time: 48 sec. Overpotential: - 124 mV Bottom: i = 60 mA/cm 2 Top: i = 0.24 mA/cm 2 3.4 mA/cm 2 (Depolarization by SPS) Sidewalls: Interpolated kinetics between Top and Bottom SiO 2 Electrolyte SiO 2 Electrolyte Slide 85 SiO 2 Electrolyte Seam Cell-Design Simulations Via Fill Simulation Plating Time: ~147 sec. Overpotential: - 80 mV Bottom: i = 10 mA/cm 2 i 0 = 1.12 mA/cm 2 C = 0.83 Top: i = 0.05 mA/cm 2 4.8 mA/cm 2 High Depolarization by SPS: i 0 = 3.1 A/cm 2 0.28 mA/cm 2 C = 0.9 Sidewalls: Interpolated kinetics between Top and Bottom Current density has been lowered: No Bottom-Up Fill No Bottom-Up Fill 1 sec time intervals Slide 86 z* r* 10 s 20 s 30 s 35 s Flat Bottom- up Growth i avg =63 mA/cm 2 SIMULATIONS OF THE VIA-FILL = 120 mV PEG = 100 ppm SPS = 20 ppm VIA-FILL *V. Dubin, Microelectronic Engineering, 70, 461, 2003. Slide 87 z* r* Seam after 900 s Conformal Deposition = 120 mV PEG = 100 ppm SPS = 0 ppm VIA-FILL SIMULATIONS: Effect of SPS = 120 mV PEG = 100 ppm SPS = 100 ppm z* r* 15 s Rapid depolarization on the via sidewalls Center- line Voids Slide 88 Growth Profile at Low overpotential z* r* Seam after 75 s Low bottom-up current density i ~ 12 mA/cm 2 = 80 mV PEG = 100 ppm SPS = 20 ppm Bottom cannot escape depolarizing sidewalls GOOD BAD Slide 89 Modeling of Superfill Effect of Current Density C peg =200 ppm C sps =20 ppm Via AR = 10 V = 130 mVV = 60 mV Bottom-up growth Seam at the mouth due to depolarizat ion by SPS 30 s 200 s 1 mA/cm 2 21 mA/cm 2 Slide 90 Wafer-scale Modeling Rationale for study Only wafer-scale parameters, e.g., total current (I) or voltage (V) are measurable current/ potentialwaveformsOptimize the process by identifying current/ potential waveforms Transient nature of wafer-scale processes due to: Transient additives interactions Geometry changes during via-fill Slide 91 Wafer-scale Modeling 300 mm wafer 0.2 dia., 1 deep vias (via loading ~ 6 %) Empirical observations during wafer metallization: Current is initiated upon wafer immersion Initial overall current is low Current is increased as via-fill is initiated Slide 92 Wafer-scale Modeling Current balance on the entire wafer : Assuming inhibited sidewall kinetics similar to the wafer top The wafer geometric current density : Slide 93 Wafer Current Density, mA/cm 2 Time, s Wafer-scale current transients Rapid wafer depolarization at short times (t < 10 s) Wafer current drops at long times (t>25s) SPS = 20 ppm PEG = 100 ppm Wafer Current, A = 0.12 V (constant Driving force) Slide 94 Wafer Current Density, mA/cm 2 Time, s Comparison with Experiments Model predictions in agreement with experiments * Experimental data: J. Reid et al., Electrochem. Solid-State Lett., 6(2) C26 (2003). Source: J. Reid et. al.* Slide 95 Wafer Current Density, mA/cm 2 Time, s Wafer-scale i vs. t : Effect of potential = 0.12 V VIA-FILL COMPLETION SPS = 20 ppm PEG = 100 ppm Via loading = 6.3% = 0.13 V Slide 96 Wafer Current Density, mA/cm 2 Time, s Wafer-scale i vs. t : Effect of SPS conc. SPS = 20 ppmDefect-free Fill = 0.12 V PEG = 100 ppm Via loading = 6.3% SPS = 30 ppm Centerline Voids Slide 97 Wafer Current Density, mA/cm 2 Time, s Wafer-scale i vs. t : Effect of via loading Via loading = 6.3% = 0.12 V PEG = 100 ppm SPS = 20 ppm Via loading = 12.6% Slide 98 Wafer Voltage (mV ) Voltage Implication of Constant Current Time, s Wafer Current Density, mA/cm 2 Time, s SPS =` 20 ppm PEG = 100 ppm = 0.12 V (constant Driving force) Current 120 Too high bottom defects Too low centerline defects Slide 99 A comprehensive model for the bottom-up fill is presented. WITHOUT invoking any adjustable parameters Based on experimentally characterized additives effects The model explains: Specific role of the PEG and SPS in the multi- component additives system The effect of operating parameters and via geometry Wafer-scale current response. Major Conclusions Slide 100 Acknowledgements: Case Prime Fellowship to Rohan Akolkar General Motors Research and Development The Dept. of Chemical Engineering, CWRU John DUrso David Rear Mark Bubnick Applied Materials Yezdi Dordi Peter Hey THANK YOU ALL! Dr. Rohan Akolkar Slide 101 Slide 102 Additives Distribution during TK time scale PEG Surface Coverage Normalized depth, z* SPS Surface Coverage Via TopVia Bottom No PEG or SPS on the via sidewalls at t = 0 t = 0 s Slide 103 Additives Distribution during TK time scale PEG Surface Coverage Normalized depth, z* SPS Surface Coverage Via TopVia Bottom Inhibited Via Top PEG-free bottom with some SPS t < 1 s Slide 104 Additives Distribution during TK time scale PEG Surface Coverage Normalized depth, z* SPS Surface Coverage Via TopVia Bottom Inhibited Via Top Accelerated Via Bottom t ~ 4 s Slide 105 PEG Surface Coverage Normalized depth, z* SPS Surface Coverage Via TopVia Bottom High PEG Low SPS Low PEG High SPS t ~ 8 s Additives Distribution during TK time scale