lvds thesis 1

-

Upload

avinash-thota -

Category

Documents

-

view

231 -

download

9

Transcript of lvds thesis 1

Introduction

With the recent developments in the communications market, the demand for throughput

is becoming increasingly more crucial. Although older differential technologies provide

significant signal integrity benefits compared to single ended technologies, many of them

consume much more power at lower throughput than LVDS.

The LVDS standard was created to address applications in the data communications,

telecommunications, server, peripheral, and computer markets where high-speed data

transfer is necessary. LVDS offers a low cost, high speed, low power solution when

compared to the standards of the past.

The ever-increasing processing speed of microprocessor motherboards, optical

transmission links, intelligent hubs and routers, etc., is pushing the off-chip data rate into

the gigabits-per-second range. However, unlike internal clocks, chip-to-board signaling

gains little benefit in terms of operating frequency from the increased silicon integration.

In the last decade, high data rates were achieved by massive parallelism, with the

disadvantages of increased complexity and cost for the IC package and the printed circuit

board (PCB). For this reason, the off-chip data rate should move to the range of Gb/s-per-

pin in the near future. Indeed, while the reduction of the power consumption is of great

concern in battery-powered portable systems, it is also required in other systems to

reduce the costs related to packaging and additional cooling systems.

Low-voltage differential signaling (LVDS) technology was developed in order to provide

a low-power and low-voltage alternative to other high-speed I/O interfaces for point-to-

point transmission, such as emitter-coupled logic (ECL). LVDS achieves significant

power savings by means of a differential scheme for transmission and termination, in

conjunction with a low voltage swing.

LVDS standards pose relatively stringent requirements on the tolerance affecting the

output levels, raising interesting design issues if low-cost solutions with neither external

components nor trimming procedures are required. At the same time, the very large

variation tolerated for the common-mode voltage at the input of a LVDS receiver

requires several design improvements over the typical architecture if transmission speeds

in the gigabits-per-second range must be achieved. It should be remarked that a recent

standard recommends a maximum data rate of 655 Mb/s, forecasting data rates of 1.5

Gb/s in the near future with low-loss media. At the moment, commercial LVDS chipsets

are specified for operation in the megabits-per-second range.

What is LVDS?

LVDS is defined in the TIA/EIA-644 standard. It is a low voltage, low power, differential

technology used primarily for point-to-point and multi-drop cable driving applications.

The standard was developed under the Data Transmission

Interface committee TR30.2. It specifies a maximum data rate of 655 Mbps although

some of today’s applications are pushing well above this specification for a serial data

stream.

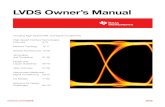

FIGURE 1. Signal Level Comparison

Differential Transmission

Differential transmission addresses many of the shortcomings of single-ended solutions

by using a pair of signal lines for each information channel. Figure 2 shows an electrical

schematic diagram of a differential transmission system. The differential driver uses a

pair of complementary outputs to indicate the state transmitted. The differential receiver

detects the voltage difference between the signal pair, rather than relative to ground, to

determine its output state.

This mode of transmission has several important advantages over single ended. You can

see the fundamental advantage in the derivation of the differential input voltage, VID, in

Figure . The noise sources VN and VG add to the input signals VIA and VIB, just as with

the single-ended circuit, but by taking the difference between the two input voltages, the

common noise terms are cancelled from the desired signal. The differential receiver

accomplishes this and, with small differential input voltage thresholds, maintains high

signal-to-noise ratios.

Figure2. Differential Interface Circuit Schematic Diagram

There is a presumption that the VN coupled to each signal line are equal or nearly so.

Differential signal pairs that are close together are generally exposed to the same noise

sources. Twisting the signal wires together adds to this advantage. This ensures similar

exposure to electric fields and cancels differential emf from magnetic field coupling by

reversing the polarity in adjacent loops created by the twist.

In addition to noise immunity, differential circuits radiate substantially less noise to the

environment than single-ended circuits. This is primarily due to the complementary

current in each line of the signal pair canceling each other’s generated fields. Conducted

noise is also lower because there is little common-mode current to circulate through the

signal return path.

Differential signaling adds cost and complexity in silicon and interconnecting hardware

where it is roughly double that for a single-ended interface. As signaling rate or the

number of circuits increase, this becomes less of a disadvantage as you add ground wires

to make the single-ended signaling work. Indeed, you can find few data interfaces above

10 Mbps or longer than a half meter or so that are not differential

Differential signaling offers many advantages over single ended technologies. LVDS

signaling centers around 1.25V with a 350 mV swing and is not dependent on power

supply voltage. Not only does this result in a faster, more stable signal, it also makes

migration to lower power supply voltages much easier.

Another advantage to differential technology is that the balanced

differential lines have tightly coupled equal but polar opposite signals which reduce EMI.

The magnetic fields radiated by each of the conductors are drawn toward each

other and cancel much of the magnetic fields.

Common Mode

Differential signaling also offers common mode rejection. The receiver ignores any noise

that is coupled equally on to the differential signals and only considers the difference

between the two signals. The receiver has a common mode voltage range of 0.05V to

2.35V. LVDS receivers will operate with as much as a r1V ground shift between the

driver and receiver. This is shown graphically in Figure 3. Low swing differential

signaling can also improve signal integrity concerns at higher speeds. As throughput

demands increase throughout the information industry, higher frequencies and wider bit

widths cause transmission line reflections and crosstalk.

As system loading increases, the characteristic impedance of a system

can change and cause impedance mismatches which will, in turn, send reflective signals

across the transmission line. These reflections can cause bit errors or increase settling

times making timing budgets more difficult as speeds increase. Differential signaling

technologies like LVDS solve this by accepting common mode noise on the differential

line. Additionally, lower swing differential technologies reduce reflections by having

small voltage swings which limit the energy supplied to the transmission line.

FIGURE 3. Common Mode Noise Range

Termination

Termination of LVDS is necessary at the receiver input to generate the Output

Differential Voltage (VOD). The TIA/ EIA-644 specification stipulates an internal

termination resistor value between 90Ω and 132Ω. Fairchild recommends a termination

resistor value between 90Ω and 110Ω depending on the characteristic impedance of the

cable. Termination of LVDS is much easier than most other technologies. ECL and

PECL both use a 220Ω pull-down resistor on each driver output as well as a 100Ω

resistor across the driver outputs. GTLP, due to the open drain configuration, must have a

termination resistor (usually 50Ω double terminated) to a 1.5V pull-up voltage in order to

generate a GTLP signal.

Fast Switching Speeds

Typical slew rates for LVDS are under 1 ns when measured from 10% to 90% of the

edge. When edge rates approach less than half the time of the distance to he load, the load

can no longer be thought of as a lumped load and transmission line effects must be

considered. Because LVDS is most often used in driving cables and in backplanes,

transmission line effects are a concern for the system designer.

One of the largest contributors to bit error in medium to long cable and bus driving

systems is reflections. Reflections are caused by mismatches in line impedance which

cause inductive and capacitive ripples in the signal which, in turn, reduce the driver’s

ability to provide a clean signal to the receiver. For this reason, it is essential for the

impedance of all cables, connectors, busses, and termination resistors to be closely

matched. The LVDS common mode rejection feature helps to minimize reflections

caused by mismatched transmission lines.

Jitter

There are many ways that digital jitter can effect a system operation. A transmission

channel typically passes signals at a specific bit rate or within a range of bit rates. Jitter

has the effect of shortening some bits, while lengthening others. This shortening of bits

can increase the signal speed and cause dropped bits in the transmission. Additionally,

excessive jitter can cause dropped bits due to the system’s internal timing correction

system not having the ability to track the signal. Jitter can be defined as a type of line

distortion caused by a random variation in a signal’s reference timing position. The

deviation can either be leading or lagging the ideal position.

Jitter is usually expressed in picoseconds (ps), as a percent (%), or as a unit

interval fraction (UI) and can be caused by a number of factors including reflections,

noise and crosstalk. Jitter is divided in to three basic categories: Deterministic jitter,

random jitter, and frequency dependent jitter. Deterministic jitter is typically a result of

phase changes which are correlated to specific events like data path bandwidth

limitations. Random jitter is often caused by thermal noise and other random variables

that are not necessarily related to specific events. Frequency-dependent-jitter is typically

caused by things such as power supply noise and crosstalk.

Point-to-Point Configuration

LVDS drivers and receivers perform optimally when used in systems designed as point-

to-point configured systems. The transmission line must be terminated at the receiver

with a termination resistor between 90Ω and 110Ω(100Ω is the recommended typical

resistor value) placed as close to the receiver inputs as possible. Most twisted pair cables

are designed to about 100Ωimpedance, so a 100: termination resistor is recommended to

avoid transmission line. Mismatches, which will result in reflections and other

discontinuities. Figure 4 shows an example of a typical point-to-point configuration using

LVDS.

FIGURE 4. Typical Multi-Drop Configuration

Multi-Drop Configuration

LVDS can also be used in a multi-drop design typically found in backplanes as well as

box-to-box applications providing the media transmission distance is short. In a typical

multi-drop system, the termination resistor must be located at the receiver that is located

at the far end of the bus. This is illustrated in Figure 5

FIGURE 5. Typical Multi-Drop Configuration

When flight time from the driver to the receivers is crucial, the system can be designed to

drive from the center to the bus. Termination resistors are needed at each end of the bus

in order to prevent reflections.

Although this arrangement is preferred when high frequencies dictate short

signal propagation across the transmission line, the termination resistors are seen by the

driver as two parallel resistors and therefore the driver must provide twice the current to

drive the bus. Figure 6 illustrates a multi-drop configuration with the driver at both the

end of the bus and the center of the bus.

FIGURE 6. Center Driven Multi-Drop Configuration

Multi-Point Configuration

Although LVDS, as defined in the RS644 standard, does not have the dynamic current

drive to support a multi-point bus system, there is a high drive LVDS available which has

a higher drive compared to the 3.5 mA drive of standard LVDS. Fairchild Semiconductor

works on a committee that is addressing a new specification for high drive LVDS, or M-

LVDS (Multi-point Low Voltage Differential Signaling).

In a multi-point system, the driver can be located at any point along the bus. For this

reason, much like the multidrop center driven bus previously discussed, a termination

resistor is required at each end of the bus. This also means that the driver sees the two

resistors in parallel and must supply twice the current to the bus. The 11 mA dynamic

drive is provided on the high drive version of LVDS to address a multi-point

configuration. Figure 7 gives a typical example of a multi-point system.

FIGURE 7. Multi-Point Configuration

LOW-POWER/LOW-VOLTAGE EFFECTS ON CMOS

TECHNOLOGY

Introduction to CMOS

In order to understand the effects of low-power/low-voltage on Complementary Metal

Oxide Silicon (CMOS) devices, an understanding of how the individual CMOS devices

work is essential. CMOS technology incorporates N-channel and P-channel devices

together to benefit from what each has to offer. CMOS technology is known for being

very power efficient, making it the obvious choice for a low-power/low-voltage

application.

In the case of an enhancement-mode N-channel CMOS device, N+ source and drain

regions are implanted into a lightly doped P-type silicon substrate, and a thin Si02 gate

oxide separates a polysilicon gate contact from the surface of the silicon (Figure 2.1). The

silicon substrate is often connected to the source to keep it from having a floating

potential, but it can also be connected to either power or ground as necessary.

Figure N-channel CMOS Transistor.

Parameters important to the design and operation of a CMOS device include threshold

voltage, capacitance, body effect, narrow channel effects, sub-threshold current, and

short-channel effects. All of these parameters impact the operation of a CMOS device

directly, and especially take effect when implemented with small geometry and low-

voltage.

Introduction to Threshold Voltage

CMOS devices can be thought of as switches. The threshold voltage is basically the gate

voltage necessary to induce a conducting channel in the CMOS device, or the voltage

necessary to turn the switch "on". This definition has exceptions such as Nchannel

depletion mode transistors. In N-channel depletion mode transistors, a channel already

exists and the device is normally in the "on" state when the gate voltage is at zero. A

negative gate voltage is required to turn the device off.

For normal or enhancement mode devices, before the gate voltage reaches the threshold

voltage, the MOS device is in the "weak inversion" region, and can be considered off

with little or no current flowing between the source and drain regions. When the gate

voltage of a long channel MOS device is not positive enough to reach the threshold

voltage, the width of the depletion region under the gate is a function of the gate voltage .

When a strong positive voltage is applied to the gate terminal relative to the source

terminal of an NMOS device, negative charges are induced in the P-type depletion region

below the gate. A channel forms near the surface of this region made up of the induced

negative charges, temporarily giving the area near the surface of the P-type material

properties of N-type material. This phenomenon is known as inversion, and is the means

for which MOS transistor operation can occur. Mobile electrons are able to travel

between the source and drain during inversion (Figure 2.2).

Figure 2.2. Diagram of Conducting Channel in an N-channel CMOS Transistor.

Increasing the gate voltage further leads to strong inversion. Strong inversion occurs

when the surface of the conducting channel is just as strongly N-type as the substrate is

P-type. The length of the depletion region continues to grow until strong inversion is

reached. Once in strong inversion, increasing gate voltage ceases to increase depletion

width and only increases inversion. The voltage required for strong inversion is known as

the threshold voltage of the device.

Once threshold voltage is reached, an increase in drain voltage causes the channel to

pinch off on the drain end of the MOS device and the drain current saturates. The MOS

device is now said to be in the saturation region of operation where the drain current is

essentially linear for any further increase in drain voltage. As Figure 2.3 depicts, for a

given gate voltage there is a drain voltage that causes the drain current of the device to

become saturated.

Figure 2.3. Diagram of Current-Voltage Relationship for an N-Channel CMOS

Transistor

Similarly. P-channel devices are made on an N-type substrate with P+ implanted source

and drain regions. A negative voltage with respect to the source voltage is applied to the

gate, and positive charges (holes) are induced in the N-type depletion region. The channel

between the source and drain terminals are formed and allow current conduction between

the source and drain terminals of the device.

Threshold Voltage and Effects of Real Devices

Solving Poisson’s equation in the depletion region under the channel provides a

simplified threshold voltage formula. Using Gauss's law at the interface, since the

displacement is continuous, the displacement at the oxide interface is equivalent to the

overall space charge in the substrate depletion region [3]. The ideal threshold voltage

required for strong inversion can be expressed as:

Where Qd is the charge per unit area in the depletion region at strong inversion, Ci is the

capacitance per unit area of the gate oxide insulator, and (J>F is the Fermi level. This is a

simplified equation that increases in complexity when used to describe real devices.

When actual devices are made, threshold voltage and other properties are great affected

by criteria not taken into account by the ideal case described above. There are charges at

the Si-SiO: interface and within the oxide. Oxide charges are formed by contamination of

sodium ions during processing. Surface charges are formed at the sudden termination of

the oxide layer where ionic Si has been left at the surface. The ions and uncompleted Si

bonds form a sheet of positive charge at the interface. Sodium contamination can be

controlled to a certain extent by using extremely clean materials in processing, and using

100 lattice arrangement wafers can minimize the amount surface charges at the Si-Si02

interface. The change in the behavior of MOS devices is enough that these effects need to

b>e included in the equations. These changes are accounted for by adding terms to the

existing equations for the threshold voltage and other effected parameters.

The ideal threshold voltage equation does not take into account the sheet of positive

charge at the Si-Si02 interface or the differences in the Si-poly work functions, and just

assumes that the transistor is in the flat band condition before any voltage is put on the

gate. This is not what is actually happening in the device. The equation for the flat band

voltage has to be added to the existing threshold voltage equation to obtain a more

accurate threshold voltage for the device:

where Фms is is the work function of the metal-semiconductor interface, and Qi is the

effective positive charge at the interface. The voltage required to create strong inversion

must therefore be large enough to reach the flat band condition (Фms and Qj/Ci),

accommodate the charge in the depletion region (Qd/Ci), and finally to induce the

inverted region (2Фf) [1]. This equation works for both N-type and P-type devices if

appropriate signs are included for each term. Figure 2.4 describes the appropriate signs to

use in each section of the equation for the specified type of device.

Figure 2.4. Appropriate Signs for each Component of the Threshold Voltage Equation.

All the terms in the new threshold voltage equation depend on doping except for Qi/Ci

[I]. Figure 2.5 describes how the level of doping affects the threshold voltage. As the

amount of doping increases, so does the threshold voltage. Adjusting the amount of

doping can control the level of the threshold voltage to a certain extent.

When the back gate bias changes from ground to a negative voltage, the threshold voltage

shifts in the positive direction. This is called the body effect or back gate bias effect. It

can be viewed as the change in depletion width of the reverse-biased PN junction

between the source and the substrate due to the change in the source-bulk voltage . The

threshold voltage equation must therefore be modified again to include the body

effect.

VTO is the zero-biased threshold voltage equation (equation 2.2) and y is the body effect

coefficient.

When designing circuits, the body effect coefficient should be as small as possible.

Lowering the substrate doping density and/or decreasing the thickness of the gate oxide

can both reduce the level of the body effect coefficient. In N-well CMOS technology, the

N-well doping density is much higher than that of the substrate, therefore the body effect

of the PMOS device is higher than that of the NMOS device. When scaling down

geometry in CMOS technology, the substrate doping density is increased and the gate

oxide is thinner, resulting in mixed influences in the body effect coefficient.

Short Channel Effects

Due to geometric downsizing and advanced processing technology, MOS devices with

channel lengths of much less than one micron are possible. These so-called "short

channel" devices are attractive because they reduce overall die area, can operate with less

power, and can have a lower threshold voltage. However, the shortened channel brings in

extra effects from the source and drain regions that must be taken into account.

The depletion region under the gate for a MOS device with a long channel is shaped like

a rectangle. The influence from the source and drain regions can be neglected because

they are far enough apart, and equation 2.3 for threshold voltage is accurate enough for

calculations. When this depletion channel length is reduced below a micron, the influence

of the source and drain regions must be taken into account. The trapezoidal channel shape

displayed in Figure 2.7 for an NMOS device is a direct result of the reduced proximity of

the source and drain regions to one another. The intrusion of the source and drain

depletion regions into the channel can cause punch-through current failures from drain

and source depletion regions overlapping and shorting out the channel. This will cause

the device to not respond to any gate voltage control, and just act like a short. The second

graph in Figure 2.7 depicts the channel length effect on the threshold voltage of the

NMOS device. As the length of a long channel device is decreased, the threshold voltage

stays constant until the length becomes very short. At this point, the threshold voltage

also begins to decrease.

Figure 2.7. Short Channel NMOS Transistor and Effect of Length on Threshold Voltage.

The threshold voltage equation must be altered to include these new effects:

In the equation above, Xj is the junction depth of the source/drain region, L is the length

of the depletion region, and Wd is the depth of the depletion region. This equation is only

applicable to devices with short channels of less than one micron; otherwise, the one

dimensional threshold voltage equation 2.3 is utilized. When devices are scaled down, Xj

is reduced along with a thinner gate oxide to reduce the sensitivity of the threshold

voltage to the short channel effect.

Reduced geometry of short channel devices tends to increase electric fields and cause

effects from hot carriers to appear. In an NMOS device, the field in the reverse- biased

drain junction can lead to impact ionization and carrier multiplication. The resulting holes

from carrier multiplication contribute to the substrate current and can move to the source,

causing electrons to be injected into the p-region. Bipolar NPN transistor action can result

in the source-channel-drain configuration and cause the gate to lose control of the current.

Transport of electrons through the barrier into the gate oxide is another hot electron

effect. These electrons can become trapped in the oxide and change the threshold voltage

and current-voltage characteristics of the device.

A processing method called Lightly Doped Drain (LDD) uses two doping levels to

combat the problems of the source and drain depletion regions intruding into the channel

and hot carrier effects. By heavy doping over most of the source and drain regions and

lightly doping the regions adjacent to the channel of the device, the LDD structure allows

the field between the drain and channel regions to be reduced. This reduces the ability of

hot carrier effects to occur and prevents source and drain depletion region intrusion into

the channel. This prevents punch-through current from happening.

Narrow Channel Effects

Narrow channel effects occur in CMOS devices using LOCOS isolation and width

reduction of the device below one micron. Inverse of the short channel effects, as the

width of the device decreases the threshold voltage increases. This effect is caused by the

influence of the depletion region under the edge of the field oxide surrounding the active

region, the bird's beak shape of the field oxide region around the active region, and the

channel stop implant under the field oxide surrounding the active region. This effect

forces an addition to the short channel threshold voltage equation:

where a is between 0 and L and is determined by the doping profile and topography of

the field oxide at the Si-SiO: interface surrounding the active region.

Recent technological advancements in processing have made shallow trench isolation

possible in place of LOCOS isolation. Shallow trench isolation reduces narrow channel

effects due to the elimination of the bird" s beak and the channel stop implant. Figure 2.8

compares the narrow channel effects of LOCOS isolation and shallow trench isolation on

threshold voltage shift. On devices utilizing low-voltage operation, implementation of

shallow trench isolation instead of LOCOS isolation is obviously necessary to prevent

large amounts of threshold voltage shift at very short channel widths.

Figure 2.8. Effect of LOCOS and Shallow Trench Isolation on Threshold Voltage.

Sub-Threshold Current

When an NMOS device is biased at VG < VT, its drain current is not really zero, but is

instead exponentially proportional to the gate voltage [3]. The current leaking across the

depletion region while the gate voltage is less than the threshold voltage is called sub-

threshold current. During weak inversion, the current in the depletion channel is caused

by diffusion. With a thinner gate oxide and a more lightly doped substrate, the sub-

threshold current slope is steeper. The MOS device is more attractive for low-power

applications with a certain amount of speed necessary because it turns on and off faster

and has less leakage current. Figure 2.9 displays the sub-threshold current characteristics

of an NMOS device with l0mV-drain voltage and bulk voltage plotted from OV to -4V.

Figure 2.9. Effect of Back Gate Bias on Level of Sub-threshold Current.

As the bulk voltage decreases, the threshold voltage increases and the sub-threshold

current decreases. This shows the tradeoffs between threshold voltage, sub-threshold

current, and bulk voltage.

MOS Capacitances

For MOS devices, there is a capacitance model that must be considered for AC and

transient analysis. The capacitance model consists of two intrinsic capacitances made up

of the drain-gate capacitance and the source-gate capacitance, and two extrinsic

capacitances made up of the drain-body capacitance and the source-body capacitance.

The intrinsic performance of the MOS device is most affected by the intrinsic

capacitances. The source-gate and drain-gate capacitances are active and vary as a

function of the gate-source voltage. The extrinsic capacitors act more like parasitic

capacitances, and have only secondary effects on overall device performance. Figure 2.10

displays the AC capacitance model for an NMOS device.

Figure 2.10. AC Capacitance Model for an NMOS Transistor.

IT is the transfer current which is equivalent to the drain current. The drain-body

capacitance and the source-body capacitance are parasitic capacitances between the

source/drain regions and the bulk substrate of the device. They occur because of the

space charge in the depletion region of the reverse biased PN junctions.

Low-Power/Low-Voltage Complications

As CMOS devices shrink to smaller sizes, problems arise with increased currents and

dissipation of power. When the lengths and widths of CMOS devices are reduced without

reducing threshold voltage levels or power supply voltage, current increases, packing

density of devices increases, and the amount of power a given size of die must dissipate

increases. This increased power dissipation causes an increased junction temperature and

therefore an increased junction leakage current, causing the device to use more power

than necessary.

Increased power dissipation in the die area has an adverse effect on the threshold voltage

of the CMOS devices. Threshold voltage exhibits a negative temperature coefficient,

which causes enhancement mode devices with low thresholds to become depletion mode

devices at elevated operating temperatures.

The most obvious solution to these problems is lowering of the power supply voltage. As

the power supply voltage is lowered, VGS-VTH lowers, and the drain current that is

related to VGS-VTH also lowers. Propagation delay increases, but the threshold voltage

can be reduced to minimize the effect granted that an increase in sub-threshold current

can be tolerated.

A phenomenon known as voltage bounce, related to the inductance of metal interconnect

lines on the IC, may inhibit performance of low-voltage operation. As device geometry

shrinks, the lines get smaller in diameter and the inductance per unit length increases.

When this inductance increases, the change in power supply current (dl/dt) causes the

voltage change on the lines by L(dl/dt).

The increased delay time variation associated with the change in threshold voltage after

the supply voltage is reduced is another problem limiting the reduction of supply voltage.

The propagation delay is a function of the difference in threshold voltage and supply

voltage through the following equation:

As the supply voltage is reduced, the change in the propagation delay due to the change

in the threshold voltage may increase. This reduces circuit performance substantially, and

increases the complexity of the circuit design. To reduce this effect and increase

performance stability, threshold voltage must again be scaled down with shrinking power

supply voltage.

Supply Voltage Reduction Strategy

To lower the supply voltage for CMOS devices, two strategies must be considered

depending on the necessary system application [3]. The high-performance strategy entails

lowering the supply voltage to increase system reliability including electro migration

reliability, hot carrier reliability, oxide stress reliability, and other reliabilities related to

the increased electric fields in the smaller geometry devices.

In this strategy, power supply voltage is not reduced aggressively and circuit performance

is optimized. The low-power strategy results in degraded speed and circuit performance,

but is more attractive for mobile systems in lengthening battery Hfe.

From earlier discussions on threshold voltage and gate length, the reduction of the gate

length does not automatically incur a reduced threshold voltage. Reducing the threshold

voltage can cause increases in levels of sub-threshold leakage current. This must be taken

into consideration when lowering the threshold voltage of a sub-micron device. The

minimum threshold voltage can be determined through threshold voltage variation due to

temperature effect, process fluctuation, and the on-off current ratio of the device. Figure

2.11 describes the threshold voltage versus supply voltage for various goals.

The arrows indicate which direction the supply voltage and threshold voltage should go

for a particular goal. For example, if performance is to be increased, power supply

voltage should be increased and threshold voltage should be decreased. By looking at this

graph, three goals can be optimized into a point for the specified needs of the application

- standby power, active power, and performance

Figure 2.11. Trade Offs Associated with Power Consumption and Performance for Low-

Power/Low-Voltage CMOS Design.

For the design of the Low-Power/Low-Voltage LVDS Receiver, a midpoint must be

chosen between performance and power consumption on the graph of Figure 2.11. A

decrease in the power supply voltage is desired without excessive operating frequency

loss and increased power consumption. The design must take into account all of the low

power/low-voltage trade-offs and complications discussed above, and still provide a

working LVDS receiver that is useful to industry.

OPERATION OF DIFFERENTIAL SIGNALS AND LVDS