LTE MIMO System Level Design

description

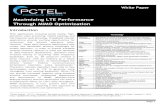

Transcript of LTE MIMO System Level Design

-

1Copyright Agilent Technologies 2009Agilent Restricted

1

LTE MIMO System-Level Design(Preliminary)

Copyright Agilent Technologies 2009Agilent Restricted

2

Agenda

MIMO OverviewMIMO Transmitter Case StudyMIMO Receiver Case StudyEarly R&D LTE Hardware Testing

-

2Copyright Agilent Technologies 2009Agilent Restricted

3Page 3

Basic channel access modesTransmitAntennas

ReceiveAntennas

SISO

The Radio Channel

MISO

Single Input Single Output

Multiple Input Single Output(Transmit diversity)

ReceiveAntennas

TransmitAntennas

MIMO

The Radio Channel

SIMO

Single Input Multiple Output(Receive diversity)

Multiple Input Multiple Output(Multiple stream)

Copyright Agilent Technologies 2009Agilent Restricted

4Page 4

Advantages of multiple antennas

MISO (Tx diversity) increases the robustness of the signal to poor channel conditions. It does not increase data rates but increases coverage and therefore cell capacity.

SIMO (Rx diversity) improves the received SNR by combining multiple copies of the same signal. Like MISO it does not increase data rates but extends coverage and hence cell capacity.

MIMO uses multiple data streams to increase cell capacity. The data streams can be allocated to one user to increase single-user data rates.

-

3Copyright Agilent Technologies 2009Agilent Restricted

5Page 5

Multiple antenna techniques

Multiple antenna techniques are fundamental to LTE and an appreciation of the different methods and their relative advantages and disadvantages is important

There are three main multi-antenna techniques used in LTE1. Transmit/receive diversity2. Spatial multiplexing

Single User MIMO (SU-MIMO) Multi-user MIMO (MU-MIMO)

3. Beamforming

Copyright Agilent Technologies 2009Agilent Restricted

6Page 6

Transmit/receive diversity

This is the same as what already exists for UMTS Transmit diversity has been specified for W-CDMA since R99. Receive

diversity was introduced in Rel-6 for HSDPA.

The same data is sent on two antennas which provides better SNRImproves performance in low SNR conditions and with fadingSimple combining is used in the receiver

eNB UE

Stream 1

Stream 1

-

4Copyright Agilent Technologies 2009Agilent Restricted

7

Single user MIMO

This is an example of downlink 2x2 single user MIMO with precoding. Two data streams are mixed (precoded) to best match the channel

conditions.The receiver reconstructs the original streams resulting in increased single-

user data rates and corresponding increase in cell capacity. 2x2 SU-MIMO is mandatory for the downlink and optional for the uplink

SU-MIMO

eNB 1 UE 1

= data stream 1

= data stream 2

Copyright Agilent Technologies 2009Agilent Restricted

8

Multiple user MIMO

UE 2

UE 1

eNB 1

MU-MIMO

Example of uplink 2x2 MU-MIMO.In multiple user MIMO the data streams come from different UE.There is no possibility to do precoding since the UE are not connected but

the wider TX antenna spacing gives better de-correlation in the channel.Cell capacity increases but not the single user data rate.The key advantage of MU-MIMO over SU-MIMO is that the cell capacity

increase can be had without the increased cost and battery drain of two UE transmitters.

MU-MIMO is more complicated to schedule than SU-MIMO

= data stream 1

= data stream 2

-

5Copyright Agilent Technologies 2009Agilent Restricted

9

SystemVue MIMO Source

Copyright Agilent Technologies 2009Agilent Restricted

10

SystemVue MIMO Channel Model

Simulated Spectrum with MIMO Fading

-

6Copyright Agilent Technologies 2009Agilent Restricted

11

SystemVue MIMO Receiver

Copyright Agilent Technologies 2009Agilent Restricted

12

Agenda

MIMO OverviewMIMO Transmitter Case StudyMIMO Receiver Case StudyEarly R&D LTE Hardware Testing

-

7Copyright Agilent Technologies 2009Agilent Restricted

13

Mixed-Signal Challenges: System Design Tradeoffs

Tx RxCodingAlgorithms

D/ABits In Decoding

Algorithms Bits Out

ChannelA/D

GainLinearityOutput Power

GainNFPhase Noise

Considerations: Key Algorithms Baseband Implementation/ Fixed-Point Effects RF Design Impairments/Non-Linearities Phase Noise, ADC Jitter Channel Impairments

FPGA HDL Code

Fixed Point Baseband Designs

Math Algorithms

Copyright Agilent Technologies 2009Agilent Restricted

14

System-Level Architecture DesignPartition Design Requirements to Meet LTE Specifications without Over-Designing

ADC and DACImpairments

RF Transmitter/PA Nonlinarities

Baseband Fixed-PointMixed-Signal

Receiver

Tx RxCodingAlgorithms

D/A

Bits In DecodingAlgorithms Bits Out

RF ChannelA/D

Coding/Decoding

Algorithms

With LTE having such high performance targets every part of the transmit and receive chain becomes critical to the link budgetSo how to decide the optimum balance, without over-designing?How are design requirements impacted going from QPSK to 16QAM to 64QAM?

-

8Copyright Agilent Technologies 2009Agilent Restricted

15

Baseband Libraries Algorithm Test Vectors for FPGA Development

(Preliminary)

Coding/Decoding

Algorithms

Copyright Agilent Technologies 2009Agilent Restricted

16

Configurable References

(Preliminary)

-

9Copyright Agilent Technologies 2009Agilent Restricted

17

Diff

FPGA HDL CoSim Output

SystemVueScrambler

Output

HDL (Actual Scrambler Code Not Shown)

Switch between C++ model and math algorithm model

FPGA Scrambler Example

(Preliminary)

Copyright Agilent Technologies 2009Agilent Restricted

18

Diff

FPGA HDL CoSim Output

SystemVueScrambler

Output

HDL (Actual Scrambler Code Not Shown)

Switch between C++ model and math algorithm model

FPGA Scrambler Example

(Preliminary)

-

10

Copyright Agilent Technologies 2009Agilent Restricted

19

Transmitter Design Start with SystemVue Pre-Configured Template

Copyright Agilent Technologies 2009Agilent Restricted

20

I in

Q in

4XUpSample

4XUpSample

FIR RRC

FIR RRC

Fs/4 Carrier Multiplexing

I(t)*CosWc(t)

Q(t)*SinWc(t)

I(t)*CosWc(t)-Q(t)*SinWc(t)

Design Fixed Point IQ Modulator andReplace Ideal IQ Modulator

Baseband Fixed-Point

-

11

Copyright Agilent Technologies 2009Agilent Restricted

21

64QAM EVM Results with FIR Wordlength =10 for Fixed Point IQ Modulator Design

EVM = 0.5 %

(Preliminary)

Copyright Agilent Technologies 2009Agilent Restricted

22

64QAM EVM Results with FIR Wordlength =8 forFixed Point IQ Modulator Design

EVM = 1.3 %

(Preliminary)

-

12

Copyright Agilent Technologies 2009Agilent Restricted

23

64QAM EVM Results with FIR Wordlength =6 & 7 for Fixed Point IQ Modulator Design

EVM = 2.9 % EVM = 46 % !

FIR Wordlength = 7 bits FIR Wordlength = 6 bits

(Preliminary)

Copyright Agilent Technologies 2009Agilent Restricted

24

Enable HDL Code Gen to Target an FPGA

-

13

Copyright Agilent Technologies 2009Agilent Restricted

25

Add RF Design: Transmitter and Antenna Cross Talk

Specify LO Phase Noise dBc/Hz @ Freq. Offset RF Transmitter/

PA Nonlinarities

Specify 1dBComp. Pt.

Copyright Agilent Technologies 2009Agilent Restricted

26

-80 dBc/Hz Phase Noise @ 10kHz with -30 dB CrossTalk

Specify Phase Noise in

dBc/Hz vs. Frequency

Offset

RS EVM = 1.3 % RS EVM = 1.3 %

QPSK 64 QAM(Preliminary)

-

14

Copyright Agilent Technologies 2009Agilent Restricted

27

-70 dBc/Hz Phase Noise @ 10kHz with -30 dB CrossTalk

Specify Phase Noise in

dBc/Hz vs. Frequency

Offset

RS EVM = 3.5 % RS EVM = 3.5 %

QPSK 64 QAM(Preliminary)

Copyright Agilent Technologies 2009Agilent Restricted

28

-60 dBc/Hz Phase Noise @ 10kHz with -30 dB CrossTalk

RS EVM = 11.2 %

QPSK

Specify Phase Noise in

dBc/Hz vs. Frequency

Offset

RS EVM = 11.2 % ,but composite EVM is 85%

64 QAM

Phase noise is introducing significant ICI , which is impacting OFDMA subcarrier orthogonality

(Preliminary)

-

15

Copyright Agilent Technologies 2009Agilent Restricted

29

LTE MIMO Downlink BER with ADI A/D Converter

MIMO SourceMIMO Receiver

Sweep SNR

ADI A/D Converter

MIMO Channel

ADC and DACImpairments

Mixed-SignalReceiver

Copyright Agilent Technologies 2009Agilent Restricted

30

QPSK BER Results with Swept ADI A/D Converter Jitter

2% Jitter

4% Jitter

6% Jitter

(Preliminary)

-

16

Copyright Agilent Technologies 2009Agilent Restricted

31

QPSK , 16QAM, 64QAM Results vs. Swept ADI ADC Jitter

QPSK 16 QAM 64 QAM

2% Jitter4% Jitter

6% Jitter

2% Jitter

4% Jitter

6% Jitter

2% Jitter4% Jitter

6% Jitter

(Preliminary)

Copyright Agilent Technologies 2009Agilent Restricted

32

QPSK , 16QAM, 64QAM Results vs. Swept LO Phase Noise

QPSK 16 QAM 64 QAM

-70 dBc/Hz

-65 dBc/Hz

-60 dBc/Hz

(Preliminary)

-

17

Copyright Agilent Technologies 2009Agilent Restricted

33

Agenda

MIMO OverviewMIMO Transmitter Case StudyMIMO Receiver Case StudyEarly R&D LTE Hardware Testing

Copyright Agilent Technologies 2009Agilent Restricted

34

Demodulator

RF IF

BasebandDe-Coding

RF/RF BER

A/DConverter

I

Q

Simulated COTS Receiver

MXG, ESGMXA, PSA

SystemVue+ VSA SW

Simulated

COTS Waveform

Step 1Download

Signal

Step 2Capture Signal

SISO Early R&D SDR Hardware Testing

-

18

Copyright Agilent Technologies 2009Agilent Restricted

35

Demodulator

RF IF

BasebandDe-Coding

RF/IF BER

A/DConverter

I

Q

MXG, ESGMXA, PSA

Simulated COTS Receiver

SystemVue+ VSA SW

Simulated

COTS Waveform

Step 1Download

Signal

Step 2Capture Signal

SISO Early R&D SDR Hardware Testing

Copyright Agilent Technologies 2009Agilent Restricted

36

Demodulator

RF IF

BasebandDe-Coding

A/DConverter

I

Q

Simulated COTS Receiver

MXG, ESG MXA with BB IQ

I Q

RF/ Analog IQ BER

SystemVue+ VSA SW

Simulated

COTS Waveform

Step 1Download

Signal

Step 2Capture Signal

SISO Early R&D SDR Hardware Testing

-

19

Copyright Agilent Technologies 2009Agilent Restricted

37

Demodulator

RF IF

BasebandDe-Coding

RF/Digital IQ BER

A/DConverter

I

Q Simulated COTS Baseband Receiver

MXG, ESG

RF/Digital IF BER

Logic Analyzers

SystemVue+ VSA SW

Simulated

COTS Waveform

Step 1Download

Signal

Step 2Capture Signal

SISO Early R&D SDR Hardware Testing

Copyright Agilent Technologies 2009Agilent Restricted

38

Picture of LTE OFDMA Mixed-Signal DUTSISO BER Test Setup

16822ALogic Analyzerwith AgilentSystemVue*

N6705ADC PowerAnalyzer

MXG(Download Signal from SystemVue)ESG(DUT Clock)

14 Bit A/D Board DUT

* Note: SystemVue does not ship with Logic Analyzer

-

20

Copyright Agilent Technologies 2009Agilent Restricted

39

LTE OFDMA SISO BER Test Setup Diagram

Trigger In

16822 Logic Analyzer withSystemVue

installed

14-Bit A/DConverter

Board (DUT)

LAN Cable

Event 1 Marker Out

Analog In

Clk In

30.72 MHzDig.Out

ESG

SVue LTE TDD/FDD Signal at 7.68 MHz IF

Download SystemVue LTE TDD/FDDSignal via LAN

SystemVueMXG

+ 3.3V + 5V

N6705A DC Power Analyzer

LAN Cable

Copyright Agilent Technologies 2009Agilent Restricted

40

LTE OFDMA SISO BER Results (TDD)

(Preliminary)

-

21

Copyright Agilent Technologies 2009Agilent Restricted

41

Automate Testing with SystemVue Math Scripting

Sweep DC Biaswith PowerSupply/Analyzer

SweepRF Poweron MXG

MXG

Power Supply/Analyzer

Sweep from: QPSK to 16 QAM to 64QAM

Logic Analyzer with SystemVue

Installed

14-BitA/D Converter

DUT

BER

(Preliminary)

Copyright Agilent Technologies 2009Agilent Restricted

42

FDD SISO BER with Swept QPSK, 16QAM, 64QAM, +5V Bias

(Preliminary)

-

22

Copyright Agilent Technologies 2009Agilent Restricted

43

http://www.agilent.com/find/eesof-lte-whitepaper

From an Agilent FPGA Developer using SystemVue:

SystemVue helped me discover a typing error in my 16QAM scrambler which was failing tests. It has saved MBD at least 3 months of development time already, and is crucial for meeting - and exceeding - our on-going development time goals.

http://cp.literature.agilent.com/litweb/pdf/5990-3671EN.pdf

New LTE Reference Vector White Paper

Copyright Agilent Technologies 2009Agilent Restricted

44

New LTE Bookwww.agilent.com/find/ltebook

-

23

Copyright Agilent Technologies 2009Agilent Restricted

45

For More Information:www.agilent.com/find/systemvue

Copyright Agilent Technologies 2009Agilent Restricted

46

For More Information:www.agilent.com/find/lte

-

24

Copyright Agilent Technologies 2009Agilent Restricted

47

Summary

Trade-off baseband and RF design impairments for system-level design requirements Evaluate fixed-point design impairments on system-level metrics such as EVM and BER; Generate HDL from fixed-point design to target FPGAs Generate LTE reference vectors to validate hand-written HDL code for FPGA implementations Perform system-level design trade-offs to minimize over-designing to meet specs (e.g. fixed point vs. LO phase noise vs. RF nonlinearities vs. ADC jitter) Combine simulation with test equipment to perform coded BER on RF/mixed-signal hardware, using simulation to provide baseband coding/decoding functionality

Copyright Agilent Technologies 2009Agilent Restricted

48

Thank You!