Linear Integrated Circuits Unit1 Raghudathesh VTU

-

Upload

raghudathesh -

Category

Documents

-

view

233 -

download

0

Transcript of Linear Integrated Circuits Unit1 Raghudathesh VTU

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

1/54

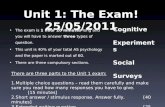

LINEAR INTEGRATED CIRCUITS (VTU) - 10EC46

UNIT - 1

Operational Amplifier Fundamentals: Basic Op-Amp circuit, Op-Amp parameters: Input &output voltage, CMRR & PSRR, offset voltages & currents, Input & output impedances, Slewrate & Frequency limitations Op-Amps as DC Amplifiers Biasing Op-Amps, Direct coupled-Voltage Followers, Non-inverting Amplifiers, Inverting amplifiers, Summing amplifiers,Difference amplifier. 7 Hours.

TEXT BOOKS:1. “Operational Amplifiers and Linear IC’s”, David A. Bell, 2nd edition, PHI/Pearson, 2004.2. “Linear Integrated Circuits”, D. Roy Choudhury and Shail B. Jain, 2nd edition, Reprint 2006,

New Age International.

Special Thanks To:Faculty: Rajappa H S (Asst Professor, ECE, GMIT)

BY:

RAGHUDATHESH G PAsst ProfECE Dept, GMIT

Davangere 577004Cell: +917411459249Mail: [email protected]

Website: raghudathesh.weebly.com

Quotes: The starting point of all achievement is desire. Every noble work is at first impossible.

A moment’s insight is sometimes worth a life’sexperience. The true secret of happiness lies in taking a genuine interest in all the details of daily life. The center of every man’s existence is a dream. Dare to live the life you have dreamed for yourself. Go forward and make your dreams come true.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 1

mailto:[email protected]:[email protected]:[email protected]:[email protected]

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

2/54

LIC: Abbreviated as L inear I ntegrated Cir cuits . Definition1: An Integrated Circuit (IC) is a miniature, low cost electronic circuit

consisting of active and passive components fabricated together on a single crystal of

silicon. The active components are transistors and diodes and passive components areresistors and capacitors.

Definition2: An Integrated Circuit (IC) , sometimes called a chip or microchip, is asemiconductor wafer on which thousands or millions of tiny resistors, capacitors, andtransistor s are fabricated. An IC can function as an amplifier, oscillator, timer, counter,computer memory, or microprocessor.

Classification: A particular IC is categorized as either linear (analog) or digital , depending on

its intended application.

Linear ICs: They have continuously variable output that depends on the input signal level

(they have infinite state changes). As the term implies, the output signal level is alinear function of the input signal level.

Ideally, when the instantaneous output is graphed against the instantaneous input,the plot appears as a straight line.

Applications: audio-frequency (AF) and radio-frequency (RF) amplifiers. Operational Amplifier (op amp) is a common device in these applications.

Digital ICs: They operate at only a few defined levels or states, rather than over a continuous

range of signal amplitudes. Applications: used in computers, computer networks, modems, and frequency

counters. The fundamental building blocks of digital ICs are logic gates , which work with binary data, that is, signals that have only two different states, called low (logic 0)and high (logic 1).

Advantages of ICs over discrete circuits:

1. Minimization & hence increased equipment density.2. Cost reduction due to batch processing.3. Increased system reliability4. Improved functional performance.5. Matched devices.6. Increased operating speeds7. Reduction in power consumption.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 2

http://searchcio-midmarket.techtarget.com/definition/microchiphttp://searchcio-midmarket.techtarget.com/definition/semiconductorhttp://searchcio-midmarket.techtarget.com/definition/transistorhttp://searchcio-midmarket.techtarget.com/definition/amplifierhttp://searchcio-midmarket.techtarget.com/definition/oscillatorhttp://searchmobilecomputing.techtarget.com/definition/memoryhttp://searchcio-midmarket.techtarget.com/definition/analoghttp://searchcio-midmarket.techtarget.com/definition/digitalhttp://searchcio-midmarket.techtarget.com/definition/digitalhttp://whatis.techtarget.com/definition/AF-audio-frequency-or-afhttp://searchnetworking.techtarget.com/definition/radio-frequencyhttp://whatis.techtarget.com/definition/logic-gate-AND-OR-XOR-NOT-NAND-NOR-and-XNORhttp://whatis.techtarget.com/definition/logic-gate-AND-OR-XOR-NOT-NAND-NOR-and-XNORhttp://searchnetworking.techtarget.com/definition/radio-frequencyhttp://whatis.techtarget.com/definition/AF-audio-frequency-or-afhttp://searchcio-midmarket.techtarget.com/definition/digitalhttp://searchcio-midmarket.techtarget.com/definition/analoghttp://searchmobilecomputing.techtarget.com/definition/memoryhttp://searchcio-midmarket.techtarget.com/definition/oscillatorhttp://searchcio-midmarket.techtarget.com/definition/amplifierhttp://searchcio-midmarket.techtarget.com/definition/transistorhttp://searchcio-midmarket.techtarget.com/definition/semiconductorhttp://searchcio-midmarket.techtarget.com/definition/microchip

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

3/54

Operational Amplifier: Definition: An Operational Amplifier, or op-amp for short, is fundamentally a voltage

amplifying device are having very high gain integrated circuit amplifiers which is basically a three-terminal device consists of two high impedance inputs, one called the

Inverting Input, marked with a negative sign, ( - ) and the other one called the Non-inverting Input, marked with a positive sign ( + ). The third terminal having lowimpedance represents the output which can both sink and source either a voltage or acurrent.

The inputs are identified as non-inverting input and inverting input because of the way inwhich they affect the output voltage.

The basic circuit of an operational amplifier consists of a differential amplifier inputstage and an emitter - follower output stage.

The term OP-AMP is used to denote an amplifier which can be configured to performvarious operations like amplification, subtraction, differentiation, addition, integrationetc.

Circuit Symbol and Terminals:

Figure 1.1 Circuit and IC symbol for an operational amplifier (op-amp)

Figure 1.1 shows there are two input terminals, one output, and two supply terminals. The two input terminals of the operational amplifier are designated inverting input

(identified with a minus sign) and non-inverting input (plus sign).

Input signal at the inverting input terminal produces an inverted output (Phase), and anyinput to the non-inverting terminal generates a non-inverted output (Phase).

The supply terminals are identified as + V CC (the positive supply terminal) and V EE thenegative supply terminal). Typical supply voltages for operational amplifiers range from±9 V to ±22 V.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 3

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

4/54

Characteristics of Ideal OPAMP:1. Voltage Gain is infinite (A V = ∞) 2. Open loop gain is infinite3. Input impedance is infinite (R i = ∞)

4. Output impedance zero (R o = 0)5. Bandwidth is infinite ( BW = ∞) 6. Gain Independent of Frequency7. Zero input voltage offset, i.e., V o = 0 when V 1 = V 2 8. Zero power supply rejection ratio ( PSRR =0) i.e. output voltage is zero when power

supply V CC = 09. No change in the characteristic feature with change in temperature10. Infinite Common mode rejection ratio (CMRR = ∞) 11. Infinite slew rate (S = ∞)

Packaging: Some typical operational amplifier packages are illustrated in Fig. 1.2.

Figure 1.2: Opamp Packages

The plastic dual-in-line (DIP) package in Fig. 1.2(a) has eight terminals, only five ofwhich are normally used for a basic operational amplifier.

The TO-5 metal can-type package shown in Fig. 1.2(b) also uses only five of its eightterminals.

As with other semi-conductor devices, a metal can package can normally dissipate moreheat than a plastic container.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 4

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

5/54

But DIP packages are usually the least expensive and they can be more compact thanmetal can containers.

Block Diagram Representation of Op-amp:

Op-amps are available in an integrated circuit form. Commercial integrated circuit op-amps usually consist of four cascaded blocks.

The block diagram of IC op-amp is shown in the Figure 1.3 below

Figure 1.3: Internal block schematic of an op-amp

Input Stage: The input stage requires:

High input impedance to avoid loading on the sources. It requires two input terminals. It also requires low output impedance.

All such requirements are achieved by using the dual input, balanced outputdifferential amplifier as the input stage.

The function of a differential amplifier is to amplify the difference between thetwo input signals. The differential amplifier has high input impedance. This stage

provides most of the voltage gain of the amplifier.

Intermediate Stage: The output of the input stage drives the next stage which is an intermediate stage.

This is another differential amplifier with dual input, unbalanced i.e. single endedoutput.

The overall gain requirement of the op-amp is very high. The input stage alonecannot provide such a high gain.

The main function of the intermediate stage is to provide an additional voltagegain required.

Practically, the intermediate stage is not a single amplifier but the chain ofcascaded amplifiers called multistage amplifiers.

Level Shifting Stage: All the stages are directly coupled to each other.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 5

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

6/54

As the op-amp amplifies DC signals also, the coupling capacitors are not used tocascade the stages.

Hence the DC. quiescent voltage level of previous stage gets applied as the inputto the next stage. Hence stage by stage DC. level increases well above ground

potential. Such a high DC voltage level may drive the transistors into saturation. This further may cause distortion in the output due to clipping. This may limit the

maximum AC output voltage swing without any distortion. Hence before the output stage, it is necessary to bring such a high DC voltage

level to zero volts with respect to ground. The level shifter stage brings the DClevel down to ground potential, when no signal is applied at the input terminals.

Then the signal is given to the last stage which is the output stage. The buffer is usually an emitter follower whose input impedance is very high.

This prevents loading of the high gain stage.

Output Stage: The basic requirements of an output stage are low output impedance, large a.c.

output voltage swing and high current sourcing and sinking capability. The push-pull complementary amplifier meets all these requirements and hence

used as an output stage. This stage increases the output voltage swing and keeps the voltage swing

symmetrical with respect to ground. The stage raises the current supplying capability of the op-amp.

Overall block diagram is as shown below

Figure 1.4: Op-amp Internal Architecture

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 6

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

7/54

Basic Operational Amplifier Circuit : The basic circuit of an operational amplifier is shown in the figure 1.5 below

Figure 1.5: The basic circuit of an operational amplifier has a differential amplifier input stage and an emitter follower output

The circuit is provided with a +V CC and – VEE supply voltages, and the two inputterminals are grounded.

Transistors Q 1 and Q 2 constitute a differential amplifier, which produces a voltage changeat the collector of Q 2 when a difference input voltage is applied to the bases of Q 1 and Q 2.

Transistor Q 3 operates as an emitter-follower to provide low output impedance. The DC output voltage level at the emitter of Q 3 is obtained by applying KVL to the loop

+VCC, RC, Q 3, base of Q 3 and output.

------- (1)

Assume that Q 1 and Q 2 are matched transistors, that is they have equal V BE levels andequal current gains.

Then, with both transistor bases at ground level, the emitter currents are equal, and bothIEl and I E2 flow through the common emitter resistor, R E. Thus, total emitter current could

be calculated as

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 7

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

8/54

Appling KVL to the loop from base of transistor Q 2, R E and – V EE supply we get,

--------- (2)

Given that Vcc = +10 V, V EE = - 10 V, R E = 4.7 kΩ, R C = 6.8 kΩ, and all transistors have

VBE = 0.7 V.Scenario1: With both input terminals at ground level we shall find the output voltage

Hence, Also,

Substituting I C2 in equation (1) we get,

Scenario2: A positive-going voltage is applied to the non-inverting input terminal andinverting input terminal is grounded.

When a positive-going voltage is applied to the non-inverting input terminal, Q 1 base is

pulled up by the input voltage, and its emitter terminal tends to follow the input signal. Since Q 1 and Q 2 emitters are connected together, the emitter of Q 2 is also pulled up by the

positive-going signal at the non-inverting input terminal.

The base voltage of Q 2 is fixed at ground level so the positive-going movement at itsemitter causes a reduction in its base-emitter voltage (V BE2). The result of the reduction in

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 8

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

9/54

VBE2 is that its emitter current is reduced and consequently its collector current isreduced.

Let, the positive-going input at the base of Q 1 reduces I C2 by 0.2 mA (1.0 to 0.8 mA).This gives a new level of output voltage as,

Conclusion: The output voltage has changed from +2.5 V to +3.9 V, a change of +1.4 V. It isseen that a +ve going signal at the non-inverting input terminal has produced a positive-going

output voltage.

Scenario3: A positive-going voltage is applied to the inverting input terminal and non-inverting input terminal is grounded.

Here, Q 2 base is pulled up, the base-emitter voltage of Q 2 is increased, and that of Q 1 isreduced by a similar amount. This results in an increase in I E2 and a consequent increasein IC2.

Let us assume that a 0.2 mA change occurs in I C2 . Thus, I C2 is increased from 1 mA to 1.2mA by the positive-going voltage at the inverting input terminal. The output voltage cannow be calculated as

Conclusion: The output voltage has now changed from its original level of +2.5 V to +1.1V, achange of -1.4 V. Therefore, the positive-going signal at the inverting input terminal produced anegative-going voltage change at the output.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 9

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

10/54

A Basic Operational Amplifier Circuit Consists:1. A differential amplifier stage with two (inverting and non-inverting) input terminals

and2. A voltage follower output stage.

The differential amplifier offers high impedance at both input terminals and it producesvoltage gain.

The output stage gives the op-amp low output impedance. A practical operational amplifier circuit is much more complex than the basic circuit.

Input Voltage Range: The maximum positive going and negative going input voltage that is applied to an Op-

Amp is termed as its input voltage range.

Ex: For Op-Amp 741 typical input range is ±13V when using a ±15V supply.

Output Voltage Range: The maximum output voltage swing is limited by the input voltage range.

The op-amp is connected to function as either a non-inverting or inverting amplifier; theoutput voltage may be much larger than the input.

Just how far the output voltage can swing in positive or negative direction depends on thesupply voltage and the op-amp output circuitry.

A rough approximation for most operational amplifiers is that the maximum output

voltage swing is approximately equal to 1 V less than the supply voltage. For the 741 op-amp with a supply of ±15 V, the data sheet lists the output voltage swing

as typically ±14 V when R L ≥ 10 kΩ.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 10

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

11/54

Common Mode Rejection Ratio:

Figure 1.6: Basic op-amp circuit with the two input terminals connected together, and a common mode input voltage applied.

Common Rejection Ratio (CMRR) is defined as the ability of Op-Amp in rejectingcommon mode inputs. CMRR is also defines as the ratio of the open-loop gain M to thecommon mode gain A cm.

CMRR expressed in decibels as,

The common mode voltage gain ‘Acm’ is defined as the ratio of change in the outpvoltage to the change in common mode input voltage.

From the figure 1.6 we see that the two input terminals are connected together and bothare raised to 1V above ground level. This is known as a common mode input.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 11

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

12/54

Here we see that there is no differential input; both input terminals are at the same potential. So ideally the output should be zero.

As the base voltages of Q 1 and Q 2 are raised to 1V above ground, the voltage drop acrossemitter resistor R E is increased by 1V, and, consequently, I C1, and I C2 are increased.

The increased level of I C2 produces an increased voltage drop across resistor R C, whichresults in a change in the output voltage at the emitter of Q 3.

Similarly, if a -1V common mode input is applied, I C2 falls, and again a change is produced at the circuit output.

The effect of op-amp common mode gain is modified by feedback. Consider the non-inverting amplifier circuit in Figure 1.7.

Figure 1.7: A common mode input voltage appears at both i nput terminals of a non-inverting opamp

The output voltage is given by,

Any output voltage will produce a feedback voltage across resistor R 2, which results in adifferential voltage at the op-amp input terminals.

The differential input produces an output which tends to cancel the output voltage thatcaused the feedback. The differential input voltage required to cancel V o(cm) is,

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 12

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

13/54

Vd is also the feedback voltage developed across R 2 hence,

Hence,

Here,

Power Supply Voltage Rejection: For a basic op-amp circuit a variation in -V EE could have essentially the same effect as an

input voltage change. Hence, variations in V CC and V EE do produce some changes at theoutput.

The power supply rejection ratio (PSRR) is a measure of how effective the operationalamplifier is in dealing with variations in supply voltage.

Ideally, the output voltage should not vary with variations in the power supply voltage.

If a variation of 1V in V CC or V EE causes the output to change by 1V, then the supplyvoltage rejection ratio is 1V per volt (1V/V).

If the output changes by 10 mV when one of the supply lines changes by 1V, then thesupply rejection ratio is 10mV/V.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 13

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

14/54

For the 741 operational amplifier, the supply voltage rejection ratio is specified astypically 30µV/V.

Input Offset Voltage:

Definition1: Input offset voltage is the amount of input voltage that should beapplied between two input terminals of an op-amp in order to force the output voltageto zero.

The origin of input offset voltage is due to the mismatch between the transistors ofthe input stage of the op-amp i.e, V BE1 ≠ V BE2

Definition2: Output offset voltage is a DC voltage present at the output terminal ofan op-amp when both the input terminals are grounded.

Consider a internal circuit of op-amp voltage follower circuit as shown below

Figure 1.8: internal circuit of op-amp voltage follower c ircuit

For the output voltage to be exactly equal to the input, the transistor Q 1 and Q 2 must be perfectly matched.

Determining the output voltage by applying KVL to V i, V BE1 , VBE2 and output V 0.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 14

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

15/54

Scenario1: Say both transistors are matched V BE1 = V BE2 and V i = 0 Output is given as

Scenario2: Say both transistors are not perfectly matched hence V BE1 = 0.7V andVBE2 = 0.6 V and V i = 0

Output is given as

The above unwanted output voltage is known as an output offset voltage. To set the output voltage to ground level, the input would have to be raised/increased

to +0.1 V. This is termed an input offset voltage (V os).

Typical input offset voltage for 741 op-amp is 1 mV.

Input offset Current (I os): Definition: The algebraic difference between two input currents flowing into the two

input terminals of an op-amp.

Input transistors of an operational amplifier not being perfectly matched that is, thetransistor base-emitter voltages being unequal, the current gain (h FE) of one transistormay not be exactly equal to that of the other.

Thus, when both transistors have equal levels of collector current, the base current in onemight be 1µA while the other has a base current of 1.2 µA.

The difference these two input current levels is known as the input offset current (I os). When an operational amplifier is connected as a simple voltage follower the input offset

current has no effect. But some circuits have two equal-value resisistors in series with theinput terminals and in this case, the input offset current produces unequal voltage dropsacross these resistors as shown in figure 1.9 below.

V

V

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 15

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

16/54

Figure 1.9: Input offset current

The difference in the resistor voltage drops behaves as a differential input voltage which produces an output offset voltage.

The typical input offset current for the 741 operational amplifier is 20 nA.

Input Bias Current: Definition: the average of the two input currents, flowing into the op-amp terminals is

called as input bias current.

Figure1.10: Input Bias Current

For 741 op-amp, maximum value of input bias current is 500 nA.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 16

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

17/54

Offset Nulling: There are two method for nulling input offset voltage and current which is discussed

below

Method1:

Figure 1.11: Potentiometer method

A variable resistance introduces between the emitters of Q 1 and Q 2 can minimizethe effect of offset voltage and currents.

The variable resistance RP is a low resistance Potentiometer which changes thevoltage drop from base of each transistor to the common point of Potentiometer.

Thus, input current also gets altered. Because an offset voltage is produces by the input offset current, this adjustment

can null the effects of both input offset current and input offset voltage. Method2:

Figure 1.12: manufacturer's recommended method of offset nulling for the741

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 17

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

18/54

A 10 kΩ potentiometer is connected to offset nulling terminals 1 and 5contact is connected to the negative supply line as shown in figure 1.12.

The potentiometer is adjusted to null the output offset zero. Thus nulling bothinput offset current and input offset voltage.

Resistor Tolerance Effect: The discussions of offset voltages and currents assumed that either there were no resistors

at the op-amp input terminals, or else that exactly equal resistors were connected to theinput terminal.

Most operational amplifier circuits have resistors at their input terminals and sometimesthose resistors may not have equal resistance values.

Input offset voltage due to the input offset current is,

Output voltage is given as

Resistor tolerance is,

Input offset voltage is given as,

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 18

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

19/54

Input Impedance: For all linear applications, some form of negative feed-back is provided by externally

connected components.

From negative feedback theory the impedance at the op-amp input terminal becomes

Here, Zi = the op-amp input impedance without negative feedback M = op-amp open-loop gain β = feedback factor = 1 for a voltage follower

Note the above equation applies to a non-inverting amplifier, it does not apply to aninverting amplifier.

The impedance of signal sources connected at the input of an operational amplifier circuitas shown in figure 1.13 below should be very much smaller than the amplifier inputimpedance to avoid a loss of signal across R S.

Figure 1.13: Op-Amp Input & output Impedance

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 19

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

20/54

Output Impedance: The typical output resistance specified for the 741 op- amp is 75Ω. Any stray capacitance

in parallel with this is certain to have a much larger reactance than 75 Ω. Like the input impedance, the output impedance of the op-amp is affected by negative

feedback.

Here, Zo = op-amp output impedance without negative feedback M = op-amp open-loop gain

β= feedback factor Load impedances connected at the output of an operational amplifier should be larger

than the circuit output impedance as shown in Figure 1.13. This is to avoid anysignificant loss of output as a voltage drop across Zout.

Slew Rate: The slew rate (S) of an operational amplifier is the maximum rate at which the output

voltage can change.

When the slew rate is too slow for the input, it results in distortion.

Consider the figure 1.14 shown below where a sine wave is applied as input to a voltagefollower produces a triangular waveform as output. The triangular wave results because

the op-amp output simply cannot move fast enough to follow the sine wave input.

Figure 1.14: Slew rate

Expression for slew rate is given as below,

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 20

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

21/54

Here, t = minimum time required for satisfactory operation of op-amp ΔV0 = output voltage change S = slew rate in V/µs

The typical slew rate of the 741 op-amp is specified as 0.5 V per microsecond. Thismeans that 1µs is required for the output to change by 0.5 V.

Frequency Limitations: Figure 1.15 below shows the graph of the open-loop gain (M) plotted versus frequency

for a 741 operational amplifier.

Figure 1.15: Graph of Signal frequency v/s open-loop gain

It can be seen that M is 100 dB when the signal frequency is 1 Hz. At 10 Hz the gain hasfallen below 100 dB, and M continues to fall as the signal frequency increases.

Note that frequency is plotted to a logarithmic base that M falls linearly as f increaseslogarithmically.

M falls by 20 dB when f increases from 100 Hz to 1 kHz. The ten times increases infrequency is termed a decade. So, the rate of fall of the gain is said to be 20 dB per

decade. From figure 1.12 we see that M falls to zero at approximately 800 kHz. Where an internal

gain equal to or greater that 80 dB is required for a particular application, it is availablewith a 741 only for signal frequencies up to approximately 100 Hz.

An internal gain greater than 20 dB is possible for signal frequencies up approximately90 kHz. Other operational amplifiers maintain substantial internal off frequencies thanthe 741.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 21

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

22/54

Bias Current Paths: Operational amplifiers must be correctly biased if they are to function properly.

The inputs of most operational amplifiers are the base terminals of the transistors in adifferential amplifier. Base currents must flow into these terminals for the transistors to

be operational. Hence, the input terminals must be directly connected to suitable DC bias voltage

sources.

For many applications, the most appropriate DC bias voltage level for the op amp inputterminals is approximately halfway between the positive and negat ive supply voltages.

One of the two input terminals is usually connected in some way to the op-amp output tofacilitate negative feedback.

The other input might be biased directly to ground via a signal source as shown in figure1.16 below.

Figure 1.16: Directly Connected Voltage Follower

Base current I B1 flows into the op-amp via the signal source while I B2 flows from theoutput terminal as illustrated above.

Figure 1.17 shows a situation in which resistor R 1 is included in series with the invertingterminal to match signal source resistance R s in series with the non-inverting terminal.The op-amp input currents produce voltage drops I B1R s and I B2R 1 across the resistors.

R s and R 1 should be selected as equal resistors so that the resistor voltage drops areapproximately equal. Any difference in these voltage drops will have the same effect asan input offset voltage.

Figure 1.17: R 1 included to march Rs

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 22

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

23/54

Maximum Bias Resistor Values: If very small resistance values are selected for R s and R 1 in the circuit in figure 1.17 the

voltage drops across them will be small.

On the other hand, if R s and R 1 are very large, the voltage drops I B1R S and I B2R 1, might

be several volts. For good bias stability, the maximum voltage drop across these resistors should be much

smaller than the typical forward-biased V BE level for the op-amp input transistors.Usually, the resistor voltage drop is made at least ten times smaller than V BE.

For 741 op-amp I B(max) = 500 nA.

Hence

This is a maximum value for the bias resistors for a 741 operational amplifier. For other op-amps are involved, R (max) should be calculated using the specified I B(max) for

that particular op-amp. the general expression is given as,

Potential Divider Bias:

Figure 1.18: Potential Divider Using Op-Amp

Figure 1.18 shows a potential divider (R 1 and R 2) circuitry is employed to derive aterminal bias voltage from the supply voltages.

Potential divider bias is commonly used with op-amps and in transistor circuitry.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 23

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

24/54

The potential divider current (I 2) should be much larger than the op-amp maximum input bias current. This is to ensure that I B, and any bias current variation, has a negligibleeffect upon the bias voltage level.

Usually I 2 is made 100 or more times I B. Thus,

For 741 op-amp typical value of I B(max) is 500 nA thus,

The above is the minimum value of I B when using a 741 and it would be quite

satisfactory to use a current of 1 mA.

The input voltage range is minimum of ±12 V for a 741 op amp with a ±15 V supply. The resistance "seen" when "looking out" of the non-inverting input terminal in figure

1.18 is R 1║R 2. To equalize the voltage drops at the input terminals,

Single Polarity Supply Voltage:

A single polarity supply voltage can be employed with an operational amplifier. A 741 could use a +30 V supply as illustrated in figure 1.19 below.

Figure 1.19: op-amp with single polarity

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 24

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

25/54

In this case the input terminal bias voltage should be approximately half the supplyvoltage (+ 15 V for a 30 V supply).

Alternatively, V B might be within the input voltage range (± 12 V for a 741 using a ± 15V supply) of the half-way point between + V cc and ground. Since the circuit shown in

figure 1.19 is a voltage follower, the dc output voltage will be equal to the bias voltagelevel.

Biasing BIFET Op-Amps: BIFET Op-amps are operational amplifiers with FET input stages is shown in figure 1.20

below.

Figure 1.20: Op-amp with FET input Stage

BIFET draw very low levels of input bias current like, 50 pA is not unusual. In this case, the usual design approach of selecting resistor currents one hundred times

IB(max) would result in very high resistor values which are undesirable for several reasons.1. When the bias resistors at the gate terminal of a FET are extremely large, a charge

can accumulate at the gate and this might take a relatively long time to discharge.2. Thus, the gate voltage would not be a stable quantity, and the op-amp biasconditions would be uncertain.

3. Another reason for avoiding high resistance values with any op-amp circuit is thatstray capacitance becomes more effective as resistance values increase, possiblyresulting in unwanted circuit oscillations.

For satisfactory bias conditions when using BIFET op-amps, the resistance "seen" when"looking out" of either input terminal should normally not exceed 1 MΩ.

A reasonable rule-of-thumb is to first select the largest resistor in a bias network as 1

MΩ, then calculate the other resistors accordingly. There are some op-amps which can operate with even larger resistors, notably the LM108

(not a BIFET op-amp) which can use signal source resistors as hig h as 10 MΩ.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 25

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

26/54

Concept of Virtual Ground: An Op-Amp has a very high gain typically order of 10 5. If power supply voltage V cc = 15V, then maximum input voltage which can be applied is

Here A d = Differential Gain. Let say supply voltage be 15 V and gain be 10 5 then,

i.e. Op-Amp can work as a linear amplifier (from +V i to – V i) if input voltage is less than15 µV. Above that Op-Amp saturates as shown in figure 1.21 below

Figure 1.21: Op-amp input & Output relation

Consider the Op-amp circuit as shown below,

Figure 1.22: Op-amp Circuit

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 26

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

27/54

Say if V 1 is grounded then V 2 cannot be more than 150 µV as supply voltage is +15 V,which is very very small and close to ground.

Therefore V 2 can also be considered at ground if V 1 is at ground. Physically V 2 is notconnected to the ground yet we considered V 2 at ground that is called virtual ground.

Direct-Coupled Voltage Followers: A voltage follower also called a unity-gain amplifier, a buffer amplifier, and an isolation

amplifier is a op-amp circuit which has a voltage gain of 1.

This means that the op amp does not provide any amplification to the signal. The reasonit is called a voltage follower is because the output voltage directly follows the inputvoltage, meaning the output voltage is the same as the input voltage.

This is the reason voltage followers are used. They draw very little current, not disturbingthe original circuit, and give the same voltage signal as output. They act as isolation

buffers, isolating a circuit so that the power of the circuit is disturbed very little.

Voltage followers are important to buffer or isolate a low impedance load from a voltagesource. This means that rather than connect a relatively low value of load resistanceacross the terminals of the power source, the op amp can be used to eliminate any loadingthat might occur. Thus, the power source will not be loaded down. The circuit acts as anideal voltage source with nearly zero internal impedance, since it barely uses any current,yet outputs the full voltage.

Design: An operational amplifier may be function as a voltage follower with the use of any

external components connected to it as in figure 1.23 below.

Figure 1.23: Op-amp voltage follower

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 27

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

28/54

In the above circuit the resistor R 1 is commonly used between output and invertingterminal to match the source resistance Rs.

Say the maximum values of base currents I B1 and I B2 may be I B1(max) and I B2(max) forthe case of perfect matching then,

------ (1) The above will be the maximum voltage drop across each resistors. Since I B1(max) and I B2(max) are same for op-amp hence R s and R 1 will be practically

same. Hence, input offset voltage is given by

------- (2) Performance:

The input impedance of the voltage follower is given as below

The output impedances of the voltage follower is given as below

The voltage follower has very high input impedance and very low output impedancehence it used to convert a very high input impedance source to low output impedanceacting as buffer.

Consider a load resistance connected to the source as shown in figure 1.24(a) below

Figure 1.24(a): Load connected directly to source

The load voltage is given as below,

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 28

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

29/54

Consider a load resistance connected to the source as shown in figure 1.24(b) below

Figure 1.24(a): Load connected using Voltage Follower

Now we know that input impedance (Z in) of op-amp is very large hence input voltageto op-amp is given as below,

Also we know that output impedances (Z out) of the voltage follower is very low,output voltage across the load is given as,

And output voltage V o is given as,

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 29

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

30/54

Due to large open loop gain M, V o = V i and due to very low output impedance V L = V o. Hence load voltage is same as the output voltage which is equal to input voltage.

Voltage Follower Using a Potential Divider Bias:

Figure 1.25 below illustrates the use of a voltage follower with a potential divider produce a low impedance dc voltage source.

Figure 1.25: Potential Divider Bias for Op-amp

In reality a potential divider is used to obtain the voltage required from supply voltage asshown in figure 1.26 below

Figure 1.26: potential divider

In the above circuit various electrical parameters is given below,

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 30

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

31/54

-------- (1)

------- (2)

------- (3)

-------- (4)

Say in above case when R L varies by a small amount I L change due to the change in V L then

The above draw back can be eliminated by using voltage follower to generate constantvoltage across the load as shown below

Figure 1.27: Voltage follower with potential divider

Due to very high input impedance and very low output impedance, if R L changes, theload voltage V L is same as V 2 which does not dependant on R L.

Due to above reasons load voltage remains constant irrespective of change in R L. Parameters with Op-amp is as below

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 31

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

32/54

When R L Changes by say 10% also, V L = V 2

Comparison of Emitter Follower and Voltage Follower:

Sl No Emitter Follower Voltage Follower

1

2 Also called as buffer amplifiers Also called as buffer amplifiers

3 Higher Input Impedance butless than Voltage Follower

Higher Input ImpedanceCompared to Emitter Follower

4 output impedance greater thanvoltage follower

Lower output impedance muchlower than emitter follower

5 AC signal voltage loss is morethan voltage follower

AC signal voltage loss is veryless compared to emitterfollower

6 DC loss is the voltage drop ofthe transistor

DC loss is Vi/M which is verysmall

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 32

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

33/54

Direct Coupled Non-inverting Amplifier: Figure 1.28 below shows the circuit for direct coupled non-inverting amplifier

Figure 1.28: Direct Coupled Noninverting Amplifier Configurations

The closed loop voltage gain of the non-inverting amplifier is Input and output voltages are given as,

The closed loop voltage gain is given as,

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 33

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

34/54

Design Steps:1. From Potential divider logic the resistor values R 2 and R 3 are determined using V i,

Vo, I 2. By convention we select I 2 much larger than I B(max) by about 100 times.

2. From the concept of virtual ground, V i = V A = V B thus

3. As V o appears across (R 2 + R 3) hence,

4. To equalize the voltage drop due to bias current I B at each input terminal,

5. If R 1 is not very large compared to R S then,

6. In case of BIFET op-amp, R 2 is selected as 1MΩ, a large value.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 34

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

35/54

Input and Out Impedance of Direct Coupled Non-Inverting Amplifier: Consider the circuit as shown below

Figure 1.29: Impedance circuit of direct coupled non-inverting amplifier

The input impedance of an op-amp circuit is given as,

------ (1)

Here, Zi = the op-amp input impedance without negative feedback M = op-amp open-loop gain

β = feedback factor For non-inverting amplifier the feedback factor is given as

------ (2)

Here A v = closed loop voltage gain of the non-inverting amplifier Substituting (2) in (1) we get

------ (3)

The input impedance given by equation (3) is the impedance "seen" when "looking into"the non-inverting input terminal; it does not include R1. Thus, the impedance seen fromthe signal source is

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 35

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

36/54

------- (4) Output impedance of an op-amp circuit as

Here, Zo = op-amp output impedance without negative feedback M = op-amp open-loop gain

β= feedback factor As β = 1/Av above equation is written as,

Direct Coupled Inverting Amplifier: The inverting amplifier circuit is as shown in the figure 1.30 below

Figure 1.30: The Op-amp inverting amplifier circuit using BJT

Input and output voltages are given as,

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 36

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

37/54

The closed loop voltage gain is given as,

Design Steps: From Potential divider logic the resistor values R 2 and R 3 are determined using V i,

Vo, I 1. By convention we select I 1 much larger than I B(max) by about 100 times.

------ (1)

To equalize the voltage drop due to bias current I B at each input terminal,

If R 1 is not very large compared to R S then,

From the concept of virtual ground,

As V o appears across (R 2) hence,

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 37

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

38/54

Direct Coupled Inverting Amplifier Using LF353:

Figure 1.30: The Op-amp inverting amplifier circuit using BJT

In case of BIFET op-amp, R 2 is selected as 1MΩ, a large value. The closed loop voltage gain of the circuit is given as,

Resistance R1 is given as

To equalize the voltage drop due to bias current I B at each input terminal,

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 38

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

39/54

Input and Out Impedance of Direct Coupled Inverting Amplifier: Consider the circuit as shown below

Figure 1.29: Impedance circuit of direct coupled inverting amplifier(add)

From the above circuit we see that the op-amp inverting terminal will be at ground level.

Hence the junctions of R 1 and R 2 will always be close to ground potential. Thus by looking into the inverting amplifier from the signal source, the resistance R 1 is

seen with its other end at ground level thus,

------- (1) Output impedance of an op-amp circuit as

------ (2)

Here, Zo = op-amp output impedance without negative feedback M = op-amp open-loop gain

β= feedback factor For non-inverting amplifier the feedback factor is given as

------ (3)

Substituting (2) in (1) we get

------- (4)

When R 2 >> R 1 then

------ (5)

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 39

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

40/54

Inverting Summing Circuits: Figure 1.30 shows the Inverting Summing Circuit

Figure 1.30: Inverting Summing Circuit

Applying KCL to node A,

------ (1)

From the concept of virtual ground at node A, V i = 0 and i = 0, hence,

Say if R 1 = R 2 then,

------- (2)

For summing amplifiers voltage gain A v is given as

------ (3)

Put (3) in (2)

-------- (4)

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 40

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

41/54

Case1: R 1 = R 2 = R 3, then

In such cases output is the direct sum of the input voltages inverted. Case2: R 3 > R 1 and R 2 then,

Output voltage is given as

The circuit output voltage is now the sum of the input voltages multiplies by R3/R1.

Case3: R 3 < R 1 and R 2 then,

Output voltage is given as

The circuit output voltage is now the sum of the input voltages multiplies by R 1/R 3. Now let us consider a 3 inputs to a summing circuit as shown in figure 1.31 below

Figure 1.31: Op-amp summing circuit with 3 input

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 41

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

42/54

The output voltage is given as,

Case1: R 1 = R 2 = R 3, then

Case2: R 1 = R 2 = R 3 and R 4 = R 1/3, output voltage is given as

Above equation shows that output voltage is a average of the inputs. Hence, summingamplifier can be designed as averaging circuit.

Application: Audio Mixers.

Difference Amplifier or Subtractor: The op-amp circuit which amplifies the difference between two of its input is known as

Difference Amplifier or Subtractor. In open loop mode, the op-amp acts as difference amplifier but due to its large open-loop

gain the output will be saturated thus; practical circuits do use negative feedback.

Figure 1.32 shows the op-amp configured as a difference amplifier.

Figure 1.32: op-amp configured as a difference amplifier

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 42

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

43/54

We employ superposition theorem to solve the circuit Case1: let V 1 be operational and V 2 be grounded. Output be represented as V o1 as shown

in figure 1.33 below

Figure 1.33: op-amp configured as a difference amplifier with V 1 Operational

Looking in to the above figure we see that it is a inverting amplifier configuration, hencegain is given as

------ (1)

The output voltage is given as

--------- (2)

Case2: let V 2 be operational and V 1 be grounded. Output be represented as V o2 as shownin figure 1.34 below

Figure 1.34: op-amp configured as a difference amplifier with V 2 Operational

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 43

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

44/54

Looking in to the above figure we see that it is a non-inverting amplifier configuration,hence gain is given as

------ (3)

The output voltage is given as

The voltage V A is given by Ohms law as,

Substituting V A in V o2 we get,

------- (4) Adding both the outputs we get,

------- (5)

Now Say we select the resistances R 1 = R 3 and R 2 = R 4 in such case above equation isreduced to,

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 44

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

45/54

-------- (6)

Now say if R 2 = R 1 in this case the output is the difference value of 2 input voltages.

Input Resistances: Two Types:

Differential Input Resistance (R i(diff) ): It is the resistance offered to an input signal source which is directly connected across

the input terminal and is given as,

Figure 1.35: Differential Input Resistance

Common Mode Input Resistance (R i(cm) ):

It is the resistance offered to an input signal source which is connected betweenground and both the input terminals and is given as,

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 45

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

46/54

Figure 1.35: Common Mode Input Resistance

Effect of Common Mode Voltage:

Say V c, is the common voltage which gets applied to both the input terminals. Hence input 1 becomes V 1 + V c, while input 2 becomes V 2 + V c. But the output is

amplified difference of (V 1 + V c) and (V 2 + V c).

Thus V c, gets cancelled and has no effect on the output. But this is true if the ratio R 4/R 3 is perfectly matched with R 2/R 1.

If these ratios are unequal then V c, at one input gets amplified more than that at the otherinput. Hence V c will not get cancelled and output will get disturbed.

Practically it is impossible to match these ratios perfectly and some common modevoltage is bound to be present.

To nullify the effect of common mode voltage, the resistor R 4 is selected as thecombination of fixed and variable resistor.

Hence adjusting variable part of R 4, the ratio R 4/R 3 is made almost equal to R 2/R 1. Thus

common mode voltage is nulled. This is shown in the figure 1.36.

Figure 1.36: Practical Adjustments for difference amplifier

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 46

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

47/54

Output Level Shifting:

In the figure 1.36 R 4 is connected to a DC bias voltage V B instead of being grounded inthe usual manner.

Now let both the input voltages V 1 and V 2 be grounded and modified circuit is as shown

in figure 1.37 below

Figure 1.37: Effect of V B

Voltage at point A is given as,

------- (1)

But Current I in the circuit given by applying KVL to the circuit,

------ (2) Substituting (2) in (1) we get,

------- (3)

Since the circuit is behaving as non-inverting amplifier hence the output voltage is givenas,

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 47

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

48/54

Using resister relationship i.e, R 2/R 1 = R 4/R 3 to nullify the common mode voltage, we get

Circuit Design:1. Obtain the values of R 1 and R 2 as per the design of an inverting amplifier.2. Select R 3 and R 4 such that R 2/R 1 = R 4/R 3.

3. Generally R 1 = R 3 and R 2 = R 4 is selected considering the requirement of the inputresistor.

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 48

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

49/54

VTU Questions:

1. Define the following terms as applied to op-amp and mention their typical values forIC741: i. CMRR; ii. Slew Rate; iii. PSRR; iv. Input Offset Voltage. v. Output Offset

Voltage. December 2015 (08 Marks), June 2014 (08 Marks), June 2013 (06 Marks)2. Sketch an op-amp direct coupled difference amplifier circuits. Explain the operation of

the circuits and derive an equation for the output voltage. December 2015 (07 Marks),December 2013 (05 Marks)

3. Design a direct coupled non-inverting amplifier to amplify 100mV signal using IC741 toa level of 4V. December 2015 (05 Marks)

4. Explain direct coupled two I/P-inverting summing amplifiers with neat diagram andnecessary design steps. June 2014 (06 Marks)

5. Design a direct coupled non-inverting amplifier to amplify 100mV signal using IC741 to

a level of 5V. June 2014 (06 Marks)6. Explain Common Mode Voltage, Common Mode Voltage Gain and Common Mode

Rejection Ratio for op-amps. Show that December 2013 (10

Marks)7. Design a direct coupled non-inverting amplifier to amplify 100mV signal using IC741 to

a level of 3V [consider ]. December 2013 (05 Marks)8. With a neat circuit diagram, explain the basic op-amp circuit. June 2013 (06 Marks),

December 2012 (08 Marks)

9.

Draw a neat circuit diagram for a direct coupled non-inverting op-amp circuit and explainthe design steps. June 2013 (04 Marks)

10. Two signals each ranging from 0.1 V to 1 V are to be summed. Using 741 op-amp designa suitable inverting summing circuits. June 2013 (04 Marks)

11. Define Slew rate and unity gain bandwidth. What is the effect of slew rate on the outputvoltage of op-amp? December 2012 (06 Marks)

12. Design an inverting amplifier using IC741 op-amp. The voltage gain is to be 50 and theoutput voltage amplitude is to be 2.5 V. December 2012 (06 Marks)

13. Derive an expression for output voltage of non-inverting summing circuit using an op-

amp, consider two inputs. June 2014 (07 Marks) 14. The non-inverting amplifier uses µA741 op-amp with R 1=R 2=2.2kΩ. Determine

maximum possible output offset voltages due toa. Input offset voltage of 5 mV.

b. Input bias current of I B(max) = 500 ἠA.c. Input offset current of I i(os) = 200 ἠA.d. Resistance tolerance of ±10% December 2015 (08 Marks)

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 49

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

50/54

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 50

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

51/54

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 51

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

52/54

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 52

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

53/54

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor

Department of ECE raghudathesh.weebly.com Page No - 53

-

8/20/2019 Linear Integrated Circuits Unit1 Raghudathesh VTU

54/54

Op-AmpFundamentals RAGHUDATHESH G P Asst Professor