Layout Decomposition for Triple Patterning Lithographybyu/papers/C07-ICCAD2011-TPL-slides.pdf ·...

Transcript of Layout Decomposition for Triple Patterning Lithographybyu/papers/C07-ICCAD2011-TPL-slides.pdf ·...

Outline

Layout Decomposition for Triple PatterningLithography

Bei Yu1 Kun Yuan2 Boyang Zhang1 Duo Ding1

David Z. Pan1

1ECE Dept. University of Texas at Austin, Austin, TX USA

2Cadence Design Systems, Inc., San Jose, CA USA

Nov. 7, 2011

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

Outline

Outline

1 Introduction

2 AlgorithmTPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

3 Experimental Results

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

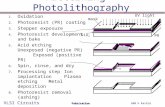

Overcome the lithography limitations

193nm based lithography tool, hard for sub-30nm

Delay or limitations of other techniques, i.e. EUV, E-Beam

Double/Multiple Patterning LithographyOriginal layout is divided into two/several masks (layout decomposition)Decrease pattern density, improve the depth of focus (DOF)Objective: minimize both conflicts and stitches

a

b

c

b

ca2

a1Stitch

a1

b

ca2

mask2

mask1

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

Triple Patterning Lithography (TPL)

b

a cConflicts

b

a c

Layout is decomposed into three masks

Similar but more difficult than 3 coloring problem

Why Triple Patterning Lithography (TPL) ?

Resolve some native conflict from DPL

Reduce the number of stitches

Triple effective pitch, achieve further feature-size scaling (22nm/16nm)

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

Layout Decomposition

DPL Layout Decomposition

Iterative Method (remove conflict→ minimize stitch) Local Optimal

Cut based methodologies (ICCAD’08, ICCAD’09, ASPDAC’2010)

Minimize conflict and stitch simultaneously

ILP Formulation (Yuan et. al ISPD’2009)→ optimal but slowHeuristic (Xu et. al ISPD’2010)→ only for planar layout

TPL Layout Decomposition

Previously only via layout is considered (Cork et. al SPIE’08)

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Layout Decomposition

Our work is the first systematic study for general layout

Mathematical Formulation

Novel Color representations

Semidefinite Programming based approximation

TPL Layout Decomposition is HARDER

Solution space is much bigger

Conflict graph is NOT planar

Detect conflict is not P, but NP-Complete

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

Problem Formulation

Problem: TPL Layout Decomposition

Input: layout and minimum coloring space.Output: decomposed layout,

minimize the stitch number and the conflict number.

Two Lemmas:

Deciding whether a planar graph is 3-colorable is NP-complete

Coloring a 3-colorable graph with 4 colors is NP-complete

Theorem 1

TPL Layout Decomposition problem is NP-Hard

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

Layout Graph and Decomposition Graph

Graphs Construction∗:1 Given input layout.2 Generate Layout Graph (LG).3 Projection.4 Generate Decomposition Graph (DG).

* same with Yuan et. al ISPD’09

Two sets of edges:

CE : conflict edge.

SE : stitch edge.

bf

ea

c d

Input Layout

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

Layout Graph and Decomposition Graph

Graphs Construction∗:1 Given input layout.2 Generate Layout Graph (LG).3 Projection.4 Generate Decomposition Graph (DG).

* same with Yuan et. al ISPD’09

Two sets of edges:

CE : conflict edge.

SE : stitch edge.

bf

ea

c d

Input Layout

da

bf

c

e

Layout Graph

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

Layout Graph and Decomposition Graph

Graphs Construction∗:1 Given input layout.2 Generate Layout Graph (LG).3 Projection.4 Generate Decomposition Graph (DG).

* same with Yuan et. al ISPD’09

Two sets of edges:

CE : conflict edge.

SE : stitch edge.

bf

ea

c d

Input Layout

da

bf

c

e

Layout Graph

bf

ea

c d

project

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

Layout Graph and Decomposition Graph

Graphs Construction∗:1 Given input layout.2 Generate Layout Graph (LG).3 Projection.4 Generate Decomposition Graph (DG).

* same with Yuan et. al ISPD’09

Two sets of edges:

CE : conflict edge.

SE : stitch edge.

bf

ea

c d

Input Layout

da

bf

c

e

Layout Graph

bf

ea

c d

project

d1a

bf

c

e1

d2

e2

Decomposition Graph

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

Overview of the TPL Decomposition Flow

ILP / Vector Programming

Input Layout

Output Masks

Layout Graph Construction

Bridge Computation

Independent Component Computation

Decomposition Graph Construction

Layout Graph Simplification

Resolve Layout Decomposition problem:Integer Linear Programming (ILP)Vector Programming

Three graph based Simplifications – improve scalability

Vector Programming can be replaced by approximation methods:Semidefinite Programming (SDP)Mapping Algorithm

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

Overview of the TPL Decomposition Flow

ILP / Vector Programming

Input Layout

Output Masks

Layout Graph Construction

Bridge Computation

Independent Component Computation

Decomposition Graph Construction

Layout Graph Simplification

Resolve Layout Decomposition problem:Integer Linear Programming (ILP)Vector Programming

Three graph based Simplifications – improve scalability

Vector Programming can be replaced by approximation methods:Semidefinite Programming (SDP)Mapping Algorithm

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

Overview of the TPL Decomposition Flow

ILP / Vector Programming

Input Layout

Output Masks

Layout Graph Construction

Bridge Computation

Independent Component Computation

Decomposition Graph Construction

Layout Graph Simplification

Resolve Layout Decomposition problem:Integer Linear Programming (ILP)Vector Programming

Three graph based Simplifications – improve scalability

Vector Programming can be replaced by approximation methods:Semidefinite Programming (SDP)Mapping Algorithm

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

Overview of the TPL Decomposition Flow

ILP / Vector Programming

Input Layout

Output Masks

Layout Graph Construction

Bridge Computation

Independent Component Computation

Decomposition Graph Construction

Layout Graph Simplification

Resolve Layout Decomposition problem:Integer Linear Programming (ILP)Vector Programming

Three graph based Simplifications – improve scalability

Vector Programming can be replaced by approximation methods:Semidefinite Programming (SDP)Mapping Algorithm

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

Mathematical Formulation

min∑

eij∈CE

cij + α∑

eij∈SE

sij (1)

s.t. cij = (xi == xj) ∀eij ∈ CE

sij = xi ⊕ xj ∀eij ∈ SE

xi ∈ {0, 1, 2} ∀i ∈ V

∑cij is the number of conflicts,

∑sij is the number of stitches

Represent 3 colors using two 0-1 variables (0, 0), (0, 1), (1, 0)

Similar to previous DPL works, (1) can be transferred to ILP

Solving ILP is NP-Hard problem, suffers from runtime penalty

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

Graph Simplification

Independent Component Computation

Partition the whole problem into several sub-problems

Bridge Computation

Further partition the problem by removing bridges

a

b

a

b

Remove bridge

a

b

a

b

Rotate colors to insert bridge

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

Graph Simplification (cont.)

Layout Graph Simplification

Iteratively remove node withdegree ≤ 2

Push the nodes into stack

Right layout can be directlycolored

bf

ea

c d

(a)

da

bf

c

e

(b)

d

a

b f

c

e

fc

(c)

d

a

b f

c

ed

be

af

c

(d)

b

d

a

b f

c

ee

af

c

(e)

d

a

f

c

ee

af

c

b

(f)

d

a

f

c

e

fc

b

(g)

d

f

c

a

b

e

(h)

bf

ea

c d

(i)

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

Vector Programming

New representation of colors

Three vectors (1, 0), (− 12 ,√

32 ) and (− 1

2 ,−√

32 )

same color: ~vi · ~vj = 1

different color: ~vi · ~vj = −1/2

(- , )√32

12

(1, 0)

(- ,- )√32

12

Vector Programming:

min∑

eij∈CE

23(~vi · ~vj +

12) +

2α3

∑eij∈SE

(1− ~vi · ~vj) (2)

s.t. ~vi ∈ {(1, 0), (−12,

√3

2), (−1

2,−√

32

)}

Equal to Mathematical Formulation (1)

Still NP-Hard

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

Semidefinite Programming (SDP) Approximation

Relax Vector Programming (2) to Semidefinite Programming (SDP)

SDP: min A • X (3)

Xii = 1, ∀i ∈ V

Xij ≥ −12, ∀eij ∈ CE

X � 0

SDP (3) can be solved in polynomial time

Mapping Algorithm

Continuous SDP Solutions⇒ Three Vectors

Tradeoff between speed and globaloptimality

Vector Programming Solutions

SDPSolutions

Mapping

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

Example of SDP Approximation

A =

0 1 1 −α 11 0 1 0 11 1 0 1 0−α 0 1 0 11 1 0 1 0

After solving the SDP:

X =

1.0 −0.5 −0.5 1.0 −0.5

1.0 −0.5 −0.5 −0.51.0 −0.5 1.0

. . . 1.0 −0.51.0

SDP: min A • X (3)

Xii = 1, ∀i ∈ V

Xij ≥ −12, ∀eij ∈ CE

X � 0

43

2

1

5

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

TPL Decomposition FlowMathematical Formulation and Graph SimplificationSemidefinite Programming (SDP) Approximation

Example of SDP Approximation

A =

0 1 1 −α 11 0 1 0 11 1 0 1 0−α 0 1 0 11 1 0 1 0

After solving the SDP:

X =

1.0 −0.5 −0.5 1.0 −0.5

1.0 −0.5 −0.5 −0.51.0 −0.5 1.0

. . . 1.0 −0.51.0

SDP: min A • X (3)

Xii = 1, ∀i ∈ V

Xij ≥ −12, ∀eij ∈ CE

X � 0

43

2

1

5

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

Experimental Results

Experimental Setting:

implement in C++

Intel Core 3.0GHz Linux machine with 32G RAM

15 layouts based on ISCAS-85 & 89 are tested

Layout parser: OpenAccess2.2

ILP solver: CBC

SDP solver: CSDP

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

Experimental Results – Graph Simplification

1

10

100

1,000

10,000

C43

2

C49

9

C88

0

C1,

355

C1,

908

C2,

670

C3,

540

C5,

315

C6,

288

C7,

552

S1,48

8

S38,4

17

S35,9

32

S38,5

84

S15,8

50

CP

U R

un

tim

e (s

)

Runtime Comparison of Normal ILP and Accelerated ILP

Normal ILP

Accelerated ILP

Graph Simplification can save 82% runtime 1

Still maintain the optimality1Normal ILP uses Independent Component Computation

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

Experimental Results – How fast is SDP?

0

5

10

15

20

25

30

35

40

45

50

C432

C499

C880

C1,35

5

C1,90

8

C2,67

0

C3,54

0

C5,31

5

C6,28

8

C7,55

2

S1,48

8

S38,4

17

S35,9

32

S38,5

84

S15,8

50

CP

U R

unti

me

(s)

Runtime Comparison of Normal ILP and Accelerated ILP

Accelerated ILPSDP Based

SDP can effectively speed-up ILP

Compared with Accelerated ILP, SDP can save 42% runtime

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

Experimental Results – How good (bad) is SDP?

0

10

20

30

40

50

60

70

80

90A

ILP

SD

P

AIL

PS

DP

AIL

PS

DP

AIL

PS

DP

AIL

PS

DP

AIL

PS

DP

AIL

PS

DP

AIL

PS

DP

AIL

PS

DP

AIL

PS

DP

AIL

PS

DP

AIL

PS

DP

AIL

PS

DP

AIL

PS

DP

AIL

PS

DP

Co

nfl

ict

Nu

m a

nd

Sti

tch

Nu

m

Comparison of Accelerated ILP (AILP) and SDP

C43

2

C49

9

C88

0

C1,

355

C1,

908

C2,

670

C3,

540

C5,

315

C6,

288

C7,

552

S1,48

8

S38,4

17

S35,9

32

S38,5

84

S15,8

50

Stitch Num

Conflict Num

Conflict NumStitch Num

SDP can achieve near optimal results.

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

Experimental Results – Dense Layout

Circuit SE# CE# Accelerated ILP SDP Basedst# cn# CPU(s) st# cn# CPU(s)

C1 16 247 1 5 5.5 0 6 0.29C2 38 289 0 15 17.32 0 16 0.77C3 24 381 0 14 33.41 0 15 0.32C4 56 437 9 32 203.17 9 32 0.49

avg. - - 2.5 16.5 64.9 2.25 17.3 0.468ratio - - 1 1 1 0.9 1.05 0.007

For very dense layout

SDP can achieve 140× speed-up.

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

Experimental Results – S1488

Stitch number: 0

Conflict number: 1

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

Conclusion

First systematic work on triple patterning layout decomposition

Mathematical formulation to minimize both stitches and conflicts

Novel color representations

Semidefinite programming based approximation

Expect to see more researches on Triple Patterning Lithography

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

Thank You !

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography

IntroductionAlgorithm

Experimental Results

Appendix – ILP Formulation

min∑

eij∈CE

cij + α∑

eij∈SE

sij (4)

s.t. xi1 + xi2 ≤ 1

xi1 + xj1 ≤ 1 + cij1 ∀eij ∈ CE

(1− xi1) + (1− xj1) ≤ 1 + cij1 ∀eij ∈ CE

xi2 + xj2 ≤ 1 + cij2 ∀eij ∈ CE

(1− xi2) + (1− xj2) ≤ 1 + cij2 ∀eij ∈ CE

cij1 + cij2 ≤ 1 + cij ∀eij ∈ CE

xi1 − xj1 ≤ sij1 ∀eij ∈ SE

xj1 − xi1 ≤ sij1 ∀eij ∈ SE

xi2 − xj2 ≤ sij2 ∀eij ∈ SE

xj2 − xi2 ≤ sij2 ∀eij ∈ SE

sij ≥ sij1, sij ≥ sij2 ∀eij ∈ SE

ICCAD2011 1A.1 Layout Decomposition for Triple Patterning Lithography