Lab #4: POLLING & INTERRUPTS...Must be Done Individually Before the Lab. 1 Describe the major...

Transcript of Lab #4: POLLING & INTERRUPTS...Must be Done Individually Before the Lab. 1 Describe the major...

Lab #4: POLLING & INTERRUPTSCENG 255 - iHaz - 2017

Must be Done Individually Before the Lab.

Recognize different kinds of exceptions.

Understand the behavior of interrupts.Realize the advantages and disadvantages of interrupts relative to polling.

Explain what polling is and write code for it.

Explain what an Interrupt Service Routine (ISR) is and write code for it.

Lab4 Objectives

Must be Done Individually Before the Lab.

1 Describe the major difference between polling and interrupt.

2 Explain what APSR, IPSR and EPSR are.

3 Explain how PRIMASK is used.

4 Explain what an exception vector table is.

5 Explain what PORT Control registers are.

Pre-Lab4 Questions

Describe the major difference between polling and interrupt.

Polling Interrupt• In polling, the processor continuously

polls or tests a given device as to whether it requires attention. The polling is carried out by a polling program that shares processing time with the currently running task. A device indicates it requires attention by setting a bit in its device status register.

• Polling the device usually means reading its status register every so often until the device's status changes to indicate that it has completed the request. This is an inefficient method and much of the processors time is wasted on unnecessary polls.

• An interrupt is a signal to the microprocessor from a device that requires attention. Upon receiving an interrupt signal, the microcontroller interrupts whatever it is doing and serves the device. The program which is associated with the interrupt is called the interrupt service routine (ISR) or interrupt handler.

• When ISR is done, the microprocessor continues with its original task as if it had never been interrupted. This is achieved by pushing the contents of all of its internal registers on the stack. The registers will then be pop(ed) from the stack on completion of the interrupt call, allowing the microprocessor to resume its original task.

Polling vs. Interrupt

A) Polling: FaceBook with notifications Disabled B) Interrupt: FaceBook with notifications Enabled.

Example: Detecting a pulse lasting for 1ms, which appears once in 10s at random timing. Polling method: Check every 500us for example for this pulse so we don’t miss it. Interrupt detection ISR: Triggers itself and executes this only when pulse occurs (much more efficient).

Polling is good for operations that are not dependent on exact timings.

Polling vs. Interrupt

Explain what APSR, IPSR and EPSR are.Program status register The Program Status Register (PSR) combines: ● Application program status register (APSR): Contains the current state of The condition flags from previous instruction executions. ● Interrupt program status register (IPSR): contains the exception type number of the current ISR. Bit[31:6] of IPSR are reserved while Bit[5:0] are applied to the current ISR number. ● Execution program status register (EPSR): The EPSR contains the Thumb state bit.

APSR, IPSR, EPSR and PRIMASK

Explain how PRIMASK is used.The priority mask register (PRIMASK) prevents activation of all exceptions with configurable priority. Bit[31:1] of PRIMASK are reserved and there is no effect when Bit[0]=0, but it prevents the activation of all exceptions with configurable priority when Bit[0]=1.

Explain what an exception vector table is.ARM provides the Cortex Microcontroller Software Interface Standard (CMSIS) for programming the Cortex-M0 microcontroller. The CMSIS defines a standard way to access peripheral registers and to define exception vectors, the names of the registers of the core peripherals and the core exception vectors.The entry for IRQ0 is located at 0x00000040 because the IRQ0 is located at position 16 in the vector table.

Exception Vector Table

Explain what PORT Control registers are.STM32F051 microcontroller has five general-purpose input/output (GPIO) ports, Port A, B, C, D and F. Each port can have up to 16 pins, and each port has associated with it the following set of registers: • GPIO port mode register (GPIOx_MODER)• GPIO port output register (GPIOx_OTYPER)• GPIO port output speed register (GPIOx_OSPEEDR)• GPIO port pull-up/pull-down register (GPIOx_PUPDR)• GPIO port input data register (GPIOx_IDR)• GPIO port output data register (GPIOx_ODR)• GPIO port bit set/reset register (GPIOx_BSRR)• GPIO port configuration lock register (GPIOx_LCKR)• GPIO alternate function low register (GPIOx_AFRL)• GPIO alternate function high register (GPIOx_AFRH)

STM32F051 Microcontroller GPIO

Operating Modes• Seven operating modes:

– User

– Privileged: • System

• FIQ

• IRQ

• Abort

• Undefined

• Supervisorexception modes

Operating Modes (2)

User mode:

– Normal program execution mode

– System resources unavailable

– Mode changed by exception or software interrupt (trap instruction)

Exception modes:

– Entered upon exception

– Full accessto system resources

– Mode changed freely

Exceptions

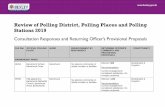

Table 1 - Exception types, sorted by Interrupt Vector addresses

Exception Mode Priority IV Address

Reset Supervisor 1 0x00000000

Undefined instruction Undefined 6 0x00000004

Software interrupt Supervisor 6 0x00000008

Prefetch Abort Abort 5 0x0000000C

Data Abort Abort 2 0x00000010

Interrupt IRQ 4 0x00000018

Fast interrupt FIQ 3 0x0000001C

Lab Hardware (Boards)

DIO1 board features include• A four digit seven-segment LED display;• 8 individual LEDs;• A 3-bit VGA port;• 5 momentary pushbuttons;• 8 slide switches;• A PS2 mouse/keyboard port.

http://www.ece.uvic.ca/~ceng255/lab/lab_files/interrupt.zip

DigiLab DIO1 Board

DigiLab DIO1 Board Diagram

Digilab DIO1 Board Diagram

Digilab DIO1 Board Diagram

Digilab DIO1 Board Diagram

Abbreviation Definition

A1 - A4 Seven-segment anode connection

CA - CG Seven-segment cathode connection

BTN1-BTN4, BTN5 Push button connection

SW1 - SW8 Slide switch connection

LD1 - LD8 Light Emitting Diode connection

CLK1 Clock connection

DIO1B Pin Signal DIO1B Pin SignalA1 A21A2 A22A3 A23A4 A24A5 A25A6 A26A7 A27A8 A28A9 A29A10 A30A11 A31 BLUA12 A32 PS2DA13 A33 GRNA14 A34 PS2CA15 A35 REDA16 A36 HSA17 A37 VCCA18 A38 VSA19 A39 GNDA20 A40 VU

DIO1B Pin Signal DIO1B Pin SignalB1 CA B21 A1B2 SW1 B22 LD1B3 CB B23 A2B4 SW2 B24 LD2B5 CC B25 A3B6 SW3 B26 LD3B7 CD B27 A4B8 SW4 B28 LD4B9 CE B29B10 SW5 B30 LD5B11 CF B31B12 SW6 B32 LD6B13 CG B33B14 SW7 B34 LD7B15 DP B35 BTN5B16 SW8 B36 LD8B17 BTN2 B37 VCCB18 BTN1 B38 LDGB19 BTN4 B39 GNDB20 BTN3 B40 VU

Digilab DIO1 Board (PINs)

Polling

Given Required

The following program tests the status of Port PA4, and uses a button to change the status of port PA4.

a) Revise the program in such a way that another button (btn2) can do the same operation.

In this experiment, initially all LEDs on the board are off.

b) Consider having two buttons, modify the program so that the LEDs toggle only if you push the buttons in the following order: Pushing button number one (btn1) twice and button number two (btn2) once.

Pressing the button (btn1) makes one LED toggle.

Include a well-commented listing of your program.

For this part of the lab, you are required to change the program as follows:

Explain the changes that you have made in the provided program and the

The Lab Task

http://www.ece.uvic.ca/~ceng255/lab/lab_files/polling.zip

Interrupt

Given Required

The provided program in Figure 9 uses a button to send an interrupt to the processor.

a) Revise the program in such a way that another button (btn2) generates another interrupt and increments the content of the counter.

The program is running a loop until it receives an interrupt. Having received the interrupt, the processor completes the execution of the current instruction and jumps to the interrupt handler.

b) Consider having two buttons, modify the program so that the LEDs toggle only if you receive interrupts in the following order: Pushing button one (btn1) three times and button two (btn2) twice.

We increment the contents of a counter by one inside the interrupt handler and display its contents on the LEDs

Include a well-commented listing of your program.

You are required to change the program to add the following functionality.

Explain the changes that you have made in the provided program and the

The Lab Task

http://www.ece.uvic.ca/~ceng255/lab/lab_files/interrupt.zip

An exception is an automatic procedure call initiated by some events during the execution of a program.

Exception and interrupt change the control or execution flow of a program when certain conditions occur.They are designed to be special events which occurrence cannot be predicted precisely.Exceptions occur as a result of an event during a program’s execution.While an interrupt is a hardware event that is triggered by an external source

What is an Exception

Some common exceptions are undefined op-codes, privileged instructions, virtual memory page faults, and

system calls (i.e., operating system service request).

If the divisor of a division is equal to zero, a divided-by-zero trap will occur.As a result, the control flow is transferred to some fixed memory location instead of continuing in sequence in the currently executing program.At the fixed location, there exists a branch instruction to a routine called the exception handler, which performs some appropriate actions.The essential point about an exception is that it is synchronous with program execution, meaning that it happens as a result of executing some instructions.

What is an Exception - Example

It is crucial to return to the interrupted program in the same state as processor was in when the interrupt occurred

An interrupt is a hardware event that triggers the processor asynchronously to branch from its current PC to a specific location in the memory.After the interrupt stops the currently executing program, it transfers control to a fixed address that calls the appropriate Interrupt Service Routine (ISR), which performs some needed actions. The control will return to the interrupted program when the handler completes the required actions.The external interrupt handler’s address in ARM depends on an 8-bit vector number, which is supplied by the interrupt controller module.

Interrupts

The processor and the Nested Vectored Interrupt Controller (NVIC) prioritize and handle all exceptions that change the normal flow of software control.The NVIC supports up to 32 individual interrupts, each of which has 4 priority levels (higher 0-3 lower)..The processor automatically stacks its state on exception entry and un-stacks its state on exception exit, with no inst. overheadAfter an interrupt occurs, the processor does the following: • Complete current instruction execution • Suspend currently executing program • Stack eight registers (R0, R1, R2, R3, R12, LR, PC, xPSR) • Write an EXC_RETURN value to LR • Write the interrupt number to IPSR • Load PC with the interrupt vector

ARM Interrupt Structure

The general procedure to configure the external interrupt (EXTI) peripheral as well as the NVIC peripheral is as follows:

1 Configure the EXTIXX bits in the SYSCFG_EXTICRX registers to map the GPIO pin(s) of interest to the appropriate external interrupt lines (EXTI0- EXTI15).

2

For the external interrupt lines (EXTIXX) of interest, choose a signal change that will trigger the external interrupt. The signal change can be a rising edge, a falling edge or both. These can be set via the EXTI_RTSR (rising) and the EXTI_FTSR (falling) registers.

3 Unmask the external interrupt line(s) of interest by setting the bit corresponding to the EXTI line of interest in the EXT_IMR register.

4 Set the priority for the interrupt vector in the NVIC either via the CMSIS based “NVIC_SetPriority()” function or through the IPR0- IPR7 registers.

5 Enable the interrupt in the NVIC either via the CMSIS based “NVIC_EnableIRQ()” function or via the ISER register.

6 Write your interrupt service routine (ISR), defined in vectors_stm32f0xx.c

7 Inside your interrupt service routine, check the source of the interrupt, which can be from the GPIO pin directly or the external interrupt line.

ARM Interrupt Procedure

The three EXTIXX Line Handlers are defined as:void __attribute__ ((weak, alias ("Default_Handler"))) EXTI0_1_IRQHandler(void);void __attribute__ ((weak, alias ("Default_Handler"))) EXTI2_3_IRQHandler(void);void __attribute__ ((weak, alias ("Default_Handler"))) EXTI4_15_IRQHandler(void);

ARM Interrupt Procedure

Polling a device means reading its status register regularly until the device's status changes to indicate that it has a request or has accomplished a task.The disadvantage in this method of finding out the status of a device is that the CPU needs to keep asking the same question over and over when it could be doing other useful work.In this situation, the performance of the application program decreases. However, if the processor is used for a single task, this approach may be used due to its simplicity. - The loading process of ISR and provide the information that

we need to configure and use GPIO in Eclipse is discussed. - Some templates that could be used for polling and interrupt

service routines are presented. - These templates need to be Changed to fulfill this lab’s goals.

Polling

The entry for IRQ0 is located at 0x00000040 because the IRQ0 is located at position 16 in the vector table.ARM provides the Cortex Microcontroller Software Interface Standard (CMSIS) for programming the Cortex-M0 microcontroller. The CMSIS defines a standard way to access peripheral registers and to define exception vectors, the names of the registers of the core peripherals and the core exception vectors. The following functions are provided: // Enables an interrupt or exceptionvoid NVIC_EnableIRQ(IRQ_Type IRQn)// Sets priority of an interrupt/exception with configurable priority level to 1 //void NVIC_SetPriority(IRQ_Type IRQn, uint32_t priority)

Configure the ISR

The interrupt program status register (IPSR) contains the exception type number of the current ISR. Bit[31:6] of IPSR are reserved while Bit[5:0] are applied to the current ISR number. The exception master registers disable the handling of exceptions by the processor. Exceptions are disabled in situations where they might impact on time critical tasks or code sequences.The priority mask register (PRIMASK) prevents activation of all exceptions with configurable priority. Bit[31:1] of PRIMASK are reserved and there is no effect when Bit[0]=0, but it prevents the activation of all exceptions with configurable priority when Bit[0]=1.The interrupt priority registers (IPR0-IPR7) provide an 8-bit field for each interrupt and are only word-accessible, each of which holds four priority fields. Each priority field holds a priority value, 0-192. The lower the value, the higher is the priority of the corresponding interrupt. The processor implements only Bit[7:6] of each field, while Bit[5:0] read as zero and ignore writes.

Interrupt Controller Registers

IPR register mapping

STM32F051 microcontroller has five general-purpose input/output (GPIO) ports, Port A, B, C, D and F. Each port can have up to 16 pins, and each port has associated with it the following set of registers: • GPIO port mode register (GPIOx_MODER)• GPIO port output register (GPIOx_OTYPER)• GPIO port output speed register (GPIOx_OSPEEDR)• GPIO port pull-up/pull-down register (GPIOx_PUPDR)• GPIO port input data register (GPIOx_IDR)• GPIO port output data register (GPIOx_ODR)• GPIO port bit set/reset register (GPIOx_BSRR)• GPIO port configuration lock register (GPIOx_LCKR)• GPIO alternate function low register (GPIOx_AFRL)• GPIO alternate function high register (GPIOx_AFRH)• GPIO port bit reset register (GPIOx_BRR)

STM32F051 Microcontroller GPIO

where the ‘x’ in each register’s acronym represents the port, i.e., the GPIOx_MODER associated with port A is called GPIOA_MODER.

A 16-bit read/write register. Writing a ‘0’ in bit 8 of the GPIOC_ODR register indicates that the voltage on PC8 is driven by the microcontroller to 0V (GND) (‘1’ —>> 3.3V (VDD)). To access this register, CMSIS provides the handler GPIOx→ODR in C language. Writing to the ODR register is good if you want to write to the entire port.e.g. GPIOC->ODR = 0xF0FEThe above statement changes the state of every pin on the GPIOC peripheral from its previous (and now discarded) state, to the one indicated by the statement; 0xF0FE (0b1111000011111110).However if you want to set only a single pin; lets say PC8 without affecting the state of the rest of the pins on GPIOC, you have to perform a read-modify-write (RMW) access. To set pin PC8 independent of all other pins on GPIOC (RMW):GPIOC->ODR |=0x00000100;//(0b00000000000000000000000100000000)

To clear pin PC8 independent of all other pins on GPIOC (RMW):

GPIOC->ODR &=~(0x00000100);//(0b00000000000000000000000100000000)This works fine, but you have to read the ODR register, OR (|) or AND(&) (modify) it with a mask and then write it back to the ODR register.

Port Output Data Register (GPIOx_ODR)

This is a 32-bit register where each set of two consecutive bits represents the mode of a single I/O pin. For example bits 0 and 1 of the MODER register associated with GPIOC (GPIOC_MODER) represent the mode of GPIO pin PC0, and bits 26 and 27 of the same register represent the mode of GPIO pin PC13. These two bits can be set to:

Port Mode Register (GPIOx_MODER)

which allows the GPIO pin to be used as an input pin. which allows the GPIO pin to be used as an output pin. which allows the GPIO pin to be used as an analog input pin. which allows the GPIO pins to be used by as the UART, SPI, etc.

This is a 16-bit register where each bit denotes the ‘type’ of a single pin in the register. This register sets the type of output pins to either push-pull or open drain. For example, if pin PC7 is configured as an output pin, clearing bit 7 (or leaving its state at zero) of the OTYPER register associated with GPIOC (GPIOC_TYPER), will set the output type of the GPIO output pin PC7 to “Push-Pull”.

Port Output Type Register (GPIOx_OTYPER)

This is a 32-bit register where each set of two bits represents the speed of a single output pin. For example bits 0 and 1of the OSPEEDR register associated with port C (GPIOC_OSPEEDR) represent the speed setting of the output pin PC0, and bits 26 and 27 of the same register represent the speed setting of the output pin PC13. These two bits can be set to

Port Output Speed Register (GPIOx_OSPEEDR)

The GPIOx_PUPDR register configures the internal pull-up and pull-down resistors on each I/O pin. The internal pull-up/-down resistor can be configured on GPIO pins set as input or output. The Pull-up/-down resistor has a typical value of 40 kohms but can range from 30-50 kohms. Again each two consecutive bits represent the internal pull-up/-down resistor setting for each pin within a single port

Port Pull-up/Pull-down Register (GPIOx_PUPDR)

This is a 16-bit read-only register. Each bit represents the input value on a corresponding pin. Reading a ‘0’ in bit 8 of this GPIOC_IDR register indicates that the voltage on PC8 is 0V (GND). While reading a ‘1’ in bit 8 of this GPIOC _IDR register indicates that the voltage on PC8 is 3.3V (VDD).

Port Input Data Register (GPIOx_IDR)

Polling#define TRUE (1==1) #define FALSE (1==0) #define BUTTON_PUSHED TRUE #define BUTTON_RELEASED FALSE #define LED_ON TRUE #define LED_OFF FALSE GPIO_InitTypeDef GPIO_InitStructure;

int ReadButton1Status( void ) { if(GPIOA->IDR & GPIO_Pin_4) return( BUTTON_PUSHED ); return( BUTTON_RELEASED ); }

/* GPIOD Periph clock enable */ RCC_AHBPeriphClockCmd(RCC_AHBPeriph_GPIOA, ENABLE); RCC_AHBPeriphClockCmd(RCC_AHBPeriph_GPIOC, ENABLE);

//configure the PA0 as the output pin GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_OUT; GPIO_InitStructure.GPIO_OType = GPIO_OType_PP; GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_NOPULL; GPIO_Init(GPIOA, &GPIO_InitStructure);

while (1){ if( BUTTON_PUSHED == ReadButton1Status()) GPIO_SetBits(GPIOA, GPIO_Pin_0); else GPIO_ResetBits(GPIOA, GPIO_Pin_0);}

//configure PA4 as the input pin GPIO_InitStructure.GPIO_Pin = GPIO_Pin_4 | GPIO_Pin_5; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN; GPIO_InitStructure.GPIO_OType = GPIO_OType_PP; GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_DOWN; GPIO_Init(GPIOA, &GPIO_InitStructure);

The Lab Code

InterruptEXTI_InitTypeDef EXTI_InitStructure; GPIO_InitTypeDef GPIO_InitStructure; NVIC_InitTypeDef NVIC_InitStructure; volatile int EXTI4Counter = 0b0000;

while (1) { if ((EXTI4Counter & 0b1000) != 0) GPIO_SetBits(GPIOA, GPIO_Pin_0); else GPIO_ResetBits(GPIOA, GPIO_Pin_0); if ((EXTI4Counter & 0b0100) != 0) GPIO_SetBits(GPIOA, GPIO_Pin_1); else GPIO_ResetBits(GPIOA, GPIO_Pin_1); if ((EXTI4Counter & 0b0010) != 0) GPIO_SetBits(GPIOA, GPIO_Pin_2); else GPIO_ResetBits(GPIOA, GPIO_Pin_2); if ((EXTI4Counter & 0b0001) != 0) GPIO_SetBits(GPIOA, GPIO_Pin_3); else GPIO_ResetBits(GPIOA, GPIO_Pin_3); }

/* Enable GPIOA clock */ RCC_AHBPeriphClockCmd(RCC_AHBPeriph_GPIOA, ENABLE);

//configure the PA0, PA1, PA2, PA3 as the output pin GPIO_InitStructure.GPIO_Pin=GPIO_Pin_0|GPIO_Pin_1|GPIO_Pin_2|GPIO_Pin_3; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_OUT; GPIO_InitStructure.GPIO_OType = GPIO_OType_PP; GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_NOPULL; GPIO_Init(GPIOA, &GPIO_InitStructure);

//configure PA4 and PA5 as the input pin GPIO_InitStructure.GPIO_Pin = GPIO_Pin_4 | GPIO_Pin_5; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN; GPIO_InitStructure.GPIO_OType = GPIO_OType_PP; GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_DOWN; GPIO_Init(GPIOA, &GPIO_InitStructure);

/* Enable SYSCFG clock */ RCC_APB2PeriphClockCmd(RCC_APB2Periph_SYSCFG, ENABLE);

void EXTI4_15_IRQHandler(void) { if (EXTI->IMR & EXTI_IMR_MR4 ) { if ( EXTI->PR & EXTI_Line4 ) { EXTI4Counter = ( EXTI4Counter + 1 ) & 15; EXTI->PR |= EXTI_PR_PR4; }

if ( EXTI->PR & EXTI_Line5 ) { EXTI4Counter = ( EXTI4Counter - 1 ) & 15; EXTI->PR |= EXTI_PR_PR4; } } }

/* Connect EXTI0 Line to PA0,PA1,PA2,PA3 pin */ SYSCFG_EXTILineConfig(EXTI_PortSourceGPIOA, EXTI_PinSource0|EXTI_PinSource1 |EXTI_PinSource2|EXTI_PinSource3);

/* Configure EXTI4 line and EXTI5 line*/ EXTI_InitStructure.EXTI_Line = EXTI_Line4 | EXTI_Line5; EXTI_InitStructure.EXTI_Mode = EXTI_Mode_Interrupt; EXTI_InitStructure.EXTI_Trigger = EXTI_Trigger_Falling; EXTI_InitStructure.EXTI_LineCmd = ENABLE; EXTI_Init(&EXTI_InitStructure);

/* Enable and set EXTI4_15 Interrupt */ NVIC_InitStructure.NVIC_IRQChannel = EXTI4_15_IRQn; NVIC_InitStructure.NVIC_IRQChannelPriority = 0x00; NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE; NVIC_Init(&NVIC_InitStructure);

The Lab Code

References

http://www.ece.uvic.ca/~kinli/ceng255/CENG-255-2016-Lab4.pdf

http://www.ece.uvic.ca/~ceng255/lab/

http://www.ece.uvic.ca/~ceng255/lab/docs/PM0215_STM32F0_Cortex_M0_Programming_Manual.pdf

http://www.ece.uvic.ca/~kinli/ceng255/ARM7-TDMI-manual-pt3.pdf

http://www.mrc.uidaho.edu/mrc/people/jff/240/241/docs/pin_table.pdf

http://www-classes.usc.edu/engr/ee-s/201/Digilent/DIO1-sch.pdf

http://www.pa.msu.edu/courses/2016fall/PHY440/Miscellany/DIO1-rm.pdf

http://www-classes.usc.edu/engr/ee-s/201/ee201l_lab_manual_Spring2007/Spring2007_PDFs/Addendum1_Digilab.pdf

http://www.electronics-base.com/useful-info/software-related/90-polling-vs-interrupt