JVC GR-DVF31U DVL40EG (1999 Fusion DVC Models) Technical Guide

Transcript of JVC GR-DVF31U DVL40EG (1999 Fusion DVC Models) Technical Guide

VIDEO TECHNICAL GUIDE

COPYRIGHT © 1999 VICTOR COMPANY OF JAPAN, LTD. Septmber 1999

GR-DVF31U/DVL40EG NTSC/PAL

(1999 Fusion DVC Model)

DIGITAL VIDEO MOVIE

INDEX

INDEX-1

SECTION 1 OUTLINE OF THE PRODUCTS1.1 COMPARISON TABLE OF DV MODELS SPECIFICATION BY PRODUCTS YEAR.............1-1

1.1.1 Comparison table of DV models specification by products year .....................................1-11.1.2 DV model chart table of LCD type..................................................................................1-2

SECTION 2 EXPLANATION OF ELECTRICAL CIRCUT2.1 CIRCUIT OUTLINE ..............................................................................................................2-1

2.1.1 Reference block diagram (GR-DVF31U)........................................................................2-12.1.2 Explanation of PLL operation .........................................................................................2-22.1.3 Explanation of PB equalizer and ATF operations ...........................................................2-32.1.4 Explanation of PC terminal and JLIP terminal ................................................................2-4

2.2 CPU FUNCTIONS................................................................................................................2-62.2.1 SYSCON CPU (IC1001) function ...................................................................................2-62.2.2 DECK CPU (IC1401) function ........................................................................................2-92.2.3 MDA IC (IC1601) function..............................................................................................2-142.2.4 CDS AGC AD IC (IC5601) function................................................................................2-202.2.5 B/W LCD driver IC (IC7001) function (for GR-DVF11U) .................................................2-22

SECTION 1OUTLINE OF THE PRODUCTS

1-1

1.1 COMPARISON TABLE OF DV MODELS SPECIFICATION BY PRODUCTS YEAR1.1.1 Comparison table of DV models specification by products year (1/2)

ModelFunctionBattery BN-V11 Ni-Cd (6V, 1100 mAh)

BN-V12 Ni-Cd (6V, 1200 mAh)BN-V20 Ni-MH (6V, 2000 mAh)

Charging time: AA-V15 used 70 min. (BN-V11) 70 min. (BN-V12) 110 min. (BN-V20)

BN-V207 Lithium-ion (7.2V, 700 mAh)BN-V214 Lithium-ion (7.2V, 1400 mAh)

Charging time: AA-V20 used 90 min. (BN-V207) 180 min. (BN-V214)

Charging of battery in the unit No ←Lens cover Yes

Manual Shutter←Cap

Viewfinder Color LCD 0.55" 113k pixelsB/W CRT

Color LCD 0.55" 113k pixelsB/W LCD

LCD monitor Non2.5" 480 × 234 = 112k pixels3" 480 × 234 = 112k pixelsHorizontal resolution: 240 linesAmorphous silicon transistor

2.5" 480 × 234 = 112k pixels3" 480 × 234 = 112k pixels3.5" 480 × 234 = 112k pixelsHorizontal resolution: 240 linesAmorphous silicon transistor

Image device 1/4"Total 766 × 596 = 460k pixels (*766 × 711 = 540k pixels)Effective aria 611 × 480 = 290k pixels (*601 × 576 = 350k pixels)

1/4"Total 998 × 677 = 680k pixels (*998 × 797 = 800k pixels)Effective aria 711 × 485 = 340k pixels (*702 × 575 = 400k pixels)

Horizontal resolution 360 Lines 400 LinesProgressive scanning No ←Electric image stabilizer Yes ←Sensitivity lux 16 lux (*18 lux)

60 IRE Level Slow Shutter offLens specification F1.6 f = 3.9 to 62.4 mm F1.6 f = 3.9 to 62.4 mmTele macro Yes ←Zoom ratio Optical zoom: 16×

Digital zoom: 4×/10× or 8×/20×Max. zoom: 160× or 320×

Optical zoom: 16×Digital zoom: 4×/10×,25× or 28×Max. zoom: 160× ,400× or 450×

Snapshot 5 modeWith frameFullPin-upPin-up 4-divisionPin-up 9-division

←

Playback snapshot Yes ←Playback digital zoom Yes 10×

RM-V712UYes 4×RM-V711U (optional: GR-DVF11U)

Slow motion YesRM-V712U

Yes (Frame Advance)RM-V711U (optional: GR-DVF11U)

Auto flash No ←Video auto light Yes Yes ( /No)Audio 2ch(48kHz) /4ch(32kHz) 2ch(48kHz) /4ch(32kHz)Snapshot search No ←Record end search No ←Audio dubbing No (Yes:PAL model,32kHz only,RCU only) Yes (32kHz only,RCU only)

1998 Fusion DV Model 1999 Fusion DV Model

Table 1-1-1 Comparison table of DV models specification by products year (1/2)

1-2

•••• Comparison table of DV models specification by products year (2/2)

ModelFunctionV.insert editing No ←Time code Yes ←Headphone terminal No ←AV output terminal RCA

(Video Audio L/R)←

S output terminal Yes ←JLIP terminal Yes ←PC terminal No Yes (No: GR-DVF11U)Digital still image outputterminal

No Yes (No: GR-DVF11U)

DV terminal No Yes (EG/EK Model Output only)JLIP relatedsoftware

JLIP video capture box GV-CB3 (optional) JLIP video capture Ver.2.0 JLIP video producer Ver.1.13

Provided CD-ROM or optional HS-V4KIT (/No: GR-DVF11U) JLIP video capture Ver.3.0 JLIP video producer Ver.1.16

JLIP ID number 06 ←Remote control sensor Yes ←Button battery(only for clock backup)

Yes: CR-2025 type Yes: CR-2032 type (built-in)

1998 Fusion DV Model 1999 Fusion DV Model

Table 1-1-1 Comparison table of DV models specification by products year (2/2)

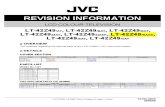

1.1.2 DV model chart table of LCD type

1998 Fusion DV Model

LCD Monitor/VF

VICTOR JVC-NTSC

Non/ Color GR-DVA1U GR-DVF1EG GR-DVF1EK GR-DVF3A GR-DVF15SH

2.5"/ BW CRT GR-DVF10U

2.5"/ Color GR-DVF10EG GR-DVF10EK GR-DVF7A GR-DVF10EA GR-DVF25SH

3.0"/ Color GR-DVF20U

1999 Fusion DV Model

LCDMonitor/VF

VICTOR JVC-NTSC

2.5"/ BW LCD GR-DVF1 GR-DVF11U,21U GR-DVL20EG GR-DVL20EK GR-DVL25A GR-DVL20EA GR-DVL28ED

3.0"/ BW LCD GR-DVL30EG GR-DVL30EK GR-DVL33SH

3.0"/ Color GR-DVF31U GR-DVL38SH

3.5"/ Color GR-DVA1 GR-DVL40EG GR-DVL40EK GR-DVL45A GR-DVL40EA GR-DVL48ED

JVC-PAL

JVC-PAL

Table 1-1-2 DV model chart table of LCD type

SECTION 2EXPLANATION OF ELECTRICAL CIRCUIT

2-1

2.1 CIRCUIT OUTLINEThe basic circuit of GR-DVF31U and GR-DVL40EG descriptions only a difference in this technical guidebecause it is the same as GR-DVM70U/DVX7E.Refer to technical guide of GR-DVM70U/DVX7E for the part which isn't descriptioned.

2.1.1 Basic block diagram (GR-DVF31U)

CCD

IC4301

CAMERA_DSP

IC4302

FIELDMEMORY

TMY(8) , TMC(4)

TGV.DRV

IC5501

FOCUSDRIVER

&ZOOM

DRIVER

IC4851

IRISDRIVER

IC4801,IC4802SYSCON

CPU

IC1001

D Y O ( 4 ) , D C O ( 4 )

BU

S(1

6)

LCDDRIVER

IC7601

I N D

L C D _ Y

L C D _ B - Y , L C D _ R - Y

M O N I T O R70

M O N _ G

M O N _ R

M O N _ B

LCDPANEL

LCDPANEL

Y _ O U T

T X

V _ O U T

A/VOUT

IRIS_O/C

A F Z _ D A T A

IC3001

DECK_DSP

IC3002

16MDRAM

IC3501

REC AMP&

PB AMP

IC1401

DECKCPU

IC3201

DVEQ

IC3301

DVANA

H S EIC2101

AUDIOA/D, D/A

IC3503

EVRDAC

A_OUT/ L

AUDIOAMP

IC2201

PB

_AU

/ L

PB

_AU

/ R

R D ( 1 6 )

RA(10 )

M I C U N I TINT_MIC / L

INT_MIC / RAO_SIG / R

AO_SIG / L

MA IN10

FMY(8 ) , FMC(4 )

H1 , H2 , RG

SSI

X A V D , X A H D

IC1003

E 2 PROM

IC1004

RTC32kHz

X1002

A N A _ D A T AS _ D T _ I N

AD(16 )

S _ D T _ I N

S _ D T _ O U T

ONSCREEN

IC1002

DRIVE+ , -

F O C U S ( 4 )

Z O O M ( 4 )

S OUT

IC1601

MDA M

M

M

C A P S T A NM O T O R

D R U MM O T O R

L O A D I N GM O T O R

V I D E OH E A D

VIDEODRIVER

IC3701

I R I S P W M

AID

AT

DO

DA

T

AID

AT

DO

DA

T

MD

A_I

NM

DA

_OU

T

V C O , A T F _ G A I N

DV

_C, D

V_Y

DV

_R-Y

, DV

_B-Y

D V _ C , D V _ Y

L C D _ I N D

L C D _ I N D

I N D

A F Z _ D A T A

C L K 2 7 , C L K 1 8 , C L K 1 3

OPTICALBLOCK

C C D _ O U T CDS/AGCA/D

IC5601

C A M _ A D ( 1 0 )

54MHz

X5501

1394PHY

IC3101TPA+ ,TPA-TPB+ ,TPB-

D V _ J A C K

OS

D_D

AT

A

S W

IC7604

V F _ G

V F _ R

V F _ B

SS

I

S U B

S _ D T _ O U T

L O A D _ F W DL O A D _ R E V

A V C O C

V1,V2,V3,V4

S E C O N D20

PD(4)

DYI (4) ,DCI (4)

HS

E

PB

DA

TA

AD

DT

(16)

AD

DT

(16)

A D D T ( 1 6 )

AN

A_D

AT

A

V F01

MIC

_AU

/ L

MIC

_AU

/ R

S P K + , S P K -

SP

P B _ E N V

P B _ E N V

IRIS

PW

M

R

G

B

R E C C _ A D JV

RE

F_Y

,VR

EF

_C,V

RE

F_R

B

R E C C _ A D J

H _ G A I N , H _ O F F S E T

Y _ G C T L , C _ G C T L , A S P E C T

H _ G A I N , H _ O F F S E T

Y C _ G C T L , A S P E C T

A F Z _ D A T A

A _ O U T / R

M D A _ I N , M D A _ O U T

C C D40

JUNCTION30

D _ C O I L _ UD _ C O I L _ VD _ C O I L _ W

C _ C O I L _ UC _ C O I L _ VC _ C O I L _ W

PC

JLIP

R X

T X

R X

R X

T X

RX

TX

SR

V_T

X

S R V _ R X

1 F1 S2 F2 S

P B O

A T F O

Fig. 2-1-1 Basic block diagram (GR-DVF31U)

2-2

2.1.2 Explanation of PLL operation

X5501

54MHz

T GV . D R V

IC5501

V C X O

V C O

X3301

81MHz

PH

YC

LK

P W M 4 0 5

IC3001CLK

27

V C O V C O A U DP W M A U D

V C O A U D

A012A V C O C

X3001

24.576MHz

MAIN_VCO

A07MAIN_VCO

ADJ

A04FS_PLLADJ

JIG CONN

IC3301

FS_PLLJ IG CONN

C L KO S C

P C

F R PG E N

81MHz

41.85MHz

Serial I /FF rom

D E C K _ C P U12.288MHz11.289MHz

8.192MHz

D V D S P

D V A N A

F R PG E N

MAIN CLK

1394L INK

R E F

1394P H Y

P C

R E F

27MHz F R P

F R P

D O M C K

40.5MHz Not used

REC CLK

IC3101

A N A _ D A T A

VC

O40

5I

VCO405

Fig. 2-1-2 PLL operation block diagram

The main clock for the deck section operates at a frequency of 40.5 MHz, which is equivalent to 18 MHzfor the previous models. Since two memories of the SHUFFLE memory and the ECC memory that areneeded for the previous models are integrated into one DRAM, the clock frequency is raised in order toincrease the processing speed. For setting the clock duty ratio exactly at 50 %, 40.5 MHz clock isproduced from the 81 MHz clock. The PLL circuit of the main clock system produces 81 MHz clock by theX'TAL X301 and VCXO, and sends the 81 MHz clock to the IC3001 DV DSP. Using the frame pulseproduced from the 81 MHz pulse as the comparison signal of the PLL, the frame pulse (29.97 Hz in NTSCor 25 Hz in PAL) is produced from the 27 MHz pulse output from the camera and this frame pulse is usedas the reference signal of the PLL in the general recording and playback modes. However, the frame pulseproduced by decoding the input DV signal is used as the PLL reference signal for phase comparison in the1394 input mode. A phase error is output as the PWM405 signal, which passes through the filter circuitand controls the VCXO. For PLL adjustment, the filter output voltage is set nearly at the center (1.2 V ± 0.1V) of the tolerance in the condition that the PLL is locked.There are three audio sampling frequencies (32 kHz, 44.1 kHz and 48 kHz) provided, therefore, masterclocks (8.192 MHz, 11.289 MHz and 12.288 MHz) are produced by the VCO in the IC3301 for therespective sampling frequencies, and those master clocks are output to the IC3001 DV DSP. For adjustingthe FS-PLL, the respective frequencies are adjusted in the free-run status.

2-3

2.1.3 Explanation of PB equalizer and ATF operations

L P F A G C

B P F G C A

A02

A D 1A U T O

E Q1 + D VITERBI

P L LD E T2 C H

D A CP W M

A D 2

V C O

A T F

C P UI/F

J IG CONNP B _ V C O

IC3203

P B _ E N V

DISCRI

R E C C L K

P B _ D A T A

PB_CLK

R E C C T L

ADDT00:15S E R V O

C P U

IC3301 IC3201D V _ A N A D V _ E Q

41.85MHz

41.85MHz

+ -

P B O

A T F O

PLLO CLK

V O A

V O BR E F V

PLLE

AINAD2

AINAD1

ATF_GAIN

DISCR

CTL1

D T R

REC:H

S W

Fig. 2-1-3 PB equalizer and ATF operation block diagram

In the playback mode the PB ENV signal output from the PB amp. is branched into two in the IC3301 DVANA; one is the signal for playback data and the other is that for ATF. The PBO signal output through theLPF and AGC is sent to the IC3201 DV EQ as that for playback data, while the ATFO signal outputthrough the BPF and GCA is also sent to the IC3201 DV EQ as that for ATF.In the IC3201 DV EQ, the playback signal undergoes digitalization (AD1), waveform equalization (AUTOEQ), SI-NRZI channel decoding (1+D), and Viterbi-decoding (VITERBI). The resultant signal processed asmentioned above is output from the IC3201 as the playback data signal. At the same time, the PLL circuitconstructed in this circuitry controls phase correction in order to generate the PB clock synchronizing withthe playback signal. The 41.85 MHz signal oscillated by the IC3203 VCO is output as the PB clock (PBCLK). Since the internal switch of the IC3301 varies the capacitance of the capacitor, the switch is turnedoff to minimize the capacitance of the capacitor when the level of the REC CTL is H, namely, in theAudio-Dubbing mode. As a result, the response time is shortened in that mode. The discriminator(DISCRI) compares the 41.85 MHz signal oscillated from the VCO with the other 41.85 MHz signalproduced from the 81 MHz of the main clock in order to detect a difference between the two frequencies.In the general playback mode, the discriminator outputs a Low level signal when the frequency differenceis +1 % or more or a High level signal when the difference is -1 % or more. In the other modes, a Low levelsignal is output when the frequency difference is +3 % or more or a High level signal is output when thedifference is -3 % or more. When the frequency difference is within ±1 % in the general playback mode orwithin ±3 % in the other modes, the output signal has a high impedance. Therefore, a frequency difference,if there is, is roughly corrected.Regarding the signal for the ATF, the frequency component of the ATF pilot signal is extracted from theplayback signal by the BPF and the ATF gain is adjusted by the GCA. Then, the ATF circuit in the IC3201DV EQ detects a tracking difference using the pilot signals of F0, F1 and F2, and data on the detectionresult is transmitted to the servo CPU.

2-4

2.1.4 Explanation of PC terminal and JLIP terminal

P C

JLIP

R X

S Y S C O NC P U

D E C KC P U

G N D

R X

T X

G N D

EDIT

RX

D

TX

D

SR

V_R

X

SR

V_T

X

IC1006Q 1 0 0 1

D 1 0 0 2

IC1001

Q 5 0 2

IC503

IC502

IC501

Q 5 0 1

J503

J507

ED

IT_C

TL

IC1401

Q 1 0 0 8

IC503T X

M A X 3 2 2 1

Fig. 2-1-4 PC terminal and JLIP terminal block diagram

PC Cab le2.5φ 3-Pole Plug

To: PC RS-232C

Fig. 2-1-5 PC cable

4-2 Edi t Cable

N.C.

N.C.

EDITR XTXG N D

G N D

R E M O T E

Remote Pause Jack JLIP Jack

4

3

2

1

2

1

3.5φ, 4-Pole Plug3.5φ, 2-Pole Plug

Fig. 2-1-6 4-2 edit cable

The PC jack (2.5 mm φ, 3 poles) and JLIP jack (3.5 mm φ, 4 poles) are provided as the JLIP terminals ofthis model. Since the IC501 of an RS-232C transceiver is built in the PC terminal, a straight type PC cable(without level converter) can be used for connecting this model with a personal computer. Therefore, astraight type PC cable is contained in the personal computer connecting kit supplied as an accessory orthe HS-V4KIT to be supplied as an optional. Since the JLIP terminal is the same as usual, a personalcomputer can be connected with this model by use of the JLIP-PC cable (QAM0099-002) that internallyincorporates a level converter. However, it is recommended to use the PC terminal for connecting a

2-5

personal computer and to use the JLIP terminals for connecting other JLIP apparatus such as a videodeck, video printer and so on, because such the connection enables the user to perform program editingwith the JLIP video producer.If this model is used for program editing with the JLIP video producer, only the video deck having the JLIPterminal can be connected with it as a recording unit because it has no remote output terminal (editingterminal). Accordingly, neither video deck having the remote pause terminal nor multibrand remotecontroller can be connected with this model. This problem can be solved by use of a special 4-pole-to-2-pole remote cable while connecting the EDIT CTL with a dead pin of the JLIP terminal (except the USversion). When trying to make this connection for program editing with the JLIP video producer, pay heedto the point that it is required to use a special 4-pole-to-2-pole remote cable. If a 2-pole-to-2-pole remotecable is used for connection or a 4-pole-to-2-pole remote cable is revsersely connected, communicationwith a personal computer and editing operation result in failure because the RX pole of the JLIP terminal isgrounded.However, for utilizing the program editing function of this model without use of the JLIP video producer, inother words without connection of a personal computer, either a 4-pole-to-2-pole or a 2-pole-to-2-poleremote cable can be used for connecting a video deck having the remote pause terminal and multibrandremote controller. When a 4-pole plug is inserted into the JLIP jack, the remote pause signal is output fromthe EDIT CTL. On the other hand, when a 2-pole plug is inserted into the jack, the remote pause signal isoutput from the TXD because it is detected that the RX pole is grounded.This model is capable of transferring digital still pictures with the JLIP video capture used together. Theprevious models having the digital still picture output terminal (GR-DVL9000, GR-DVL9500) use theVRAM (field memory) as the capture memory and output digital video data from the TXD through theCAMERA DSP and SYSCON CPU, while the personal computer receives and saves digital data in theDVF format. Differently from this system currently in use, this model outputs DV playback data that issaved in the DRAM from the SRV-TX through the DECK DSP and DECK CPU. At that time, only theimage data is extracted from the DV playback data not to be accompanied with the other data such asaudio data, sub code, etc., and the image data is output as the DV stream data. Receiving the image data,the personal computer (JLIP Video Capture Ver.3.0) manages the whole image data of an album in onefile (extension: **.vna). For saving an image data as an image file, open an album on the personalcomputer and select desirable data, which will be saved as a JPEG, BMP or DVF formatted file when"Save Image As ..." operation is executed.

2-6

2.2 CPU FUNCTIONS2.2.1 SYSCON CPU (IC1001) function1. SYSCON CPU (IC1001) pin functons (1/3)

Pin No. Label In/Out Description1 AU_CMODE Out M clock select for audio AD/DA IC

2 LAMP_ON Out Video light ON/OFF

3 BUS0 In/Out

4 BUS1 In/Out

5 BUS2 In/Out

6 BUS3 In/Out

7 VDD - Power supply

8 VSS - GND

9 BUS4 In/Out GND

10 BUS5 In/Out

11 BUS6 In/Out

12 BUS7 In/Out

13 BUS8 In/Out

14 BUS9 In/Out

15 BUS10 In/Out

16 PWR_CTL Out Power control

17 SRV_RDY In Ready signal from DECK_CPU IC1401

18 BUS11 In/Out

19 BUS12 In/Out

20 BUS13 In/Out

21 BUS14 In/Out

22 BUS15 In/Out

23 MODE0 In GND

24 MODE1 In GND

25 MODE2 In AL3V

26 SRV_CS Out Chip select to DECK_CPU IC1401

27 WB_IR_DET In Flicker detect

28 F/Z_CS Out Chip select to F/Z DRIVER IC4851

29 VDD - Power supply

30 OSCI In System clock (24MHz)

31 OSCO Out System clock (24MHz)

32 VSS - GND

33 MFLD In Field discrimination signal

34 NMI In H: fixed

35 RST In Reset

36 PHOTO_SW In Snap shot switch input

37 V_MUTE Out Video mute

38 JLIP_INT In JLIP interrupt

39 VD In Vertical sync signal

40 OMT In EIS data readout timing

41 KASHA_CTL In Not used

42 MENU_P_A In Menu dial pulse

43 CFRP In Frame reference pulse

Address/Data MPX BUS 16bits CAMERA_DSP IC4301

Address/Data MPX BUS 16bits CAMERA_DSP IC4301

Address/data MPX BUS 16bits CAMERA_DSP IC4301

Table 2-2-1 SYSCON CPU (IC1001) pin functions (1/3)

2-7

• • • • SYSCON CPU (IC1001) pin functions (2/3)

Pin No. Label In/Out Description44 RTC_INT In Clock 1 sec. Interrupt

45 AFBEND In AF data readout timing

46 VF_MONI Out VF/MONI select signal

47 LCD_LOAD Out LCD data load pulse

48 VF_CTL Out VF_REG4.8V ON/OFF control

49 EEPROM_CS Out Chip select signal to EEPROM IC1003

50 VDD Out Power supply

51 TIMER_OUT - Not used

52 TALLY Out Tally lamp

53 MONI_CTL Out MONI_LCD back light control

54 MONI_UD Out MONI_LCD L/R UP/DOWN reverse control

55 REMOTE In Remote control input

56 S_DT_IN In Serial data input from DECK_CPU EEPROM RTC

57 S_DT_OUT In Serial data output to DECK_CPU TG/VDRIV CDS/AGC/ADC EEPROM RTC

58 S_CLK Out Serial clock

59 - - Not used

60 AFZ_DATA Out Serial data output to AUDIO FZ_MDA DAC/EVR

61 AFZ_CLK Out Serial data output to AUDIO FZ_MDA DAC/EVR

62 RXD Out RS232C data input

63 TXD In RS232C data output

64 AUDIO_CS Out Chip select signal to AUDIO IC2200

65 LCD_SO In Serial data input from LCD EEPROM

66 LCD_SI Out Serial data output to LCD EEPROM

67 LCD_CLK Out Serial clock output to LCD EEPROM

68 VDD - Power supply

69 VSS - GND

70 AVSS - GND

71 VRefL - Reference power supply

72 BATT_CHK In Battery DC input

73 KEY_A In Deck operation switch input

74 KEY_B In Camera operation switch input

75 ZOOM_SW In Zoom switch input

76 IR_AD In AWB IR sensor AD input

77 HALL_AD In Iris hall generator AS input

78 Z_PTR_AD In ZOOM position sensor AD input

79 F_PTR_AD In FOCUS position sensor AD input

80 TG_CS Out Chip select signal to TG/V.DRV IC5501

81 - - Not used

82 - - Not used

83 - - Not used

84 BATT_SW In DC pulg installation detect

85 MONI_RVS In LCD reverse switch input

86 VRefH - ADC power supply (REG3V)

Table 2-2-1 SYSCON CPU (IC1001) pin functions (2/3)

2-8

•••• SYSCON CPU (IC1001) pin functions (3/3)

Pin No. Label In/Out Description87 AVDD - Power supply

88 - - Not used

89 SRV_RST Out Reset signal to DECK_CPU IC1401

90 OEM_REG5_CTL Out Not used

91 MENU_SET_SW In Menu set switch input

92 RTC_CS Out Chip select signal to RTC IC1004

93 DAC_CS Out Chip select signal to DAC/EVR IC3503

94 CLWE Out Write enable

95 CHWE Out Write enable

96 CRE In Read enable

97 CALE Out Address latch enable

98 VDD - Power supply

99 VSS - GND

100 SEL_SW In Snap shot mode switch

101 TRIG_SW In Trigger switch

102 DIAL_MANU In Dial MANUAL

103 DIAL_AUTO In Dial AUTO

104 DIAL_OFF In Dial OFF

105 DIAL_PLAY In Dial PLAY

106 EJECT_SW In EJECT switch detect

107 CAS_SW In Cassette switch detect

108 MONITOR_SW In Monitor OPEN/CLOSE switch detect

109 - - Not used

110 MENU_P_B In Menu dial pulse

111 LCD_CS1 Out Chip select signal to LCD EEPROM IC7603

112 RESERVE - L: fixed

113 - - Not used

114 F/Z_RST Out Reset signal to F/Z DRIVER IC4851

115 K_CTL Out Shutter sound oscillator control

116 - - Not used

117 KRST/CLR Out Shutter sound reset/clear signal to CAMERA_DSP IC4301

118 - - Not used

119 VDD(VPP) - Power supply

120 IRIS_O/C Out Iris OPEN/CLOSE

121 CDS_CS Out Chip select signal to CDS/AGC/AD IC5601

122 TG_RST Out Reset signal to TG/V.DRV IC5501

123 S_MUTE Out Shutter sound mute

124 WEN In Memory write timing at slow shutter

125 STIL_PLS In Odd/Even field discrimination signal at slow playback (FRAME ADVANCE)

126 FADE_H Out Fade in/out pulse (Fade last high)

127 AFADER Out Fade in/out pulse (Fade execution: high)

128 A_MUTE Out Audio mute

Table 2-2-1 SYSCON CPU (IC1001) pin functions (3/3)

2-9

2.2.2 DECK CPU (IC1401) function1. DECK CPU (IC1401) pin functions (1/5)

Pin No. Label In/Out Description

1 CAP_BRK Out Capstan motor brake control27 LD_ON Out Loading motor ON/OFF control14 ANA_CS Out Chip select signal to DV_ANA IC330128 OSD_CS Out Chip select signal to OSD IC10022 VSS - GND

29 MIC_CTL Out Power supply control to MIC3 PHY_PD Out Power down control to PHY IC3101

61 PHY_RST Out Reset output to PHY IC310115 PHY_CNA In IEEE1394 connection detect (Connect: L)45 ANA_PD Out Power down control to DV_ANA IC330116 VMUTE_IN In Video mute input46 - - Not used4 - - Not used

30 VDDH - Power supply (REG_3V)31 - - Not used62 - - Not used5 REWSEL Out Read/write select signal of Bus

47 AS Out Address strobe signal of Bus17 - - Not used63 - - Not used49 - - Not used32 VSS - GND18 - - Not used79 - - Not used6 - - Not used

48 - - Not used64 DSYSCLK - Not used7 DRWSEL - Not used

65 DAS - Not used19 VDDB - Power supply (REG_3V)33 ADM15 In/Out20 ADM14 In/Out82 ADM13 In/Out50 ADM12 In/Out66 ADM11 In/Out8 ADM10 In/Out

67 ADM9 In/Out51 ADM8 In/Out34 VSS - GND9 ADM7 In/Out

35 ADM6 In/Out21 ADM5 In/Out52 ADM4 In/Out10 ADM3 In/Out36 ADM2 In/Out22 ADM1 In/Out23 ADM0 In/Out

Address/Data MPX BUS 16bits DECK_DSP IC3001 DVEQ IC3201

Address/Data MPX BUS 16bits DECK_DSP IC3001 DVEQ IC3201

Table 2-2-2 DECK CPU (IC1401) pin functions (1/5)

2-10

•••• DECK CPU (IC1401) pin functions (2/5)

Pin No. Label In/Out Description

11 VDDB - Power supply (REG_3V)37 DK In Servo CPU ready signal (Low: Deck mode)24 RE Out Read enable signal38 WE1 - Not used12 WE0 Out Write enable signal40 PVDD - Power supply (REG_3V)53 PVSS - GND56 MMOD1 -54 MMOD0 -55 RESET In Reset input from SYSCON CPU IC100170 FRQS - L: fixed71 VSS - GND69 EXMOD1 - H: fixed68 EXMOD0 - H: fixed72 OSCI In 27MHz clock input form TG/V.DRV IC550188 OSC0 - Not used86 VDDH - Power supply (REG_3V)87 SYSCLK - Not used85 EQ_CS Out Chip select signal to DV_EQ IC3201

104 DV_CS Out Chip select signal to DECK_DSP IC3001102 CS1 - Not used103 CS0 - Not used101 VDD - Power supply (REG_3V)100 STIL_PLS Out Odd/Even field discrimination signal at slow playback (FRAME ADVANCE)84 V_PB_L Out Video track area recording off signal99 DV_RST Out Reset signal output to DECK_DSP IC300183 EQ_TRST Out Reset signal output to DV_EQ IC3201 (for Boundly scan)

120 EQ_RST Out Reset signal output to DV_EQ IC3201118 VSS - GND119 HID3 Out Head switch pulse (control of recording current measure circuit)116 REC_I Out ON/OFF control for recording circuit to PRE/REC IC117 PBH Out ON/OFF control for playback circuit to PRE/REC IC134 REEL_LED Out Reel sensor LED control135 REC_SAFE In REC safty switch133 VDDH - Power supply (REG_3V)136 CAM2 In132 CAM1 In148 CAM0 In149 AVSS - GND152 - - Not used150 - - Not used151 - - Not used147 - - Not used

Control port for FLASH CPU

Mechanism position detect from rotary encoder

Table 2-2-2 DECK CPU (IC1401) pin functions (2/5)

2-11

•••• DECK CPU (IC1401) pin functions (3/5)

Pin No. Label In/Out Description

164 - - Not used166 - - Not used167 - - Not used163 - - Not used168 - - Not used165 - - Not used183 BCID3 In181 BCID2 In184 BCID1 In200 DEW_SENS In Dew sensor detect182 E_SENS In End sensor detect199 S_SENS In Start sensor detect198 VREFH - Reference voltage216 AVDD - Power supply (REG_3V)214 ADTRG In H: fixed239 NMI In H: fixed213 VSS - GND240 - - Not used197 - - Not used227 - - Not used212 - - Not used226 DV_INT In DV_DSP interrupt signal196 DRAM_PG In Drum PG238 DRAM_FG In Drum FG180 MSELECT In DECK_CPU chip select input form SYSCON CPU IC1001225 VDD Power supply (REG_3V)195 MDA_CS Out Chip select signal to MDA IC1601237 SRV_RDY Out DECK_CPU ready signal output to SYSCON CPU IC1001179 AGC_RST Out Video output clamp control to A/V OUT SECTION211 TRIG_OUT Out Remote pause output210 - - Not used236 - - Not used194 ADC_PWD1 Out D/A power control to AUDIO AD/DA IC2101 (power down: L )224 ADC_PWD0 Out A/D power control to AUDIO AD/DA IC2101 (power down: L)209 VSS - GND235 ADC_DEM1 Out178 ADC_DEM0 Out223 - - Not used193 - - Not used208 - - Not used

Sampling frequency select to AUDIO AD/DA IC2101(ADC_DEM0/ADC_DEM1:frequency L/L:44.1k, L/H:48k, H/L:OFF, H/H:32k)

Cassette tape ID board information

Table 2-2-2 DECK CPU (IC1401) pin functions (3/5)

2-12

• • • • DECK CPU (IC1401) pin functions (4/5)

Pin No. Label In/Out Description

162 - - Not used222 - - Not used177 - - Not used234 - - Not used192 VDDH - Power supply (REG_3V)207 HID Out Head switch pulse output176 A_PLL - Not used233 V_PLL - Not used191 DRUM_REF Out Drum offset voltage output to MDA IC1601221 CAP_REF Out Capstan offset voltage output to MDA IC1601175 - - Not used232 - - Not used159 - - Not used220 - - Not used206 VSS - GND231 TR In HID reference (Drum 150Hz reference)190 FR In Frame pulse from DECK_DSP IC3001204 DV_INT In DV_DSP interrupt signal174 SPA In Pulse for ATF sample219 HID_IN In Head switch pulse input205 VDD - Power supply (REG_3V)230 S_REEL In SUP reel pulse189 T_REEL In TU reel pulse218 TR In HID reference (Drum 150Hz reference)173 CAP_FG In Capstan FG229 DRUM_FG In Drum FG203 - - Not used201 DRUM_FG In Drum FG187 TAPE_LED Out Tape sensor LED control185 VSS - GND188 VD In Vertical reference pulse form CAMERA_DSP IC4301186 - - Not used171 - - Not used169 - - Not used172 - - Not used170 VDD - Power supply (REG_3V)158 - - Not used154 - - Not used156 - - Not used153 - - Not used157 - - Not used155 VSS - GND

Table 2-2-2 DECK CPU (IC1401) pin functions (4/5)

2-13

•••• DECK CPU (IC1401) pin functions (5/5)

Pin No. Label In/Out Description

140 - - Not used138 - - Not used142 - - Not used139 - - Not used141 - - Not used137 - - Not used124 VDDH - Power supply (REG_3V)122 EEP_CLK - Not used123 EEP_OUT - Not used121 EEP_IN - Not used125 EEP_CS - Not used106 VPP - Power supply (REG_3V)107 BR - H: fixed105 VSS - GND109 ANA_CLK Out Serial clock to DV_ANA IC3301108 ANA_IN Out Serial data bus output to DV_ANA IC330193 ANA_OUT In Serial data bus input from DV_ANA IC330191 MDA_CLK Out Serial clock from MDA IC160194 MDA_IN Out Serial bus data output from MDA IC160190 VDD Power supply (REG_3V)92 MDA_OUT In Serial bus data input from MDA IC160189 SYS_CLK In Serial clock from SYSCON CPU IC100178 SYS_IN Out Serial bus data output to SYSCON CPU IC100174 SYS_OUT In Serial bus data input from SYSCON CPU IC100176 - - Not used73 VSS - GND77 TXD Out RS232C output59 RXD In RS232C input75 OSD_CLK Out Serial clock to OSD IC100258 OSD_DATA Out Serial bus data to OSD IC100260 - - Not used57 MIC_SCL Out Serial clock for MIC43 VDDH Power supply (REG_3V)42 MIC_SDA In Serial data fro MIC44 - - Not used41 - - Not used

Table 2-2-2 DECK CPU (IC1401) pin functions (5/5)

2-14

2.2.3 MDA IC (IC1601) function1. MDA IC (IC1601) pin locations

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

41424344454647484950515253545556

16151413121110987654321 17 18 19 20

D.v

NC

D.W NC

D.G

ND

NC

L.F

WD

FG

ND

2L.

GN

DL.

RE

VC

.GN

DL.

UN

RE

GN

CC

.U

D.U

FG

ND

1

NC

C.V NC

C.W

40

39

38

37

C.PCI

C.VSC.SDC.VCCC.FG+C.FG-C .FGOUTC.FGSOUTC.HU+C.HU-C.HV+C.HV-C . H W +C.HW-C.UNREGC.VM

57585960

D.D

ET

EC

TT

ES

T1

D.P

CV

D.P

CI

D.C

L

GN

D2

VR

EG

DIN

CS

CLK

C.C

OM

C.B

UC

.BR

KC

.RC

C

D.E

CD

.EC

R61

62

63

64

D.PG-D.FGPG+

D.FG-

D.VSG N D 1D.UIND.VIN

D.WIND.COM

D.SLD.ISETL.REF

D.UNREGD.VM

D.FGOUTD.FGSOUT

N CN C

C.PCV

C.ECR

C.E

CC

.CL

D.O

SC

TE

ST

2

D .PGSOUTD.PGOUT

N CN C

Fig. 2-2-3 MDA IC (IC1601) pin locations

2-15

2. MDA IC (IC1601) capstan servo section block diagram

DR

IVE

SIG

NA

L M

IXIN

G

UP

PE

R/L

OW

ER

DIV

ISIO

N

35

V C C

C.HU+

C.UNREG

C.VM

C.U

C . W

C.V

C.GND

REG_4.8VT O R Q U E

CTL

C.FG−

C.FG+

CAP_FGC.FGSOUT

C A P . M

D I R E C T I O N

C.FGOUT

T S D

L.SATURATION PREVENT

U.SATURATION PREVENT

C.PCI

C.PCV

D C - D C

P O W E RSAVE

PW.SAVE

G N D

C.U C.V C.W

C.CL

30

28

26

25

43

41

40

42

33

34

32

31

69

37

38

39

13

20

18

16

23

24

C.F/R

C.HU-

C.HV+

C.HV-

C . H W +

C.HW-

H A L L

H A L L

H A L L

C.VM

C.EC

C.MODE

C.VS

C.ECR

C.ECCAP_REF

R IPPLEC A N C E L

C.RCC

C U R R E N TLIMIT

C.MODE

B R A K EC.BRK

C A P . M

REG_4.8V

44

SHORT CIRCUIT DETECT

C.U C.V C.W

C.U C.V C.W

C.U C.V C.W

29

27

Fig. 2-2-4 MDA IC (IC1601) capstan servo section block diagram

2-16

3. MDA IC (IC1601) drum servo section block diagram

DR

IVE

SIG

NA

LLO

GIC

UP

PE

R/L

OW

ER

DIV

ISIO

N

3 5V C C

D.UIN

D.VIN

D . W I N

D . C O M

D.SL D. ISETD . U N R E G

D.VM

D.U

D . W

D.V

D . G N D

S T A R T

O S C

B R A K E

D.ECR

D.ECD R U M _ R E F

REG_4.8V

T O R Q U EC T L

D.BRK

CURRENT FEED BACK

D.F

G−

D.P

G−

D.F

GP

G+

D R U M _ F G D R U M _ P G

D.F

GS

OU

T

D.P

GS

OU

T

D .PG.SM

D R U M . M

D.OSC

S L O P E

D.F

GO

UT

D.P

GO

UT

C U R R E N TLIMIT

T S D

D E T E C T

SE

LEC

T L

OG

IC

L .SATURATION PREVENT

U.SATURATION PREVENT

D.VM

D.DETECT

E R R O R A M P

D.PCI

D.PCVD C - D C

V R E GP O W E R

SAVE

P W . S A V E

D.VS

G N D

D.U D.V D.W

D.U D.V D.W

D.U D.V D.W

D.CL

70

71

72

73

74 75

58

57

52

53

54

65 64 66 67 63 62 6961 50

68

56

55

7

5

3

2

78

77

Fig. 2-2-5 MDA IC (IC1601) drum servo section block diagram

2-17

4. MDA IC (IC1601) interface section block diagram

14

L.UNREG

L.GND

L O A D I N GM O T O R

CO

NT

RO

L LO

GIC

G N D

9

11D

0

12

T S D

76

L.REV

L.FWD

L.REF

L.FIN

L.RIN

D A T A - L A T C HSHIFT

R E G I S T E R

D1

D2

D3

D4

D5

D6

D7

6 947 49 48

CSDINCLK

C.F/R

C.MODE

D.PG.SM

D.BRK

L.FIN

PW_SAVE

59 60 35

TEST1 TEST2 VCC

Fig. 2-2-6 MDA IC (IC1601) interface section block diagram

2-18

5. MDA IC (IC1601) pin functions (1/2)

Pin No. Label In/Out Description

1 FGND1 - Sub ground of IC

2 D.U Out Output of motor drive for Drum Motor section

3 D.V In Output of motor drive for Drum Motor section

4 NC - Not used

5 D.W - Output of motor drive for Drum Motor section

6 NC - Not used

7 D.GND - Ground for the Drum Motor section (Current detect register)

8 NC - Not used

9 L.FWD Out Output of motor drive for Loading Motor section

10 FGND2 - Sub ground of IC

11 L.GND - Ground for the Loading Motor section

12 L.REV Out Output of motor drive for Loading Motor section

13 C.GND - Ground for the Capstan Motor section (Current detect register)

14 L.UNREG - Power supply for Loading Motor section (UNREG)

15 NC - Not used

16 C.U Out Output of motor drive for Capstan Motor section

17 NC - Not used

18 C.V Out Output of motor drive for Capstan Motor section

19 NC - Not used

20 C.W Out Output of motor drive for Capstan Motor section

21 NC - Not used

22 NC - Not used

23 C.VM In VM of Capstan Motor section

24 C.UNREG - Power supply for Capstan Motor section (UNREG)

25 C.HW- In

26 C.HW+ In

27 C.HV- In

28 C.HV+ In

29 C.HU- In

30 C.HU+ In

31 C.FGSOUT Out Output of FG schmitt for Capstan Motor section

32 C.FGOUT Out Output of FG amp. for Capstan Motor section

33 C.FG- In

34 C.FG+ In

35 C.VCC - VCC of BIP control section

36 C.SD Out Short detect output of Capstan Motor section

37 C.VS In Motor power supply control of Capstan Motor section

38 C.PCV In Output of saturation prevent phase compensation for Capstan section (upper side)

39 C.PCI In Output of saturation prevent phase compensation for Capstan section (lower side)

40 C.ECR In Input of reference torque control for Capstan Motor section

FG input of Capstan Motor section

Hall input of Capstan Motor section

Table 2-2-3 MDA IC (IC1601) pin functions (1/2)

2-19

•••• MDA IC (IC1601) pin functions (2/2)

Pin No. Label In/Out Description

41 C.EC In Input of torque command control for Capstan Motor section

42 C.CL In Input of current limmit for Capstan Motor section

43 C.RCC In Ripple cancel variable terminal for Capstan Motor section (Register connect)

44 C.BRK In Brake input of Capstan Motor section (H: Brake)

45 C.BU - Not used

46 C.COM - Not used

47 CLK In Clock signal input

48 CS In Chip select signal input

49 DIN In Serial data input

50 V.REG Out Internal reference voltage output

51 GND2 - Ground for logic system

52 D.EC In Input of torque command control for Drum Motor section

53 D.ECR In Input of reference torque control for Drum Motor section

54 D.CL In Input of current limmit for Drum Motor section

55 D.PCI In Output of saturation prevent phase compensation for Drum section (upper side)

56 D.PCV In Output of saturation prevent phase compensation for Drum section (lower side)

57 D.OSC In Starting signal oscillation for Drum Motor section

58 D.DETECT In Detect mode time setting for Drum Motor section

59 TEST1 - Not used

60 TEST2 - Not used

61 D.PGSOUT Out Output of PG schumitt for Drum Motor section

62 D.PGOUT Out Output of PG amp. for Drum Motor section

63 D.PG- In Input of PG for Drum Motor section

64 D.FGPG+ In Input of FG/PG common for Drum Motor section

65 D.FG- In Input of FG for Drum Motor section

66 D.FGOUT Out Output of FG amp. for Drum Motor section

67 D.FGSOUT Out Output of FG schumitt for Drum Motor section

68 D.VS Out Control of motor power supply for Drum Motor section

69 GND1 - Ground for BIP control section

70 D.UIN In

71 D.VIN In

72 D.WIN In

73 D.COM - Middle point of motor for Drum Motor section

74 D.SL - Shape of slope waveform for Drum Motor section

75 D.ISET - Current control of SL terminal for Drum Motor section (Resister connect)

76 L.REF - Setting of output voltage for Loading Motor section

77 D.UNREG - Power supply for the Drum Motor section (UNREG)

78 D.VM Out VM of Drum Motor section

79 NC - Not used

80 NC - Not used

Input of BEMF comparator for Drum Motor section

Table 2-2-3 MDA IC (IC1601) pin functions (2/2)

2-20

2.2.4 CDS AGC AD IC (IC5601) function1. CDS AGC AD IC (IC5601) pin locations and block diagram

DV

SS

DV

SS

SD

AT

A

SC

K

CS

NC

NC

AV

DD

AV

SS

D 0

D 2

D 3

D 4

D 5

D 6

D 8

D 1

N C

BIAS

V R T

V R M

V R B

A V D D

A V S S

T E S T C

TESTY

C D S I N

A V D D

A V S S

DV

DD

AD

CLK

OB

P

SP

SIG

AV

SS

AV

DD

NC

CLP

VR

M2

1 5 1314161718192021222324

25

26

27

28

29

30

31

32

33

34

35

36

46 4847454443424140393837

12

11

10

9

8

7

6

5

4

3

2

1 P B L K

D 7

D 9

OE

DV

SS

SP

BLK

N C

AV

DD

AV

SS

DV

DD

C D S

Out

put L

atch

10bi tA /D

SerialI/F

A G C

GainSelect

C lamp

BIAS

Fig. 2-2-7 CDS AGC AD IC (IC5601) pin locations and block diagram

2-21

2. CDS AGC AD IC (IC5601) pin function

Pin No. Label In/Out Description1 PBLK In Pre-blanking pulse input2 D0 Out (LSB)3 D1 Out4 D2 Out5 D3 Out6 D4 Out7 D5 Out8 D6 Out9 D7 Out

10 D8 Out11 D9 Out (MSB)12 NC - Not used13 OE In Digital output enable control14 DVSS - Ground for the digital system15 DVDD - Power supply for the digital system16 ADCLK In A/D converter clock input17 OBP In Optical balck clamp pulse input18 SPBLK In Pre-charge level sample and hold pulse for CDS19 SPSIG In Level sample and hold pulse for CDS20 AVSS - Ground for the analog system21 AVDD - Power supply for the analog system22 NC - Not used23 CLP - Clamp voltage24 VRM2 - Reference voltage25 AVSS - Ground for the analog system26 AVDD Out Power supply for the analog system27 CDSIN In CDS input28 TESTY In Test signal input - Y29 TESTC In Test signal input - C30 AVSS - Ground for the analog system31 AVDD - Power supply for the analog system32 VRB - Reference voltage33 VRM - Reference voltage34 VRT - Reference voltage35 BIAS - Internal bias36 NC - Not used37 AVSS - Ground for the analog system38 AVDD - Power supply for the analog system39 NC - Not used40 NC - Not used41 AVDD - Power supply for the analog system42 AVSS - Ground for the analog system43 CS In Serial interface chip select input44 SCK In Serial clock input45 SDATA In Serial data input46 DVDD - Power supply for the digital system47 DVSS - Ground for the digital system48 DVSS - Ground for the digital system

Digital output

Table 2-2-4 CDS AGC AD (IC5601) pin function

2-22

2.2.5 B/W LCD driver IC (IC7001) function (for GR-DVF11U)1. B/W LCD DRIVE IC (IC7001) pin locations and block diagram

R E F _ G N D

V _ S Y N C

H _ S Y N C

B L A C K _ L E V E L

V B A T

V D D H

S M C O M P

S S T A R T

H_SKIPPING

SLE

EP

OS

D_I

N

A_G

ND

VID

EO

_IN

CLA

MP

PLL

_FIL

TE

R

525/

625

HO

DL_

SE

L

GA

MM

A

OK

BR

IGH

TN

ES

S

VB

G

BL

BL_

GN

D

MV

DD

VID

CH

VID

LC

VID

L

RE

NO

RE

NE

V C K

V P L

H O D L

V _ C O M

V E E

V D D

V S S

V _ R E F

H P L

H C K

15

13

14

16

17

18

19

20

21

22

23

24

252627282930313233343536

46

48

47

45

44

43

42

41

40

39

38

37

121110987654321

GA

IN

SF

LTR

D_G

ND

A_G

ND

P D R

VIDH

S M G N D

VHIO_SEL

S M O U T

D CRestore

O S DLevelDetect

SyncSeparator

PLL

Backl ightCurrentContro l

D C - D CConver toer

T imingGenerator

V ideoAdjust

1/13

Hsync

32fh

Vsync

416fh

32 fh Ramp

VideoA m p

VideoA m p

Blkg

Wh i te

Band GapReference

Fig. 2-2-8 B/W LCD DRIVE IC (IC7001) pin locations and block diagram

2-23

2. B/W LCD driver IC (IC7001) pin function

Pin No. Label In/Out Description1 SLEEP In Logic level input. A logic low sets the IC into the sleep mode2 OSC_CTL - Not used (L: fixed)3 OSD_IN - Not used (L: fixed)4 A_GND - Ground for the analog sections and signals5 VIDEO_IN In Input for standard level monochrome video, 525 or 625 lines6 CLAMP - Clamp capacitor, to ground, for the video black level clamp7 PLL_FILTER - Filter pin for the internal horizontal PLL8 GAIN In DC control for the gain of the video signal path9 SYFILTER - Filter pin for the sync separator

10 525/625 In Video system select (L: 525 line, H: 625 line)11 D_GND - Ground for the digital sections and signals12 A_GND - Ground for the analog sections and signals13 PDR Out Power down reset output to the LCD panel (Active Low)14 VIDH Out Upper video drive signal to the LCD panel15 VCK Out Vertical clock output to the LCD panel16 VPL Out Vertical start pulse output to the LCD panel17 HODL Out Column inversion control output to the LCD panel18 V_COM Out Internally generated supply for the LCD panel (5.8V)19 VEE Out Internally generated supply for the LCD panel (2.0V)20 VDD Out Internally generated supply for the LCD panel (9.0V)21 VSS Out Reference ground for the LCD panel22 V_REF Out Internally generated supply for the LCD panel (VBat/2V) 23 HPL Out Horizontal start pulse output to the LCD panel24 HCK Out Horizontal clock output to the LCD panel25 RENE Out Even Row enable output to the LCD panel26 RENO Out Odd Row enable output to the LCD panel27 VIDL Out Lower video drive signal to the LCD panel28 VIDLC - Connect to VIDHC through a compensation capacitor29 VIDHC - Connect to VIDLC through a compensation capacitor30 BACK_LEVEL In DC control to adjust the video output black level31 BL_GND - Ground pin for the backlight LED current32 BL - Current sink for the backlight LED current33 VBG - Output of the bandgap reference34 BRIGHTNESS Out DC control for the brightness of the backlight LED35 OK - Not used36 NC - Not used37 SMPFILTER - Not used38 SSTART - Not used39 SMCOMP - Not used (H: fixed)40 VDDH - Internally generated supply voltage (11.0V)41 SMGND - Ground pin for the DC/DC converter42 SMOUT - Not used43 VBAT - Power supply input (VF_4.8V)44 ANALOG_VBAT - Power supply45 H_SYNC - Not used46 V_SYNC - Not used47 VHIO_SEL - 45, 46 pins I/O control (L: OUT, H: INPUT)48 REF_GND - Ground for the DC/DC converter

Table 2-2-5 B/W LCD driver IC (IC7001) pin function

VICTOR COMPANY OF JAPAN, LIMITED

Printed in Japan9909 (TM1)