HYBRID SC-I B T L -V H EFFICIENCY SWITCHED … buck and boost converter topologies due to their...

Transcript of HYBRID SC-I B T L -V H EFFICIENCY SWITCHED … buck and boost converter topologies due to their...

HYBRID SC-INDUCTIVE BASED TOPOLOGIES FOR LOW-VOLUME HIGH-

EFFICIENCY SWITCHED-MODE POWER SUPPLIES

by

Seyed-Behzad Mahdavikhah-Mehrabad

A thesis submitted in conformity with the requirements

for the degree of Doctor of Philosophy

Graduate Department of Electrical and Computer Engineering

University of Toronto

© Copyright by Behzad Mahdavikhah 2014

ii

Hybrid SC-Inductive Based Topologies for Low-Volume High-

Efficiency Switched-Mode Power Supplies

Seyed-Behzad Mahdavikhah-Mehrabad

Doctor of Philosophy

Graduate Department of Electrical and Computer Engineering

University of Toronto

2014

Abstract

Switched-mode power supplies (SMPS) are widely used as the voltage or current regulators for

electronic devices. The most commonly used SMPS are inductive converters based on

conventional buck and boost converter topologies due to their simplicity and relatively high

power density and efficiency. However, in applications with large voltage difference between

their inputs and outputs, these converters suffer from excessive losses and increased volume due

to more demanding filtering and also cooling requirements. Therefore strong and ever increasing

demands for developing smaller and more efficient SMPS with high conversion ratios exist.

In this work two new converter topologies suitable for applications with large input-to-output

voltage difference are introduced for both input voltage step-down and step-up in two different

types of applications, i.e. for dc-dc converters and rectifiers with power factor correction. These

converters are developed based on the concept of merging Switched-capacitor (SC) and

inductive based converter stages by means of newly emerged digital controllers, improving

iii

efficiency and reducing the overall volume of the converter. Hence, the benefits of high power

density SC-based converters are exploited and at the same time the input-to-output voltage ratio

for the inductive stage is reduced improving its power density and efficiency. Compared to two-

stage solutions, by merging SC and inductive based stages, switches between two stages are

shared, reducing conduction losses, intermediate/flying capacitors are eliminated and controllers

are unified.

The buck-based, voltage step-down solution combines a capacitive divider and an interleaved

buck to reduce the volume of multi-phase step-down converters. Experimental results obtained

with a 7V-to-1V, 10A, 1 MHz prototype demonstrate that the merged capacitor converter has

15% smaller inductor, 13% smaller output capacitor, up to 35% lower power losses and 15%

shorter settling time after transients.

In the boost-based voltage step-up solution, the improvements are achieved by replacing the

output capacitor of the boost converter with a non-symmetric active capacitive divider, with a

2:1 division ratio, effectively providing four-level converter behavior. Experimental results

obtained with a 350 W, 200 kHz, universal input voltage (85Vrms - 265Vrms) PFC prototype

demonstrate 66% reduction of boost converter inductor and up to 10% improvement of

efficiency.

iv

Acknowledgements

I wish to express my deepest appreciation to my advisor, Professor Aleksandar Prodić, for

accepting me into the power electronics group and his invaluable advice, support and

encouragement throughout my PhD studies. Professor Prodić's knowledge, vision and passion for

research along with his dedication and unique personality provided me a mentorship truly

beyond my expectations. I have thoroughly enjoyed working in the Laboratory for Power

Management and Integrated SMPS under his supervision.

I would also like to thank my dissertation committee members, Dr. Óscar García, Dr. Reza

Iravani, Dr. Peter Lehn and Dr. Zeb Tate for their insight and their valuable and thoughtful

feedbacks.

Grateful regards to all my friends and colleagues in the Laboratory for Power Management and

Integrated SMPS, Amir Parayandeh, SM Ahsanuzzaman, Aleksandar Radić, Zdravko Lukić,

Conny Huerta Oliviares, Massimo Tarulli, Mahmoud Shousha, Adrian Straka, Parth Jane, Tim

Mcrae, Amr Amin and Nenad Vukadinovic who made this journey an enjoyable one through

their friendship and also collaborations and discussions on numerous projects.

My deepest gratitude to my parents, my grandmother and my sister for their invaluable support

in many significant ways that can never be matched with anything. I will always be grateful for

their support.

v

Finally I would like to acknowledge the support of Department of Electrical and Computer

Engineering at the University of Toronto. Financial support from the Energy System Department

is gratefully acknowledged.

vi

Contents

Chapter 1 Introduction...............................................................................................................1

1.1 Motivation ............................................................................................................................1

1.2 Thesis Objectives .................................................................................................................5

1.3 Thesis Organization and Contributions ...............................................................................6

1.4 Thesis Outline ......................................................................................................................8

References .................................................................................................................................10

Chapter 2 Background and Previous Art .................................................................................11

2.1 Topology Limits.................................................................................................................12

2.2 Reactive Components Volume ..........................................................................................13

2.2.1 Inductor Volume ....................................................................................................13

2.2.2 Output Capacitor Volume ......................................................................................14

2.3 Converter Losses ................................................................................................................15

vii

2.4 Volume reduction techniques ............................................................................................16

2.4.1 Increasing Switching Frequency ............................................................................16

2.4.2 Interleaving techniques ..........................................................................................18

2.4.3 Non-linear Controllers ...........................................................................................18

2.4.4 Ripple Cancellation ................................................................................................19

2.5 Switched Capacitor Converters..........................................................................................19

2.6 Two-Stage Converter topologies .......................................................................................22

2.7 Topologies Merging Inductive-based Solutions and Capacitive Attenuator .....................24

2.8 References ..........................................................................................................................26

Chapter 3 Digitally Controlled Multi-Phase Buck-Converter with Merged Capacitive

Attenuator ..................................................................................................................................32

3.1 Introduction ........................................................................................................................33

3.2 Principle of Operation and System Description.................................................................35

3.2.1 Steady-state operation and elimination of the output capacitor of the SC stage ...37

3.2.2 Transient and low-input mode ...............................................................................42

3.3 Practical Implementation ...................................................................................................44

3.3.1 Output filter reduction............................................................................................44

3.3.2 Component voltage ratings and start up transient ..................................................45

3.3.3 Conduction losses and switch selection .................................................................49

3.4 Experimental system and results ........................................................................................50

3.5 Conclusions ........................................................................................................................57

3.6 References ..........................................................................................................................57

Chapter 4 Low-Volume PFC Rectifier Based On Non-Symmetric Multi-Level Boost

Converter ...................................................................................................................................60

4.1 Introduction ........................................................................................................................61

viii

4.2 Principle of Operation of The Non-Symmetric Multi-Level Boost-Based (NSMB)

Front end PFC Stage ..........................................................................................................65

4.2.1 Non-symmetric active capacitive divider ..............................................................68

4.2.2 Centre tap voltage balancing and isolated downstream stages ..............................78

4.3 Practical Controller Implementation ..................................................................................80

4.3.1 Input current and bus voltage regulator .................................................................80

4.3.2 Mode selector and sampling sequence generator...................................................83

4.3.3 Centre-tap voltage regulator ..................................................................................88

4.3.4 Design Tradeoffs ....................................................................................................91

4.3.5 Extension to Higher Power Levels ........................................................................92

4.4 Experimental System and Results ......................................................................................93

4.5 Conclusions ......................................................................................................................107

4.6 References ........................................................................................................................108

Chapter 5 ....................................................................................................................................112

Conclusions and Future Work .....................................................................................................112

5 113

5.1 Digitally Controlled Multi-Phase Buck-Converter with Merged Capacitive Attenuator 113

5.1.1 Conclusions ..........................................................................................................113

5.1.2 Future Work .........................................................................................................114

5.2 Low-Volume PFC Rectifier Based On Non-Symmetric Multi-Level Boost Converter ..115

5.2.1 Conclusions ..........................................................................................................115

5.2.2 Future Work .........................................................................................................117

5.3 References ........................................................................................................................118

Appendix A Analysis of Conduction losses for optimized design of switching

components .............................................................................................................................119

ix

A.1 Analytical comparison of Conduction losses ...................................................................120

A.2 References ........................................................................................................................122

x

List of Tables

Table 3.1. MSCB converter component voltage ratings (assuming small ac ripple). .................. 46

Table 3.2. MSCB and multi-phase buck filter components parameters. ...................................... 51

Table 4.1: Comparison of NSMB Converter Parameters with Boost and 3-level PFC ................ 93

xi

List of Figures

Figure 1.1. Comparison of overall area occupied by power supplies (shown in red boxes) to the

overall PCB area for, a) a battery operated Google Galaxy Nexus 7 Tablet [4]; b) an ac powered

Panasonic VIERA TX-P50VT30E plasma TV [5]. ........................................................................ 3

Figure 1.2. Block diagram of a 2-phase merged switch capacitor buck (MSCB) converter and its

digital controller. ............................................................................................................................. 6

Figure 1.3. Block diagram of the non-symmetric multi-level buck (NSMB) based PFC rectifier

and its controller. ............................................................................................................................ 7

Figure 2.1. Most common non-isolated inductive-based converter topologies. a. buck converter.

b. boost converter .......................................................................................................................... 12

Figure 2.2. A 3-to-1 ratio down-step ladder network switched capacitor converter, Φi represents

phase of operation of switches. ..................................................................................................... 20

Figure 2.3. Capacitive energy transfer modeling with a virtual resistor [47] ............................... 21

Figure 2.4. SMPS volume reduction using two inductive converter stages ................................. 23

Figure 2.5. SMPS volume reduction using two-stage approach utilizing a SC voltage attenuator

....................................................................................................................................................... 23

Figure 2.6. Single-phase buck converter with merged capacitive attenuator [55]........................ 24

Figure 2.7. A four-level boost-derived flying capacitor multi-level converter [58]. .................... 25

xii

Figure 2.8. The three-level boot converter [57]. ........................................................................... 26

Figure 3.1. Block diagram of a 2-phase merged switch capacitor buck (MSCB) converter and its

digital controller. ........................................................................................................................... 34

Figure 3.2. Operating modes of the capacitive attenuator; top: mode A; bottom: mode B. ......... 37

Figure 3.3. Key waveforms of the MSCB converter. ................................................................... 38

Figure 3.4. Approximate dc equivalent circuit of the converter. .................................................. 40

Figure 3.5. Converter configuration during a light-to-heavy load transient and low input voltage

range Vbatt<2Vout. ........................................................................................................................... 43

Figure 3.6. Converter configuration at start-up ............................................................................ 47

Figure 3.7. start-up transient of LC undamped input filter ........................................................... 49

Figure 3.8. Equivalent circuits of the top and bottom phase of the downstream buck for the both

portions of a switching interval..................................................................................................... 50

Figure 3.9. SC stage waveforms and gating signals during steady state operation; top to bottom:

Ch.3 (top): input current, iin(t) (200mA/div); Ch.4 (upper middle): resonance capacitor voltage,

vcr(t) (200 mV/div); Ch.2 (lower middle): bottom input capacitor voltage, vc2(t) (0.5V/div); Ch.4

(bottom): top input capacitor voltage, vc1(t) (0.5V/div); digital channels 1 to 9 are gating signal

G1 to G9. Time scale is 200 ns/div. Operating conditions: vin= 7 V, Vout = 1 V, Pout ~ 2.5 W. ... 52

Figure 3.10. Transient response for buck converter; top to bottom: Ch.4 (top): output voltage,

vout(t) (50mV/div); Ch.2 (upper middle): switching node voltage for top phase, vx1(t) (10V/div);

xiii

Ch.1 (lower middle): top phase inductor current, iL1(t) (2A/div); Ch.3 (bottom): bottom phase

inductor current, iL2(t) (2A/div); Time scale is 2 us/div. Operating conditions: vin= 7 V, Vout = 1

V, load current step of 2A to 8A. .................................................................................................. 53

Figure 3.11. Transient response for MSCB converter: Ch.4 (top): output voltage, vout(t)

(50mV/div); Ch.2 (upper middle): switching node voltage for top phase, vx1(t) (10V/div); Ch.1

(lower middle): top phase inductor current, iL1(t) (2A/div); Ch.3 (bottom): bottom phase inductor

current, iL2(t) (2A/div); Time scale is 2 us/div. Operating conditions: vin= 7 V, Vout = 1 V, load

current step of 2A to 8A................................................................................................................ 54

Figure 3.12. Start-up transient of MSCB converter: Ch.4 (top): output voltage, vout(t) (1V/div);

Ch.3 (upper middle): resonance capacitor voltage, vcr(t) (2V/div); Ch.2 (lower middle): top input

capacitor voltage, vc1(t) (2V/div); Ch.4 (bottom): bottom input capacitor voltage, vc2(t) (2V/div);

Time scale is 5 ms/div. Operating conditions: start up from zero state to vin= 7 V, Vout = 1 V, Pout

~ 2.5 W. ......................................................................................................................................... 55

Figure 3.13. Efficiency and loss comparison of buck and MSCB converters for 7V-to-1V

operating condition. ...................................................................................................................... 56

Figure 4.1: Non-symmetric multi-level boost (NSMB) based PFC rectifier and its downstream

stage. ............................................................................................................................................. 63

Figure 4.2: Equivalent circuit for the analysis of the inductor voltage swing and the voltage

waveforms of (a) a general boost-based converter and (b) the conventional boost. ..................... 66

xiv

Figure 4.3: Mode 1 of operation of the non-symmetric multi-level boost front-end stage: a) input

voltage range for mode 1; b) equivalent circuit of the converter during inductor charging phase;

c) equivalent circuit during the discharging.................................................................................. 69

Figure 4.4: Mode 2 of operation of the NSMB front-end stage: a) input voltage range for mode 2;

b) equivalent circuit of the converter during inductor charging phase; c) equivalent circuit during

the discharging. ............................................................................................................................. 70

Figure 4.5: Mode 3 of operation of the NSMB front-end stage: a) input voltage range for mode 3;

b) equivalent circuit of the converter during inductor charging phase; c) equivalent circuit during

the discharging. ............................................................................................................................. 71

Figure 4.6. Waveforms of the output capacitor voltage of an ideal PFC circuit; instantaneous

input power, voltage and current waveforms (a); decomposition of input power components (b);

and output capacitor voltage ripple (c) ......................................................................................... 74

Figure 4.7: The input filter and parasitic capacitances of the boost PFC circuit (top) and NSMB

PFC (bottom) circuits. ................................................................................................................... 77

Figure 4.8: Block diagram of the centre-tap voltage balancing system based on the downstream

converter current steering. ............................................................................................................ 80

Figure 4.9: Block diagram of the input current and bus voltage regulator. .................................. 81

Figure 4.10: Block diagram of the mode selector and sampling sequence generator................... 83

Figure 4.11: State flow diagram of the mode selector logic. ........................................................ 85

xv

Figure 4.12: Waveforms of the sampling sequence generator. ..................................................... 86

Figure 4.13: Problem of utilizing bypass diode in the NSMB topology. ..................................... 87

Figure 4.14: Centre tap voltage controller regulating operation of a forward based downstream

stage. ............................................................................................................................................. 89

Figure 4.15: Key waveforms of the centre-tap voltage regulator (from top to bottom): cd(t) –

pulse width modulated signal of the downstream stage controller; cd1(t) – control signal for Qd1;

cd2(t) – control signal for Qd2; i1(t) – discharging current of the top capacitor of the NSMB; i2(t) –

discharging current of the bottom capacitor of the NSMB. .......................................................... 90

Figure 4.16: Bridgeless NSMB converter topology. .................................................................... 92

Figure 4.17: Key waveforms of the conventional boost-based PFC rectifier; top to bottom: Ch.1

(top): attenuated output voltage, Hvbus(t) (2 V/div); Ch.2 (upper middle): switching node voltage,

vx(t) (200 V/div); Ch.3 (lower middle): input line current, iL(t) (0.5A/div); Ch.4 (bottom): input

line voltage, vin(t) (200 V/div). Time scale is 1 ms/div. Operating conditions: vline = 220 Vrms,

Vbus = 400 V, Pout = 100 W, C = 100 F , L = 680 H. ................................................................ 94

Figure 4.18: Key waveforms of the NSM-based PFC rectifier; top to bottom: Ch.1 (top):

attenuated output voltage, Hvbus(t) (2 V/div); Ch.2 (upper middle): switching node voltage, vx(t)

(200 V/div); Ch.3 (lower middle): input line current, iL(t) (0.5A/div); Ch.4 (bottom): input line

voltage, vin(t) (200 V/div). Time scale is 1 ms/div. Operating conditions vline = 220 Vrms, Vbus =

400 V, Pout = 100 W, Ctop = 150 F, Cbottom= 300 F , L = 680 H. ............................................ 95

xvi

Figure 4.19: Key waveforms of the conventional boost-based PFC rectifier; top to bottom: Ch.1

(top): attenuated output voltage, Hvbus(t) (2 V/div); Ch.2 (upper middle): switching node voltage,

vx(t) (200 V/div); Ch.3 (lower middle): input line current, iL(t) (0.5A/div); Ch.4 (bottom): input

line voltage, vin(t) (200 V/div). Time scale is 1 ms/div. Operating conditions: vline = 90 Vrms, Vbus

= 400 V, Pout = 100 W, C = 100 F , L = 680 H. ....................................................................... 96

Figure 4.20: Key waveforms of the conventional boost-based PFC rectifier; top to bottom: Ch.1

(top): attenuated output voltage, Hvbus(t) (2 V/div); Ch.2 (upper middle): switching node voltage,

vx(t) (200 V/div); Ch.3 (lower middle): input line current, iL(t) (0.5A/div); Ch.4 (bottom): input

line voltage, vin(t) (200 V/div). Time scale is 1 ms/div. Operating conditions: vline = 90 Vrms, Vbus

= 400 V, Pout = 100 W, C = 100 F , L = 680 H. ....................................................................... 97

Figure 4.21: Transitions from mode 1 to mode 2 (top) and from mode 2 to mode 3 (bottom);

Ch.m1(top): input line voltage, vin(t) (200 V/div); Ch.2 (upper middle): switching node voltage,

vx(t) (200V/div); Ch.4 (middle): gating signal of SW1, c1(t) (20 V/div); Ch.1 (lower middle):

gating signal of SW2, c2(t) (20 V/div); Ch.3 (bottom): input line current, iL(t), (0.5 A/div); digital

input: mode control signal (0 = mode 1, 1 = mode 2, 2 = mode 3). Time scale is 5 s/div.

Operating conditions vline = 220 Vrms, Vbus = 400 V, Pout = 100 W, Ctop = 150 F, Cbottom = 300

F, L = 230 H. ........................................................................................................................... 98

Figure 4.22: Capacitor taps voltage regulation with the downstream stage currents; top to bottom:

Ch.1 (top): top capacitor voltage, vupper(t) (100 V/div); Ch.2 (upper middle): bottom capacitor

voltage, vbottom(t) (100V/div); Ch.4 (lower middle): discharging current of bottom capacitor, i2(t)

( 1 A/div); Ch.3 (bottom): discharging current of top capacitor, i1(t), (1 A/div);. Time scale is 2

xvii

s/div. Operating conditions vline = 220 Vrms, Vbus = 400 V, Pout = 70 W, Ctop = 150 F, Cbottom =

300 F, L = 230 H. ..................................................................................................................... 99

Figure 4.23: Amplitudes of harmonics (multiples of 50 Hz) around line frequency and the

switching frequency for the NSMB-based PFC prototype (top) and the conventional boost based

prototype (bottom). ..................................................................................................................... 101

Figure 4.24: Efficiency comparison of the conventional boost, three level boost and NSMB PFC

converters for the line input of 265 Vrms. .................................................................................... 102

Figure 4.25: Efficiency comparison of the conventional boost, three level boost and NSMB PFC

converters for the line input of 85 Vrms ....................................................................................... 102

Figure 4.26: Loss break down analysis for the conventional boost, three level boost and NSMB

PFC converters for 85Vrms and 265 Vrms input voltages at the light load operating condition

(50W). Length of each bar is normalized based on the losses of the boost at 90Vrms which is

9.8W. ........................................................................................................................................... 104

Figure 4.27: Loss break down analysis for the conventional boost, three level boost and NSMB

PFC converters for 85Vrms and 265 Vrms input voltages at the light load operating condition

(350W for 85Vrms and 400W for 265Vrms). Length of each bar is normalized based on the losses

of the boost at 90Vrms , which are 50.5W. ................................................................................... 105

Figure 4.28: Normalized volume distributions of conventional boost-based PFC and three other

solution. In case of the latter three cases, a volume break down in case of implementation with

optimal switches, i.e. lower voltage/current rated switches in single package, is also shown. .. 106

xviii

List of Acronyms

DPWM Digital Pulse Width Modulator SMPM

AC Alternating Current

ADC Analog-to-Digital Converter

CCM Continuous Conduction Mode

CM Common Mode

CPM Current Program Mode

CPU Central Processing Unit

DAC Digital-to-Analog Converter

DC Direct Current

DCM Discontinuous Conduction Mode

DCR DC resistance

DM Differential Mode

EMI Electro-magnetic Interference

ESR Equivalent Series Resistance

FSM Finite State Machine

xix

IC Integrated Circuit

LCD Liquid Crystal Display

LUT Look-up Table

MAC Multiplier Accumulator

MSCB Multi-phase Switched-capacitor Buck

NSMB Non-Symmetric Multi-level Boost

PCB Printed Circuit Board

PI Proportional Integrator

PID Proportional Integral Derivative

PWM Pulse Width Modulation

SC Switched-Capacitor

SMPS Switch-Mode Power Supply

1

Chapter 1

Introduction

1.1 Motivation

In the past few decades, electronic devices have progressively become more prevalent in many

different application areas, as diverse as communication, healthcare, transportation,

entertainment and consumer electronics, making them an essential part of today’s modern life.

2

In almost all of these applications the electric energy source, the ac line from utility network or a

set of battery cells, supplies the device by providing a variable and/or unregulated voltage,

whereas the functional blocks of the device require well-regulated dc voltages at a different

levels.

Switched mode power supplies (SMPS) are widely used to serve the purpose of regulating the

voltage supplied by the electric energy source and delivering power to the electronic loads, i.e.

functional blocks. That is mainly due to their significantly higher power density, power

processing efficiency and their capability to cope with larger input voltage range compared to

other existing solutions such as analog linear regulators [1], [2].

Still, the volume miniaturization of switched mode power supplies has not kept up with the pace

of reduction in size of the electronic loads they supply. This is especially prominent in portable

applications and consumer electronic products such as cell phones, tablets, personal computers,

liquid crystal display (LCD) monitors and TV sets.

In fact, in modern electronic devices switched mode power supplies often occupy up to 25% of

the overall volume of the device. In these systems the reactive components of power supplies,

i.e. inductors and capacitors, take most of the volume and are among the largest contributors to

the overall device weight [3]. In order to visually demonstrate a typical scenario, the portion of

the PCB area occupied by the switched mode power supplies in a Google Nexus 7 tablet and a

Panasonic Plasma TV is compared to the overall area of their electronic circuits in Fig. 1.1.

Another important feature of SMPS converters that shall not be undermined while focusing on

volume reduction of a power supply is their power processing efficiency. In battery operated

3

a) b)

Figure 1.1. Comparison of overall area occupied by power supplies (shown in red boxes) to the

overall PCB area for, a) a battery operated Google Galaxy Nexus 7 Tablet [4]; b) an ac powered

Panasonic VIERA TX-P50VT30E plasma TV [5].

electronic devices, high power conversion efficiency is crucial in order to increase the often

insufficient battery life of the device, attributed to the limited energy storage capacity of their

batteries. Furthermore, the high converter efficiency translates into savings on energy costs,

which is an imperative factor in higher power applications. Moreover, operation of the converter

with reduced volume at same or lower efficiency is not practical, since it results in a higher heat

density, requiring addition of heat sinks, and reduced reliability of the device. Therefore, in a

feasible solution for converter miniaturization, the converter volume reduction has to be

accompanied by proportional increase of its power processing efficiency.

In most of these applications buck or boost converters, or their simple derivations such as

forward or flyback converters, are conventionally used, due to their controller simplicity.

However, as it will be shown in this thesis, these topologies are not the optimized solutions, from

the size and weight point of view, for many applications and often result in overdesign of the

power stage components and, hence, increased volume and cost.

4

In these converters, the size of reactive components is mainly determined by the difference

between input and output voltages and converter switching frequency; the higher conversion

ratios and lower switching frequencies result in larger size of passive elements.

Although reduction of converter volume can be accomplished through an increase in switching

frequency, it results in more switching losses and efficiency degradation. Hence, operation in

higher switching frequency does not provide a viable solution to converter volume reduction.

In many applications of switched mode power supplies (SMPS), there is a relatively large

voltage difference between the converter input and output voltages under some operating

conditions, which has a large impact on the overall volume. For example, this can be noticed in

battery operated dc-dc converters due to large variation of the battery voltage and low voltage

requirement of digital loads. Also, in laptop computers, the power supply has to provide voltage

step-down conversion ratios up to 19:1 [6]. Other examples are ac-dc converters, where a similar

situation exists due to input voltage swing during one line cycle, e.g. 0V to 374V, while

delivering constant output voltage of around 380V or higher. Those large input-to-output voltage

differences result in increased overall volume and cost of the conventionally used buck or boost

converters due to their more demanding filtering requirements [6]-[10]. The difference also

increases switching losses, due to switching higher voltages across semiconductor switches and,

therefore, limits the maximum operating frequency of the converter besides reducing the

converter efficiency.

The newly emerged digital controllers allow for control of switching actions for new and more

complex converter topologies than the traditional analog controlled solutions. Therefore they

provide opportunities for minimizing overall converter volume and losses. The prior work [6]-

5

[10] with regards to this approach suggest that a combination of high power density switched

capacitor circuits and inductive based converter topologies, such as buck or boost, is a suitable

candidate to fulfill the goal of reducing overall converter volume while improving the power

processing efficiency at the same time. Such topologies often utilize two stages consisting of a

switched capacitor converter and an inductive-based converter stage. Those 2-stage structures

result in a significant reduction of the overall volume but at the same time introduce a relatively

large number of extra switches in the conduction path. As a consequence, the conduction losses

of those topologies are often preventing their use in higher current applications. Moreover they

usually require addition of intermediate or flying capacitors that contribute to the overall volume.

1.2 Thesis Objectives

The main goal of this thesis is development of novel converter topologies based on merging

switched capacitor (SC) and inductive based converter stages and, thus, reducing voltage

difference across components of the inductive based converter stage. By merging SC and

inductive based stages, instead of a straight forward connection of two stages, the capacitor of

input/output filter existing in inductive based converter is utilized in the SC stage, eliminating

intermediate and/or flying capacitors. Moreover, the switches between the two stages are shared

and the inductor current can be utilized for charge balancing of the SC stage. Hence, the overall

volume and efficiency can be improved compared to other two stage solutions [7-12].

Two types of hybrid converter topologies are focus of this work that target volume/efficiency

improvements for the two commonly used topologies, namely, buck and boost converters in

applications with large input-output voltage difference.

6

The implementation of the introduced multi-phase dc-dc converter for battery operated point of

load applications is demonstrated. The functionality of the developed boost-based topology is

also verified through its realization as a power factor correction rectifier circuit, i.e. ac-dc

converter.

1.3 Thesis Organization and Contributions

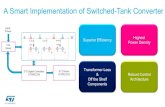

In the first part of the work, a multiphase dc-dc converter based on merging a capacitive divider

stage and a buck converter, as shown in Fig. 1.2 is developed. This topology is suitable for

applications requiring high step-down dc-dc converters and allows for a reduction of the volume

of the step-down converters with a lower penalty in conduction losses compared to other 2-stage

solutions [6], [8], [11]. Compared to the single-stage merged buck converter with capacitive

Cout

L2

L1

Cin1

Cin2

e[n]d[n]

Cr

Lf Lp

G6

G8 G9

G7

Digital controller

ADC &

Transient

detector

PID

Active capacitive divider

DPWM

Minimum Deviation

logic

Switching control

logic

d1[n]

G1

G2 G3 G4 G5

vout(t)

2-phase interleaved buck

converterInput filter

Vin1

Vin2

+

+

_

_

R

+

_

Vbatt

vx2(t)

vx1(t)Q8

Q2Q3

Q5

Q4 Q6

Q7

Q9

Q1

c(t)

ss

lv

tror

tr

Figure 1.2. Block diagram of a 2-phase merged switch capacitor buck (MSCB) converter and its

digital controller.

7

attenuator [7], the introduced converter provides a common ground between the input and output

voltages. Therefore, it allows for multi-phase operation, which in previous solutions was not

possible, and, as such, provides a suitable solution for medium to high power range applications.

Furthermore, the merged topology has a larger inductor current slew rate than a multiphase buck

converter resulting in a significantly faster transient response.

In the second part of the thesis a universal ac-dc power factor correction rectifier of Fig. 1.3 that

merges a boost power stage and a non-symmetric capacitive attenuator is presented.

This converter reduces the size of the boost inductor to a one third of the value required for the

conventional boost PFC and, for the rest of the power stage; its implementation requires the same

volume and silicon area of components as those of a conventional boost converter. The new PFC

topology also reduces switching losses of the converter through the entire operating range

without any considerable penalty in conduction losses.

Liin(t)

C

2C

+

vout(t)

_

Q1

Q2

D2

+

2Vbus/3

_

+

_

D1

Signal comparators and

mode selector

Dual-input isolated dc-dc

downstream converter

H

vx(t)

+

vin(t)

_Full-wave diode

rectifier

vline(t)

+

_ Vbus/3

H

Load

vct(t)

vtop(t)

cd(t)

Hdvout(t)

H Hd

Input current and buss voltage regulator

Downstream stage

controller

Averaged current programmed mode

controller

Centre-tap voltage

regulator

Pulse redirection

logic

Hvtop(t)

Hvct(t)

d[n]Hvin(t)

cd1(t) cd2(t)c1(t) c2(t)

NSMB Controller

Rsiin(t) Hvin(t) Hvct(t) Hvtop(t)

c1(t)

c2(t)

Figure 1.3. Block diagram of the non-symmetric multi-level buck (NSMB) based PFC rectifier

and its controller.

8

Compared to the three-level boost [9] the inductor reduction is achieved by providing non-equal

voltages across the capacitive divider cells and, in that way, effectively creating a structure that

produces 4-output voltage levels. Therefore, a 33% reduction in the inductor volume along with

improved efficiency is achieved compared to a three-level-boost while having the same

implementation cost. The capacitive divider voltages are regulated with a downstream converter

that, due to dual input operation, also has smaller volume than the conventional downstream

solutions.

To summarize, the main contributions of this thesis are:

• Development of a new multiphase converter topology and its accompanying digital

controller that merges a capacitive divider and a multiphase buck converter that minimizes

switching losses and volume of inductor and also output capacitor of the buck converter by

improving its transient response,

• Development of a four level boost-based PFC converter and its accompanying digital

controller that reduces the size of boost inductor and converter switching losses by utilizing a

non-symmetric capacitive divider instead of the output capacitor of the conventional boost PFC

1.4 Thesis Outline

The thesis is organized as follows:

Chapter 2 reviews the main challenges regarding miniaturization of the switched mode power

supplies summarizing the related previous work. Special attention is given to the prior art with

9

respect to the targeted applications, namely, battery operated point of load (PoL) converters

based on buck converter and ac-dc boost based converters.

Chapter 3 presents the first major contribution of this work which is the development of a multi-

phase dc-dc converter topology based on the multi-phase buck converter. The principle of the

operation for the converter, details of the design procedure and main implementation challenges

for the introduced converter are addressed followed by the results, experimentally verifying the

anticipated advantages.

Chapter 4 introduces a boost-based converter that operates based on the same principle, i.e.

replacing the output filter of boost with an active capacitive attenuator. The new topology is

reducing boost converter volume and losses and is the second major contribution of this thesis.

The converter design, operation and practical implementation challenges have been fully

analyzed for the case when it is employed as an ac-dc power factor correction (PFC) rectifier.

Moreover the unified digital controller that governs the operation of the ac-dc stage and the PFC

down-stream dc-dc converter is presented. This is followed by a set of experimental results from

the developed prototype converter.

Finally, this thesis is concluded in Chapter 5, summarizing the main contributions of the

presented work as well as exploring the directions for possible future research.

10

References

[1] J. illiams “High Efficiency Linear Regulators ” Linear Technology Application Note 32

March 1989.

[2] M.S. Makowski, and D. Maksimovic, "Performance limits of switched-capacitor DC-DC

converters," Power Electronics Specialists Conference, 1995. PESC '95 Record., 26th Annual

IEEE, vol.2, no., pp.1215-1221, 18-22 Jun 1995

[3] Y. Kaiwei, High-frequency and high-performance VRM design for the next generations of

processors, 2004, Virginia Polytechnic Institute and State University.

[4] J. Devincenzi, D. Hodson, M. Djuric, B. McCrigler, et. al. “Nexus 7 Teardown.” Internet:

https://www.ifixit.com/Teardown/Nexus+7+Teardown/9623, July 02, 2012 [June 11, 2014].

[5] “Panasonic VIERA TX-P50VT30E Teardown.” Internet: http://www.fullhd.gr/reviews/tv-

tear/item/7902-panasonic-viera-tx-p50vt30e-teardown.html, April, 21, 2011 [June 11, 2014].

[6] J. Sun; X. Ming, Y. Yucheng, F.C. Lee, "High Power Density, High Efficiency System Two-

stage Power Architecture for Laptop Computers," Power Electronics Specialists Conference,

2006. PESC '06. 37th IEEE , vol., no., pp.1-7, 18-22 June 2006

[7] A. Radić, A. Prodić, "Buck Converter With Merged Active Charge-Controlled Capacitive

Attenuation," IEEE Trans. on Power Electron., vol.27, no.3, pp.1049-1054, March 2012

[8] R.C.N. Pilawa-Podgurski, D.M. Giuliano, D.J. Perreault, “Merged two-stage power converter

architecture with soft charging switched-capacitor energy transfer,” in Proc. IEEE Power

Electronics Specialist Conf., 2008, pp. 4008-4015, June 2008.

[9] T.A. Meynard, H. Foch, "Multi-level conversion: high voltage choppers and voltage-source

inverters," in Proc. IEEE PESC '92, pp.397-403 vol.1.

[10] M.T. Zhang, Y. Jiang, F.C. Lee, M.M Jovanovic, "Single-phase three-level boost power

factor correction converter ," in Proc. IEEE APEC '95, pp.434-439 vol.1.

[11] J. Sun, M. Xu, and F. C. Lee, “Transient Analysis of the Novel Voltage Divider,” in Proc.

IEEE Applied Power Electronics Conf., 2007, pp. 550–556. Feb. 2007.

[12] F. Forest, T.A. Meynard, S. Faucher, F. Richardeau, J.J. Huselstein, C. Joubert, "Using the

multilevel imbricated cells topologies in the design of low-power power-factor-corrector

converters," IEEE Trans. on Industrial Electronics, vol.52, no.1, pp. 151- 161, Feb. 2005.

11

Chapter 2

Background and Previous Art

This chapter presents an overview of the relevant previous work. At first limiting factors of most

commonly used, single stage converter topologies, especially in applications of interest with

large input-output voltage difference, are briefly addressed. Previously developed techniques

utilized for improvement of such converters and their shortcomings are discussed next. The prior

art involving reduction of input-to-output voltage ratio using straight-forward, serial connection

12

of switched capacitor and inductive based solutions is covered in fourth subsection. This is

followed by an overview of the concept of merging the two converter stages and the advantages

of previous solutions using the same concept. The shortcomings of the existing merged solutions

in high conversion ratio applications and those requiring higher power ratings are also discussed,

exposing the areas for further improvements of such converter topologies, which is the main

focus of this dissertation.

2.1 Topology Limits

Traditionally, inductive-based buck converters (Fig. 2.1.a), have been the default switched mode

power converters in voltage step-down DC-DC applications, where they are used in a wide range

of applications requiring moderate to high power levels (>100mwatt) [1]. Boost converter (Fig.

2.1.b), being similar to a buck converter with flipped input/output ports, has a similar dominance

in SMPS applications where an input voltage step-up is desired. These converters provide simple

and relatively cost-effective solutions since they are implemented with a low number of

components and, a relatively simple controller governs their switching actions and regulates the

output voltage. Nevertheless, their relative simple implementation comes with a number of

disadvantageous. Their switches have to be rated for maximum voltage in the circuit, Vin for

L

SW1

D1

Cout

load

+vout(t)

_

0

Vout

iin(t)=iL(t)

Vin

+

_

iin(t) iL(t)

Vin

L

Cout Vout

0

Vin

+

_

load

SW1

SW2

a) b)

Figure 2.1. Most common non-isolated inductive-based converter topologies. a. buck converter.

b. boost converter

13

buck and Vout for boost, their inductors are connected to the converter low voltage side, Vout for

buck and Vin for boost, meaning their inductors have to be rated for the highest of the input or

output converter current, increasing their volume. In addition, since the switches have to

interrupt the inductor current and block the higher of input or output voltage, their switching

losses are relatively high which reduces their efficiency.

A more detailed analysis of such shortcomings of these two most commonly used inductive

based converters, i.e. buck and boost, is presented in the following subsection. As will be shown,

the negative effects of such drawbacks become more severe as the input-to-output voltage

difference grows higher, creating a need for the development of new topologies to minimize

these problems.

2.2 Reactive Components Volume

Reactive components are among the biggest contributors to the weight and volume of the

inductive-based converters [1], [2]. This section reviews the main factors that determine the size

of these components, i.e. energy transfer inductor and output capacitor.

2.2.1 Inductor Volume

In inductive-based converters, the inductor serves the purpose of cycle-to-cycle energy transfer

from the input source to the load connected on the converter output side, where both the input

and the output side behave either capacitive or voltage source like behavior. Storing of this

transferred energy, i.e. differential energy, in each switching cycle over the inductor results in an

inevitably existing ac current ripple superimposed on the dc inductor current. This energy can be

found from

14

LLLLLLLL iLIiILiILiILE 2)4()()(212

212

21 , (2.1)

where ∆E is the transferred energy from input to output in one switching cycle, L is the

inductance value, IL is the average inductor current and ∆iL is the inductor current ripple. Large

inductor current ripples result is increased losses over converter switches and inductor itself and

may lead to magnetic core saturation. In inductive-based converters the inductor size is

determined based on maximum desired inductor current ripple value [2]. As shown in [2], for

buck and boost converters, the amplitude of this current ripple, ∆iL, can be found by equations

2.2 and 2.3 respectively.

swin

outoutbuckL

fV

V

L

Vi

1)1(

2, . (2.2)

swout

ininboostL

fV

V

L

Vi

1)1(

2, . (2.3)

As seen from equations 2.2 and 2.3, close input-to-output voltage difference requiring small

conversion ratios can significantly reduce inductor volume.

2.2.2 Output Capacitor Volume

In dc-dc applications, the output capacitor is mainly chosen to meet requirements for output

voltage variations during load transients. This is due to the fact that output capacitor charge

taken/delivered during large load-steps is much larger than that of causing ac output voltage

ripple at the switching frequency [3]. As discussed later in this chapter, the size of output

capacitor is mainly dependent on controller performance during load transients.

15

In ac-dc applications, the size of output capacitor is determined by the desired ac output voltage

ripple at twice line frequency (∆Vout) [2], which mainly depends on input voltage frequency

(fline), load power, and output voltage and it is not dependent on the converter topology. The size

of the output capacitor in such applications can be found as [2]

outlineout

load

outout

acin

outVV

P

VC

EC

2

_. (2.4)

2.3 Converter Losses

The primary sources of converter losses are conduction and switching losses. Conduction losses

are mainly caused by the on resistances of the switches Ron, diode forward voltage drop (Vfd) and

resistive losses of other components in current conduction paths such as inductors. The fact that

buck and boost converter have a minimum number of components in conduction path, one

semiconductor device and inductor at any moment, enables them to achieve a rather good

performance in terms of minimizing conduction losses. However, this mainly depends on Ron of

switches and Vfd of diodes. Since the figure of merits of semiconductor devices, are inversely

proportional to their blocking voltages (Vds) [4], operation under higher switching voltages

negatively affects conduction losses of buck and boost converters. This is mainly due to

increases of switch on-resistances and diode forward voltage drops for a given silicon area.

Conventional hard-switched buck and boost force switches to commutate under concurrent

presence of non-zero current and voltage across them causing switching losses. Largest portion

of switching losses of these converters is created during the switch commutation period. The

switching losses of a hard switched transistor can be found by [2]

16

swxossswoffonLxsw fVcfttiVP 2

2

1)(

2

1 , (2.5)

where the first term corresponds to the commutation losses [2] and the second term represents

losses due to switch parasitic capacitances. In this equation, Vx is the voltage swing at converter

switching node which is equal to Vin and Vout for buck and boost converters, respectively; ton and

toff are commutation times during turn on and turn off transient of switches and Coss represents

output capacitance of the switch. As shown by this equation, switching losses are proportional to

the switching voltage and switching frequency. Therefore, in applications with large input or

output voltages, buck and boost converters will have relatively large switching losses, both due

to increased switching voltage and also increased parasitic capacitance of switches as they have

to be rated for higher voltages [4].

The discussion in this section indicates that the utilization of a buck or boost converter in

applications with large conversion ratios results in a large inductor volume and at the same time

negatively affects conduction and switching losses reducing system efficiency.

2.4 Volume reduction techniques

This Section reviews the existing methods for volume reduction of inductive-based converter

topologies. In each case the advantageous and drawbacks are briefly addressed.

2.4.1 Increasing Switching Frequency

Traditionally, increase of switching frequency of the converters has been the most commonly

method used for reducing the volume of converters. Increasing switching frequency reduces the

inductor volume by proportionally reducing its current ripple, (as shown in Eq. 2.1 and 2.2).

17

Moreover, switching at higher frequencies allows for higher controller bandwidth [2] that can

improve transient response of the converter, minimizing its output capacitor size in dc-dc. On the

other hand, this raises the frequency-dependent losses, such as magnetic core losses and

switching losses, as predicted by Eq. 2.5, reducing converter efficiency especially at light load

operating conditions. This efficiency degeneration and increased heat density associated with it

are the main factors limiting the switching frequency of high step down converters.

2.4.1.1 Soft switching techniques

Soft switching methods have been developed to reduce switching losses of hard switched

converters [33-36]. Therefore, they potentially allow for converter operation with higher

switching frequencies and volume reduction of reactive components while maintaining high

power processing efficiency. In general these methods implement zero current switching (ZCS)

or zero voltage switching (ZVS) for semiconductor devices by addition of a controlled resonant

circuit. In these methods a soft switching is achieved by creating a resonant current/voltage

through/across the converter switches and commutating switches when that current/voltage is

zero. This allows for operation at higher frequencies with smaller penalties in terms of switching

losses and, therefore, allows for implementation of converters with higher power densities. These

advantages come with the cost of extra circuitries and additional conduction losses introduced by

the resonance current, affecting light load converter efficiency [36-37]. However the adoption of

soft switching converters in some medium to high power applications this tradeoff has proved to

be favorable.

18

2.4.2 Interleaving techniques

Increase of effective switching frequency can also be achieved through the utilization of

interleaved multi-phase topologies where a number of converter switching cells are connected in

parallel and their internal switching instants are sequentially time shifted over equal fractions of

a switching period [5-9]. Interleaved topologies reduce the input and output current/voltage

ripple of the converters, allowing for reduction of the input and output filter size and achieving

improvements in terms of the output capacitor in dc-dc applications by facilitating transient

recovery [10] with lower penalties in terms of switching losses. Moreover, interleaved converters

have proven to be effective solutions for larger power ratings, where the semiconductor

switching components can be fully utilized. However, these solutions still suffer from relatively

high switching losses, since they switch full range of input/output voltages and, when operating

at light and medium loads, from either degradation of efficiency or quality of the input current

waveform [11]. Furthermore, interleaving does not reduce inductor current ripple in each

switching cell, thus their magnetic core losses and inductor copper losses are the limiting factor

for inductor volume reduction and the reduction of inductor volume is not proportional to the

rate of increase in effective switching frequency [12].

2.4.3 Non-linear Controllers

In dc-dc applications of switched mode power supplies, dynamic behavior of the converter is the

main factor determining the output capacitor volume. A converter with poor transient response

requires overdesigned power stage components to avoid failure during large transients. Linear

controllers being designed through state-space averaging modeling are fairly simple to

19

implement but inherently have bandwidths limited to an order of magnitude lower than converter

switching frequency. Recently emerged nonlinear controllers, utilizing digital control techniques

[13-23] have proven to be capable of achieving significant improvements in dynamic behavior of

the converter, only restricted by physical limitations of power stage reactive components, such as

inductor current slew rates, which is determined by converter topology.

2.4.4 Ripple Cancellation

In numerous applications of the ac-dc rectifiers with power factor correction, i.e. PFC rectifiers,

minimization of the output voltage ripple at the twice line frequency is needed. This is done

through increasing the size of converter output capacitor as shown in Eq. 2.4. To minimize the

output ripple at twice the line frequency without paying a large price in the system size and

reliability, a number of solutions have been proposed [24-32]. Arguably, among the most

effective are ripple cancellation based systems [24], [27]-[32]. There, a small auxiliary converter

stage, i.e. ripple cancellation circuit, is used to minimize the ripple. The auxiliary converter

improves the voltage regulation by transferring the component at twice the line frequency from

the output capacitor of the PFC stage, Cout , to its own capacitor, Caux.

2.5 Switched Capacitor Converters

Switched capacitor (SC) converters [38]-[40] realize dc-dc conversion utilizing circuits

consisting of a network of switches and capacitors only, Fig. 2.2. These converters operate by

capacitive energy transfer from input source to the load as opposed to inductive energy transfer

being used in inductive-based converters. This is done through utilization of a number of

switching cells, operating in cyclical phases. In each cycle, a small amount of charge is delivered

to the load depending on the load current and the switching frequency. Elimination of magnetic

20

C3

C4

Cout

C2

iin(t)

Vin

+

_

Φ1 Φ1 Φ1Φ2 Φ2Φ2

SW1 SW6SW5SW4SW3SW2

load

Figure 2.2. A 3-to-1 ratio down-step ladder network switched capacitor converter, Φi represents

phase of operation of switches.

component results in significant gains in converter power density and allows for realization of

fully integrated converters in low power applications.

As shown in [41-42] SC converters can achieve high power density and high efficiency in lower

power applications (up to few watts). Though, SC converters can achieve high efficiency only

when operating at conversion ratios close to their ideal (rational) ratio for the given topology and

operating mode. Operation at wide input voltage range can significantly degrade their efficiency

[43]-[46].

SC converters also introduce additional switching losses due to the capacitive energy transfer.

This is due to the fact that by connecting two capacitors with different voltage levels, an amount

of charge of ∆q is transferred from the capacitor with higher voltage, v1, to the one with a lower,

v2. This reduces the overall electric potential energy of the system of two capacitors by an

amount of ∆q.(v1-v2). This energy is dissipated as heat over the switch resistance and capacitor

equivalent series resistance (ESR) and/or radiated in the air. This loss can be modeled as a

virtual resistance R, controlling the current flow in a switched capacitor circuit [47] as shown in

21

Cout

iin(t)

V1

+

_

loadV2

+

_

R=1/C1fsw

Cout

iin(t)

V1

+

_C1

load

fsw

V2

+

_

a) b)

Figure 2.3. Capacitive energy transfer modeling with a virtual resistor [47]

Fig. 2.3. In an ideal case with negligible or no switch resistance and capacitor ESR, this energy

will be radiated at a very high frequency, contributing to circuit electromagnetic interference,

EMI.

Another drawback of SC converters compared to their inductive-based counterparts is their

pulsating input and output current waveform, which introduces the electromagnetic interference

by conducted emissions. This also results in SC switches to be overrated to cope with high input

current peaks due the short charging period [48]. This problem can be minimized by addition of

a big input capacitor which in turn increases the converter volume significantly [48].

In an optimal design of an SC converter, the switches can be rated for fractions of input voltage

based on the blocking voltage requirement for their steady state operation, i.e. they can be rated

for Vin/3 in example of Fig. 2.3. However, during the start-up transient of the converter when

capacitors are not charged, the switches are exposed to the full input voltage. Therefore in the

practical implementation the benefits associated with lower voltage rated switches cannot be

fully utilized and switches are rated for full range of input voltage. In some cases this issue can

be addressed by addition of extra circuitry [49].

22

2.6 Two-Stage Converter topologies

Among the applications of switched mode power supplies requiring large dc-dc input-to-output

voltage ratios, portable devices are of paramount significance due to their very large market

share. Some examples of such devices include tablets, laptops and gaming consuls, where the

input battery voltage has to be converted from 7-19V to 1V or below, to supply processing units

[50-51].

Utilization of high power density SC converters is not a viable solution in these applications due

to the wide range of input voltage and requirement of tight output voltage regulation during load

transients. Therefore, most of the converters used for these applications are single-stage multi-

phase buck topologies [52].

It has been shown by [53-54] that utilization of two-stage topologies in these applications can

result in a reduction of the overall converter cost and volume. In these solutions, a first stage

single-phase buck converter reduces the level of input voltage. A second stage multi-phase buck

converter connects serially after the first stage, regulating the output voltage as shown in Fig. 2.4

In such topologies the volume and cost reduction is still limited due to having an inductive first

stage that runs at 200-300 kHz [51].

Substituting the first stage of such two stage topologies with an SC converter has proven to result

in further volume reduction and efficiency improvements [46], [51] shown in Fig. 2.5. In this

case, the SC stage can operate with a constant conversion ratio, achieving optimal volume and

efficiency.

23

These 2-stage structures result in a significant reduction of the overall volume but at the same

time introduce a relatively large number of extra switches in the conduction path. As a

consequence, the conduction losses of those topologies are often preventing their use in higher

current applications. In addition, the cascaded topologies also use separate controllers for each of

the two stages increasing hardware complexity.

Input Filter

Cin

Lf

Vbatt

Cout

Vout

R

L1Q1

Q2

0

Vbatt/n

n

Vbatt

Multi-phase buck converter

stageBuck voltage attenuation

stage

LnQ1

Q2

LQ1

Q2

0

Vbatt

Figure 2.4. SMPS volume reduction using two inductive converter stages

Input Filter

Cin

Lf

Vbatt

Cout

Vout

R

L1Q1

Q2

0

Vbatt/n

n

Vbatt

Multi-phase buck converter stageSwitched capacitor Stage

LnQ1

Q2

Figure 2.5. SMPS volume reduction using two-stage approach utilizing a SC voltage attenuator

24

2.7 Topologies Merging Inductive-based Solutions and Capacitive

Attenuator

The benefits of the 2-stage converters are achieved through reduction of input-to-output voltage

difference for the inductive based converter by utilizing a first voltage attenuation stage. A

recent publication [55] shows that same functionality can be achieved by merging a capacitive

divider and a downstream buck converter as shown in Fig. 2.6. There, the switches of both stages

are shared to minimize conduction losses and the buck inductor is used for the SC stage capacitor

charge balancing, eliminating a bulky intermediate capacitor existing in other SC-based solutions

[46], [51]. The charge control of the input capacitors through buck inductor also eliminates the

extra switching losses of switched capacitor converters, due to pulse current transfer between

capacitors during capacitive charging process, forming a virtual resistance [9]. This modification

also reduces the number of switches in the conduction path, i.e. conduction losses, and simplifies

control, allowing regulation of both stages with a single controller. Still, realization of a multi-

phase solution utilizing this topology is not feasible since it does not provide a common ground

between input and output voltages.

Input Filter

Lf

Vbatt

Cout

Vout

R

L

0

Vbatt/2Cin1

Cin2

2

battV

2

battV

Q1

Q2

Q3

Q4

Figure 2.6. Single-phase buck converter with merged capacitive attenuator [55].

25

In case of the boost converter, a similar approach of merged inductive based converter and

output capacitive attenuator can be used to minimize both the inductor size and the switching

losses, by reducing the stress of the components. Multi-level converters [56-62] that have been

originally developed for use in high voltage applications, such as dc-ac inverters and ac-dc

rectifiers operate based on the same principle.

In the flying capacitor multi-cell boost [58], shown in Fig. 2.7, derived from the multilevel

concepts [63], these advantages are achieved by adding few switches and a relatively large flying

capacitor.

A three-level boost-based PFC [57], shown in Fig. 2.8 replaces the output capacitor of the boost

converter with a compact active capacitive divider and, for the same switching frequency, results

in a 50% reduction of the inductor value compared to the conventional boost converter.

L

SW1

Vin

SW3

SW2

D3 D2 D1

+

vout(t)

_

+2vout(t)/3

_

vout(t)/3+_

Cout

C2

C1+

_

Figure 2.7. A four-level boost-derived flying capacitor multi-level converter [58].

26

L

SW1

SW2

D1

D2

C1

C2

+

vout(t)

_

+

vout(t)/2_

+

vout(t)/2_

Vin

+

_

Figure 2.8. The three-level boot converter [57].

The converter topologies introduced in this thesis operate based on similar principle as the

presented merged topologies, further improving their performance and reduce their volume.

Hence the concepts discussed in this section will be revisited in Chapter 3 and 4 of this

dissertation and some of them will be used to derive the new topologies.

2.8 References

[1] M.D. Seeman, V.W. Ng, L. Hanh-Phuc, M. John, E. Alon, S.R. Sanders, "A comparative

analysis of Switched-Capacitor and inductor-based DC-DC conversion technologies," In Proc.

IEEE COMPEL 2010, pp.1-7, June 2010

[2] R. W. Erickson and D. Maksimovic, Fundamentals of Power Electronics. New York, NY:

Springer Media Inc., 2001.

[3] S.M. Ahsanuzzaman, A. Parayandeh, A. Prodić, D. Maksimovic, "Load-interactive steered-

inductor dc-dc converter with minimized output filter capacitance," In Proc. IEEE APEC 2010,

pp.980-985, Feb. 2010.

[4] B.J. Baliga, “Fundamentals of Power Semiconductor Devices,” NewYork, NY: Springer,

2008.

27

[5] B. Miwa, “Interleaved Conversion Techniques for High Density Power Supplies,” PhD

Thesis, Massachusetts Institute of Technology, Department of Electrical Engineering and

Computer Science, 1992.

[6] B. A. Miwa, D. M. Otten, and M. F. Schlecht, “High efficiency power factor correction using

interleaving techniques,” in Proc. IEEE Appl.Power Electron. Conf., 1992, pp. 557–568.

[7] C. Chang, M.A. Knights, "Interleaving technique in distributed power conversion systems,"

IEEE Trans on Circuits and Systems I: Fundamental Theory and Applications, vol.42, no.5,

pp.245-251, May 1995

[8] L. Balogh, R. Redl, "Power-factor correction with interleaved boost converters in continuous-

inductor-current mode," in Proc. IEEE APEC '93. pp.168-174.

[9] P.W. Lee, Y.S. Lee, D.K.W. Cheng, and X.C. Liu, “Steady-State Analysis of an Interleaved

Boost Converter with Coupled Inductors,” IEEE Trans. on Industrial Electronics., vol. 47, no. 4,

pp.787-795, Aug. 2000.

[10] X. Zhou; P. Wong; P. Xu; F.C. Lee, A.Q. Huang, "Investigation of candidate VRM

topologies for future microprocessors," IEEE Tran. on Power Electron., vol.15, no.6, pp.1172-

1182, Nov 2000

[11] C. Wang, “Investigation on Interleaved Boost Converters and Applications,” PhD thesis,

Virginia Polytechnic Institute and State University, July 2009.

[12] M. O’Loughlin, “An Interleaving PFC Pre-Regulator for High-Power Converters,” Texas

Instruments Seminar, http://www.ti.com/download/trng/docs/seminar/Topic5MO.pdf

[13] K. Ka-Sing Leung, H. Shu-Hung Chung, “Dynamic hysteresis band control of the buck

converter with fast transient response,” IEEE Trans. on Circuits Syst. II, vol. 52, pp. 398–402,

July 2005.

[14] A. Soto, P. Alou, and J.A. Cobos, “Nonlinear digital control breaks bandwidth limitations,”

in Proc. IEEE Applied Power Electronics Conf., 2006, pp. 724–730.

[15] Santa C. Huerta, P. Alou, J. A. Olivier, O. Garcia, J. A. Cobos, and A.Abou-Alfotouh, “A

very fast control based on hysteresis of the cout current with a frequency loop to operate at

constant frequency,” in Proc. IEEE Applied Power Electronics Conf., 2009, pp. 799–805.

[16] G. Feng, E. Meyer, and Y.-F. Liu, “A new digital control algorithm to achieve optimal

dynamic performance in DC-to-DC converters,” IEEE Trans. Power Electron., vol. 22, pp.

1489–1498, July 2007.

[17] Z. Zhao, A. Prodic, “Continuous-time digital controller for high-frequency DC-DC

converters,” IEEE Trans. on Power Electron., vol. 23, pp. 564–573, Mar. 2008.

[18] E. Meyer, Zhiliang Zhang, and Y.-F. Liu, “An optimal control method for buck converters

using a practical capacitor charge balance technique,” IEEE Trans. Power Electron., vol. 23, pp.

1802–1812, July 2008.

28

[19] V. Yousefzadeh, A. Babazadeh, B. Ramachandran, E. Alarcon, L. Pao, and D. Maksimovic,

“Proximate time-optimal digital control for synchronous buck DC-DC converters,” IEEE Trans.

Power Electron., vol. 23, pp. 2018–2026, July 2008.

[20] A. Costabeber, L. Corradini, P. Mattavelli, and S. Saggini, “Time optimal, parameters-

insensitive digital controller for DC-DC buck converters,” in Proc. IEEE Power Electronics

Specialist Conf., 2008, pp. 1243–1249.

[21] A. Radić, Z. Lukić, A. Prodić, and R. de Nie, “Minimum deviation digital controller IC for

single and two phase DC-DC switch-mode power supplies,” in Proc. IEEE Applied Power

Electronics Conf., 2010, pp. 1–6. Feb. 2010.

[22] B. Mahdavikhah, M. Peretz, A. Prodic, "Low-volume power supply for vehicular fuel

injection systems," IECON 2012 - 38th Annual Conference on IEEE Industrial Electronics

Society , vol., no., pp.531,536, 25-28 Oct. 2012.

[23] M. Pertez, B. Mahdavikhah, A.Prodic,” Hardware-Efficient Programmable-Deviation

Controller for

Indirect Energy Transfer Dc-Dc Converters, ” IEEE Tran. Power Electron., In press.

[24] H. Qingcong, and R. Zane, “Minimizing required energy storage in off-line LED driver

based on series-input converter modules,” IEEE Trans. Power Electron., vol.26, no.10, pp.2887-

2895, Oct. 2011.

[25] S.M. Ahsanuzzaman, T. McRae, B. Mahsavikhah, and A. Prodic, “Programmable output

PFC rectifier with dynamic efficiency and transient response optimization,” in Proc. IEEE

Applied Power Electronics Conference and Exposition, APEC-2012, pp. 285-290.

[26] J. Zhang, M. M. Jovanovic, and F. C. Lee. "Comparison between CCM single-stage and

two-stage boost converter," in Proc. IEEE Applied Power Electronics Conference, APEC-1999,

pp. 335-341.

[27] K.W. Lee, Y.H. Hsieh, and T.J. Liang, “ A current ripple cancellation circuit for electrolytic

capacitor-less ac-dc LED driver,” in Proc. IEEE Applied Power Electronics Conference, APEC-

2013, pp. 1058- 1061.

[28] R. Wang, F. Wang, D. Boroyevich, R. Burgos, R. Lai, P. Ning, and K. Rajashekara, “ A

high power density single-phase PWM recitifier with active ripple energy storage,” IEEE Trans.

Power Electron., vol.26, no.5, pp. 1430-1443, May 2011.

[29] S. Harb, and R.S. Balog, “Single-phase PWM rectifier with power deocoupling ripple-port

for double-line-frequency ripple cancellation,” in Proc. IEEE Applied Power Electronics

Conference, APEC-2013, pp. 1025- 1029.

[30] P.T. Krein, and R.S. Balog, “ Cost-effective hundred-year life for single-phase interters and

rectifiers in Solar and LED lighting applications based on minimum capacitance requirements

29

and a ripple power port,” in Proc. IEEE Applied Power Electronics Conference, APEC-2009, pp.

620-625.

[31] A. C. Kyritsis, N. P. Papanicolaou, and E. C. Tatakis, "A novel parallel active filter for

current pulsation smoothing on single stage grid-connected ac-pv modules," in Proc. European

conference on Power Electronics and Applications, pp. 1-10, EPE-2007

[32] B. Mahdavikhah, S.M. Ahsanuzzaman, A. Prodic, "A hardware-efficient programmable

two-band controller for PFC rectifiers with ripple cancellation circuits," In Proc. IEEE IECON,

pp.3240-3245, Nov 2013.

[33] C.P. Henze, H. Martin, D.W. Parsley, "Zero-voltage switching in high frequency power

converters using pulse width modulation," In Proc. IEEE APEC 1988, Feb 1988.

[34] Wittenbreder, E.H., "A simple clamped ZVS PWM converter," In Proc. IEEE APEC 1993,

pp.715-721, Mar 1993.

[35] J. Zhang; J. Lai; R. Kim; W. Yu, "High-Power Density Design of a Soft-Switching High-