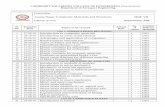

generalised substitution box

description

Transcript of generalised substitution box